lr3

.docxФЕДЕРАЛЬНОЕ АГЕНТСТВО СВЯЗИ

Федеральное государственное бюджетное образовательное

учреждение высшего образования

«Санкт-Петербургский государственный университет телекоммуникаций

им. проф. М. А. Бонч-Бруевича»

___________________________________________________________________________

Кафедра программной инженерии и вычислительной техники.

Дисциплина «Микропроцессорные устройства»

Лабораторная работа № 3

Исследование работы ПЦУ

Выполнили: ст. гр.

Проверил: ст.пр. Неелова О.Л.

_____________________

Санкт-Петербург

2024

Программа 3.1 Асинхронный RS-триггер:

module tr_rs

(input wire s,r, output wire q,nq);

wire p,np; assign p = !(s & np);

assign np = !(r & p);

assign q=p;

assign nq=np;

endmodule

Testbench:

`timescale 1ns/100ps

module biba_rs_tb;

logic s,r;

logic q,nq;

biba_rs uut_biba_rs (.s(s), .r(r), .q(q), .nq(nq));

initial

begin

s=1'b0;

r=1'b1;

#100;

s=1'b0;

r=1'b0;

#100;

s=1'b1;

r=1'b0;

#100;

s=1'b1;

r=1'b1;

#100;

s=1'b0;

r=1'b1;

#100;

end

endmodule

Рис.1 Симуляция асинхронного RS-триггера

Программа 3.2 D-триггер

module biba_tr_d

(input wire clk,d,set,res,

output wire q);

reg p;

assign q=p;

always@ (negedge set, negedge res, posedge clk)

begin

if (!set)

p<=1'b1;

else if (!res)

p<=1'b0;

else if(clk)

p<=d;

end

endmodule

Testbench:

`timescale 1ns/100ps

module biba_tr_d_tb;

logic clk,d,set,res;

logic q;

biba_tr_d uut_biba_tr_d (.clk(clk), .d(d), .set(set), .res(res), .q(q));

initial begin

clk=1'b0;

set=1'b0;

res=1'b1;

d=1'b0;

forever begin

#5 clk=~clk;

end

end

initial begin

#10

res=1'b0;

set=1'b1;

d=1'b1;

#10

res=1'b1;

d=1'b1;

#10

d=1'b0;

#10

d=1'b1;

#10

$stop;

end

endmodule

Рис.2 Симуляция D-триггера

Программа 3.3 JK-Триггер

module tr_jk

(input wire clk, set, res, j, k,

output wire q);

reg p;

assign q=p;

always@ (negedge set, negedge res, posedge clk)

begin

if (!set)

p<=1'b1;

else if (!res)

p<=1'b0;

else if (clk)

case ({j,k})

2'b00: begin p<=p; end

2'b01: begin p<=1'b0; end

2'b10: begin p<=1'b1; end

2'b11: begin p<=!p; end

endcase

end

endmodule

Testbench:

`timescale 1ns/100ps

module biba_tr_jk_tb;

logic clk,set,res,j,k;

logic q;

biba_tr_jk uut_biba_tr_jk (.clk(clk), .set(set), .res(res), .j(j), .k(k), .q(q));

initial begin

clk=1'b0;

set=1'b0;

res=1'b1;

j=1'b0;

k=1'b0;

forever begin

#5 clk=~clk;

end

end

initial begin

#10

res=1'b0;

set=1'b1;

j=1'b0;

k=1'b0;

#10

res=1'b1;

j=1'b0;

k=1'b0;

#10

j=1'b1;

k=1'b1;

#10

j=1'b0;

k=1'b1;

#10

j=1'b1;

k=1'b0;

$stop;

end

endmodule

Рис.3 Симуляция JK-триггера

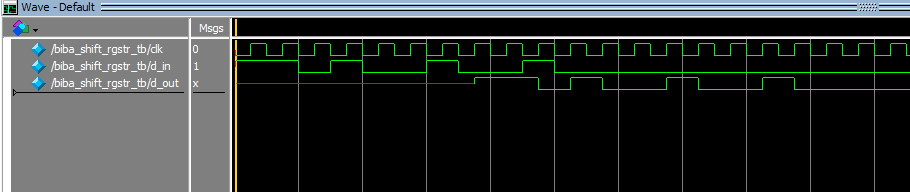

Программа 3.4 Последовательный регистр

module biba_shift_rgstr

#(parameter N=8)

( input clk,

input d_in,

output d_out);

reg [N-1:0] d;

assign d_out = d[N-1];

always @ (posedge clk)

begin

d[N-1:1] <= d[N-2:0];

d[0] <= d_in;

end

endmodule

Testbench:

`timescale 1ns/100ps

module biba_shift_rgstr_tb;

logic clk;

logic d_in;

logic d_out;

biba_shift_rgstr uut_biba_shift_rgstr (.clk(clk), .d_in(d_in), .d_out(d_out));

initial begin

clk=1'b0;

d_in=1'b1;

forever begin

#5 clk=~clk;

end

end

initial begin

#10

d_in=1'b1;

#10

d_in=1'b0;

#10

d_in=1'b1;

#10

d_in=1'b0;

#10

d_in=1'b0;

#10

d_in=1'b1;

#10

d_in=1'b0;

#10

d_in=1'b0;

#10

d_in=1'b1;

#10

d_in=1'b0;

#10

d_in=1'b0;

end

endmodule

Рис.4 Симуляция последовательного регистра

Программа 3.5 Регистр-защелка

module biba_latch_rgstr

#(parameter N=4)

(input [N-1:0] d_in,

input clk,

output [N-1:0]d_out);

reg [N-1:0]q;

assign d_out=q;

always@ (posedge clk)

begin

q<=d_in;

end

endmodule

Testbench:

`timescale 1ns/100ps

module biba_latch_rgstr_tb;

logic clk;

logic [3:0] d_in;

logic [3:0] d_out;

biba_latch_rgstr uut_biba_latch_rgstr (.clk(clk), .d_in(d_in), .d_out(d_out));

initial begin

clk=1'b0;

d_in=4'b1;

forever begin

#5 clk=~clk;

end

end

initial begin

#10

d_in=4'b1000;

#10

d_in=4'b0000;

#10

d_in=4'b0100;

#10

d_in=4'b0010;

#10

end

endmodule

Рис. 5 Симуляция регистра-защелки

Программа 3.6 Параллельный буферный регистр

module biba_buf_rgstr

#(parameter N=4)

(input [N-1:0] d_in,

input clk, ena, res, rd,

output [N-1:0] d_out);

reg [N-1:0]w;

assign d_out=(rd)? (w) : (0);

always@ (posedge clk, negedge res)

begin

if (!res)

w<=0;

else if (clk)

begin

if (ena)

w<=d_in;

else

w<=w;

end

end

endmodule

Testbench:

`timescale 1ns/100ps

module biba_buf_rgstr_tb;

logic clk,ena,res,rd;

logic [3:0] d_in;

logic [3:0] d_out;

biba_buf_rgstr uut_biba_buf_rgstr (.clk(clk), .ena(ena), .res(res), .rd(rd), .d_in(d_in), .d_out(d_out));

initial begin

clk=1'b0;

d_in=4'd5;

ena=1'b0;

rd=1'b0;

res=1'b0;

#5

res=1'b1;

forever begin

#10 clk=~clk;

end

end

initial begin

#20

d_in=4'd5;

ena=1'b0;

rd=1'b0;

res=1'b1;

#20

d_in=4'd9;

ena=1'b1;

#20

d_in=4'd7;

ena=1'b0;

rd=1'b1;

#20

d_in=4'd0;

#20

d_in=4'd2;

rd=1'b0;

end

endmodule

Рис.6 Симуляция параллельного буферного регистра