- •Отчет по лабораторной работе

- •1. Ознакомление с работой программы icBuilder.

- •2. Исследование логического вентиля

- •2.2. Продемонстрировать преподавателю работу данной схемы.

- •3. Построение заданных булевых функций

- •4. Построение управляемого инвертора

- •5. Проверка функционирования логических элементов 2и в условиях динамически меняющихся входных воздействий

- •6. Изучение работы триггеров

- •6.1. Синтез rs-триггера на базе логических вентилей и – не

- •6.2. Построение d-триггера на базе логических элементов

- •6.3. Построение d-триггера на базе логических элементов с учётом сигналов принудительной установки и сброса

- •6.4. Изучение схемы включения сдвоенного d-триггера на базе микросхемы 1533тм2

- •6.5. Изучение работы т-триггера, построенного на базе d-триггера

- •6.6. Изучение работы jk-триггера на базе микросхемы 1531тв9

6. Изучение работы триггеров

6.1. Синтез rs-триггера на базе логических вентилей и – не

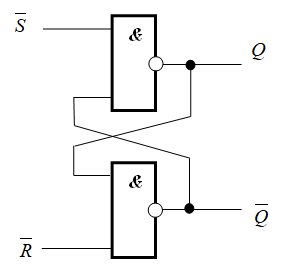

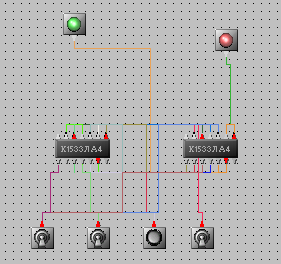

6.1. Используя логические вентили И-НЕ, построить схему, представленную на рис. 1.5.

Рис. 1.5. Схема RS-триггера. Скриншот схемы.

Заполнить таблицу 1.4.

|

|

Q |

|

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

Х |

Х |

6.2. Построение d-триггера на базе логических элементов

6.2.1. Используя логические вентили, собрать схему синхронного D-триггера, представленную на рис. 1.6. Составить таблицу истинности D-триггера, представленного на рис. 1.6.

Рис. 1.6. Схема синхронного D-триггера. Скриншот схемы.

Заполнить таблицу 1.5.

D |

C |

Q |

|

0 0 1 1 |

0 1 0 1 |

X 0 X 1 |

X 1 X 0 |

Проверить правильность составленной таблицы истинности. При проверке использовать все последовательные комбинации входных сигналов.

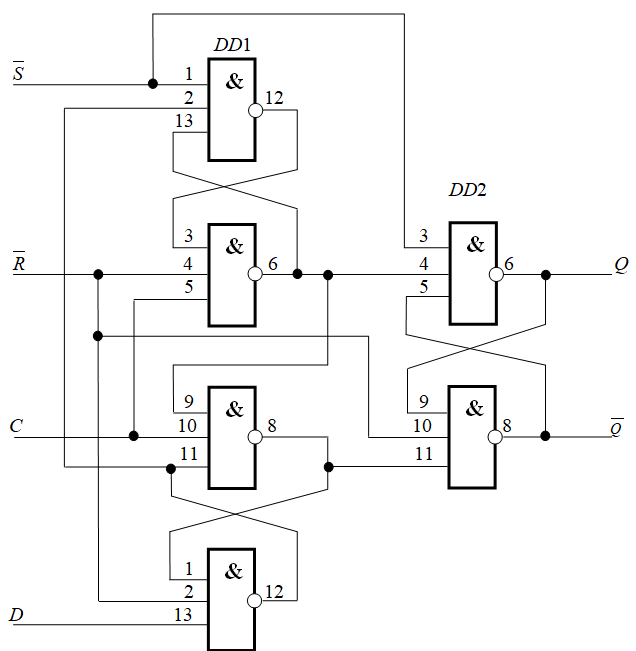

6.3. Построение d-триггера на базе логических элементов с учётом сигналов принудительной установки и сброса

6.3.1. Ввести дополнительные сигналы принудительной установки (S) и принудительного сброса (R) D-триггера. С учётом введённых сигналов построить схему (рис. 1.7):

Скриншот схемы.

Рис. 1.7. Схема D-триггера с сигналами принудительной установки и сброса.

6.3.2. На основании собранной схемы составить таблицу истинности (табл. 1.6.) и убедиться в работоспособности устройства. Пояснить полученные результаты.

Таблица 1.6.

|

|

|

D |

C |

Q |

|

0. |

0 |

0 |

0 |

0 |

1 |

1 |

1. |

0 |

0 |

0 |

1 |

1 |

1 |

2. |

0 |

0 |

1 |

0 |

1 |

1 |

3. |

0 |

0 |

1 |

1 |

1 |

1 |

4. |

0 |

1 |

0 |

0 |

1 |

0 |

5. |

0 |

1 |

0 |

1 |

1 |

0 |

6. |

0 |

1 |

1 |

0 |

1 |

0 |

7. |

0 |

1 |

1 |

1 |

1 |

0 |

8. |

1 |

0 |

0 |

0 |

0 |

1 |

9. |

1 |

0 |

0 |

1 |

0 |

1 |

10. |

1 |

0 |

1 |

0 |

0 |

1 |

11 |

1 |

0 |

1 |

1 |

0 |

1 |

12 |

1 |

1 |

0 |

0 |

x |

x |

13 |

1 |

1 |

0 |

1 |

x |

x |

14 |

1 |

1 |

1 |

0 |

x |

x |

15 |

1 |

1 |

1 |

1 |

x |

x |