СхТ_ЛР_2_Цуканова_0363

.docxМИНОБРНАУКИ РОССИИ

САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ

ЭЛЕКТРОТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

«ЛЭТИ» ИМ. В.И. УЛЬЯНОВА (ЛЕНИНА)

Кафедра САПР

ОТЧЕТ

по лабораторной работе №2

по дисциплине «Схемотехника»

Тема: Мультиплексор и демультиплексор

Студент гр. 0363 |

__________________________ |

Цуканова П.А. |

Преподаватель |

__________________________ |

Фахми Ш. С. |

Санкт-Петербург

2021

ЛАБОРАТОРНАЯ РАБОТА 2. МУЛЬТИПЛЕКСОР И ДЕМУЛЬТИПЛЕКСОР

Цель работы

Спроектировать в среде разработки мультиплексор и демультиплексор, проверить их работоспособность.

Техническое задание

Мультиплексор – логическая

схема, имеющая

входов

входов

и один выход

и один выход

,

на который подаётся значение на входе

,

на который подаётся значение на входе

,

где

,

где

— число, которое кодируется входами

— число, которое кодируется входами

.

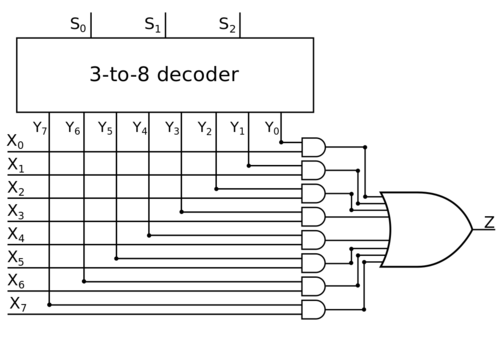

Схема показана на рис. 1.

.

Схема показана на рис. 1.

Рисунок 1 - Схема мультиплексора

Демультиплексор – логическая схема,

имеющая

входов

,

входов

,

и

и

выходов

выходов

.

На все выходы подаётся 0 кроме выхода

.

На все выходы подаётся 0 кроме выхода

,

на который подаётся значение на входе

,

где

— число, которое кодируется входами

.

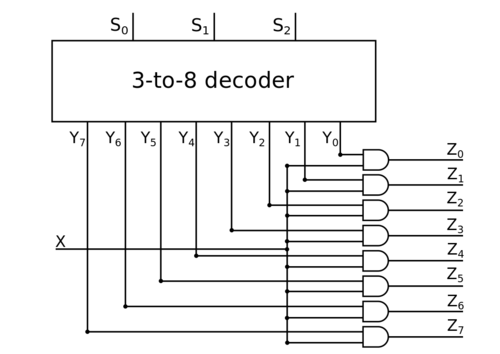

Схема показана на рис. 2.

,

на который подаётся значение на входе

,

где

— число, которое кодируется входами

.

Схема показана на рис. 2.

Рисунок 2 - Схема демультиплексора

Теоретическая подготовка

Описание схемы мультиплексора:

Входные сигналы

;

;Выходные сигналы: .

Работа модуля:

Описание схемы демультиплексора:

Входные сигналы ;

Выходные сигналы: .

Работа модуля:

Код программы:

Мультиплексор:

`timescale 1ns / 1ps

module counter (

out ,

up_down ,

clk ,

reset

);

output [7:0] out;

input up_down, clk, reset;

reg [7:0] out;

always @(posedge clk)

if (reset) begin

out <= 8'b0 ;

end

else if (up_down) begin

out <= out + 1;

end

else begin

out <= out - 1;

end

endmodule

Демультиплексор:

`timescale 1ns / 1ps

module dmul (En, X1, X2, X3, X4, X5, X6, X7, X8, Y, Z);

input En;

input Z;

input wire[2:0]Y;

output reg X1, X2, X3, X4, X5, X6, X7, X8;

always @(Z or Y or En)

begin

X1 <= (Z & !Y[0] & !Y[1] & !Y[2]) & En;

X2 <= (Z & Y[0] & !Y[1] & !Y[2]) & En;

X3 <= (Z & !Y[0] & Y[1] & !Y[2]) & En;

X4 <= (Z & Y[0] & Y[1] & !Y[2]) & En;

X5 <= (Z & !Y[0] & !Y[1] & Y[2]) & En;

X6 <= (Z & Y[0] & !Y[1] & Y[2]) & En;

X7 <= (Z & !Y[0] & Y[1] & Y[2]) & En;

X8 <= (Z & Y[0] & Y[1] & Y[2]) & En;

end

endmodule

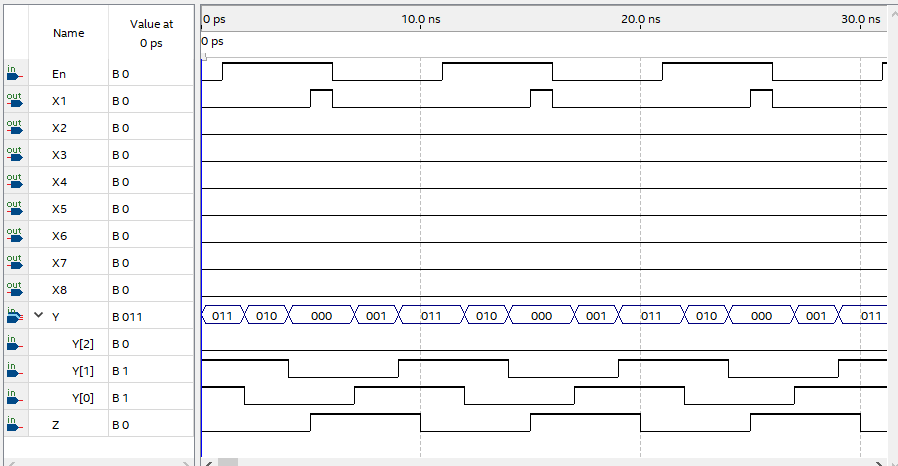

Временная диаграмма реализации схемы

Мультиплексор:

Демультиплексор:

Вывод

В результате выполнения лабораторной работы мы спроектировали мультиплексор и димультиплексор в среде Quartus и проверили их работоспособность.