СхТ_ЛР_1_Цуканова_0363

.docxМИНОБРНАУКИ РОССИИ

САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ

ЭЛЕКТРОТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

«ЛЭТИ» ИМ. В.И. УЛЬЯНОВА (ЛЕНИНА)

Кафедра САПР

ОТЧЕТ

по лабораторной работе №1

по дисциплине «Схемотехника»

Тема: Счетчик

Студент гр. 0363 |

__________________________ |

Цуканова П.А. |

Преподаватель |

__________________________ |

Фахми Ш. С. |

Санкт-Петербург

2021

ЛАБОРАТОРНАЯ РАБОТА 1. СЧЕТЧИК

Цель работы

Спроектировать в среде разработки счетчик и проверить его работоспособность.

Техническое задание

Счётчик – автомат последовательностного типа, предназначенный для счёта поступающих на его входы импульсов и фиксирующий это число в каком-либо коде. Если число различных комбинаций выходных переменных, определяющих состояние схемы, равно n, то с помощью счетчика можно считать число импульсов в диапазоне от 0 до (n −1) . Количество различных состояний схемы определяет модуль счета.

Счетчик состоит из последовательно соединённых ячеек - триггеров, работающих в счетном режиме. Каждая ячейка называется разрядом.

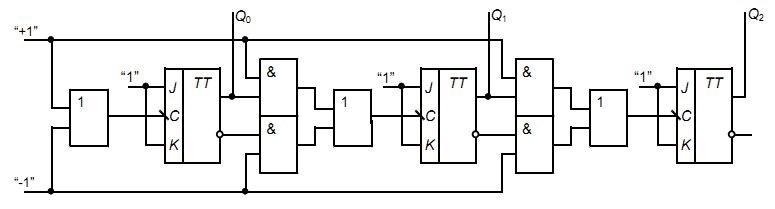

Синхронный счетчик - счетчик, в котором триггеры переходят в новые состояния одновременно. Счетчик с входами прямого и обратного счета (up-down) может работать и как суммирующий, и как вычитающий, но он имеет два входа для импульсов. Импульс, поступающий на вход прямого счета, увеличивает число, представленное выходным кодом, импульс на входе обратного счета - уменьшает. Схема такого счетчика показана на рис. 1.

Рисунок 1 - Схема счетчика

Теоретическая подготовка

Описание схемы счетчика:

Входные сигналы clk, reset, up-down;

Выходные сигналы counter0, counter1, counter2, counter3.

Работа модуля:

Количество импульсов на входе clk |

out0 |

out1 |

out2 |

out3 |

out4 |

out5 |

out6 |

out7 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

2 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

3 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

4 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

… |

||||||||

252 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

253 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

254 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

255 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

Код программы:

`timescale 1ns / 1ps

module counter (

out ,

up_down ,

clk ,

reset

);

output [7:0] out;

input up_down, clk, reset;

reg [7:0] out;

always @(posedge clk)

if (reset) begin

out <= 8'b0 ;

end

else if (up_down) begin

out <= out + 1;

end

else begin

out <= out - 1;

end

endmodule

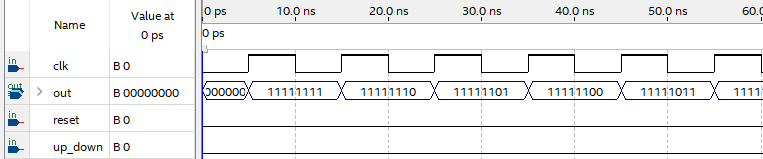

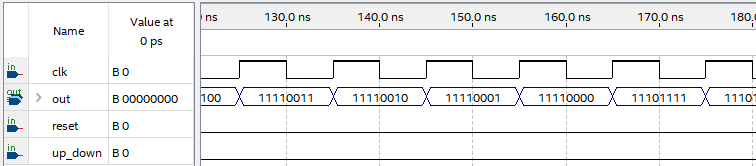

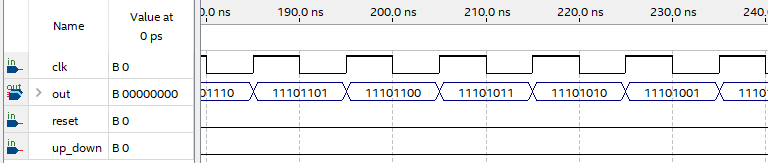

Временная диаграмма реализации схемы

Вывод

В результате выполнения лабораторной работы мы спроектировали счетчик в среде Quartus и проверили его работоспособность на плате.