- •2. Арифметико-логические устройства. Определение, структура, подход к проектированию, основные уравнения работы алу (пример синтеза выражения). Особенности знаковой и беззнаковой арифметики.

- •4. Особенности представления чисел в форматах с фиксированной и плавающей запятой. Особенности аппаратной реализации арифметических операций над числами в форматах с фиксированной и плавающей запятой.

- •5. Архитектура системы команд. Система команд и способы адресации операндов. Классификация архитектур по сложности кодирования инструкций (risc, cisc). Уровни абстракции представления микропроцессора.

- •7. Процессоры с однотактным, многотактным и конвейеризированным устройствами управления. Особенности построения. Достоинства и недостатки каждой из реализаций.

- •9.Подход к проектированию однотактного процессора на примере архитектуры risc-V. Сравнение с другими подходами к реализации микроархитектуры.

- •10.Подход к проектированию многотактного процессора на примере архитектуры risc-V. Сравнение с другими подходами к реализации микроархитектуры.

- •11. Подход к проектированию конвейерного процессора на примере архитектуры risc-V. Сравнение с другими подходами к реализации микроархитектуры.

- •12. Структурные конфликты и способы их минимизации. Конфликты по данным, их классификация и примеры реализаций механизмов их обходов.

- •13. Сокращение потерь на выполнение команд перехода и методы минимизации конфликтов по управлению.

- •14. Методы повышения производительности процессоров: суперскалярность, суперконвейерность, гипертрейдинг, внеочередное исполнение команд, переименовывание регистров и т.П.

- •Суперскалярность

- •Внеочередное выполнение команд

- •Переименовывание регистров

- •16. Иерархия памяти: причины, зависимости, следствия. Статическое и динамическое озу. Организация систем памяти в микропроцессорных системах.

- •17. Принципы организации кэш-памяти. Способы отображения данных из озу в кэш-память. Варианты построения.

- •18. Виртуальная память. Принципы функционирования и способы организации виртуальной памяти. Tlb.

- •19. Когерентность кэш. Примеры реализации когерентности кэш-памяти: VI, msi, mesi.

- •19.1 Параллелизм уровня потоков

- •19.2 Синхронизация

- •19.3 Потоково-безопасное программирование

- •19.4 Синхронная связь

- •Мультиядерность

- •Когерентность кэш л18 47:24

- •Поддержка когерентности

- •Реализация когерентности

- •Оптимизация msi: e-Состояние (Exclusive)

- •21. Механизм граничного сканирования регистров. Jtag. Области применения.

- •22. Обмен информацией между элементами в микропроцессорных системах. Организация шинного обмена. Виды и иерархии шин.

- •Иерархияшин

- •Вычислительная машина с двумя видами шин

- •Вычислительная машина с тремя видами шин

- •23. Арбитр магистрали. Алгоритмы и схемы арбитража. Методы повышения эффективности шин.

- •Отдельная шина системы ввода-вывода

- •Модули ввода-вывода

- •Конфигурации пдп(dma)

- •27. Микроконтроллеры. Определение, виды, характеристики, особенности построения и применения.

- •29.Классификации архитектур параллельных вычислительных систем: Флинна, по способу организации памяти. Нетрадиционные вычислители.

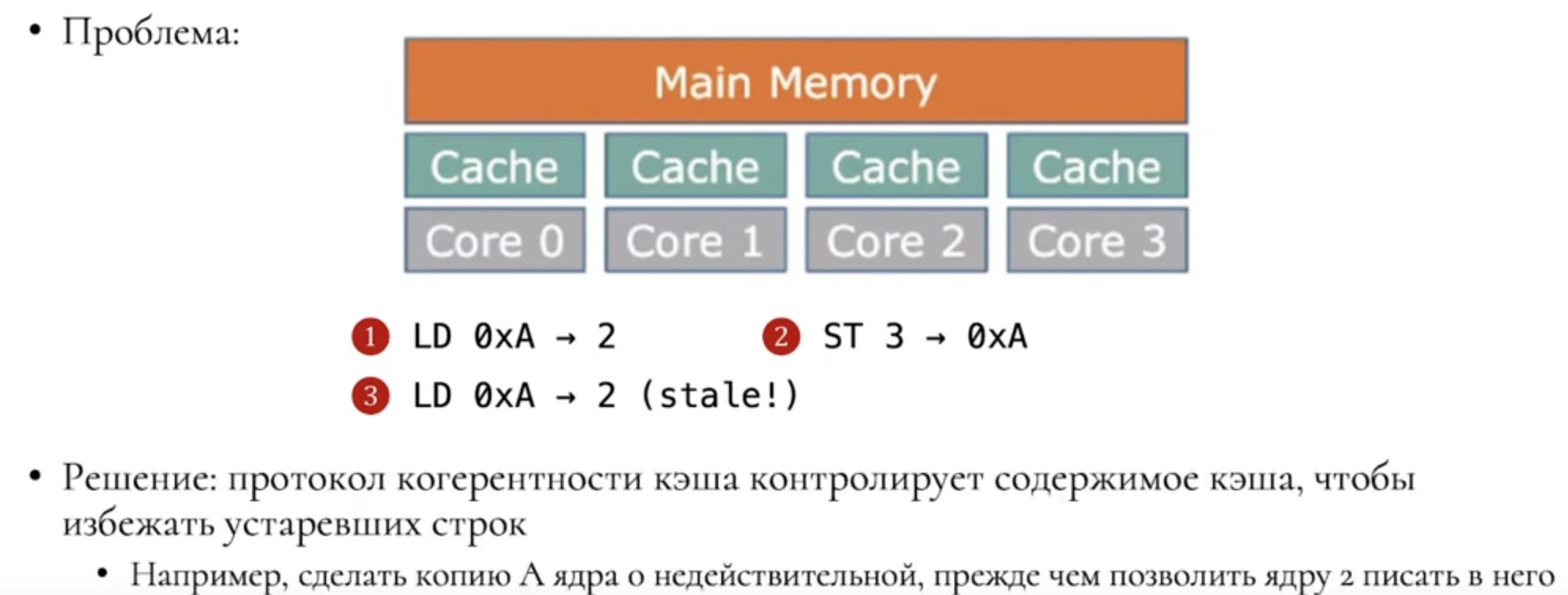

19. Когерентность кэш. Примеры реализации когерентности кэш-памяти: VI, msi, mesi.

Когерентность кэш: В многопроцессорной системе у каждого процессора существует свой собственный кэш. Все кэш-памяти работают с одной общей памятью.

Когерентность кэш - синхронизация актуальных данных во всех кэш-памятях.

19.1 Параллелизм уровня потоков

Поток - неделимая в плане распараллеливания часть выполняемой программы (процесса).

Разделение вычислений между несколькими исполнительными потоками

несколько независимых последовательных потоков, которые конкурируют за общие ресурсы (память, устройства ввода/вывода).

○ Несколько последовательных потоков, которые взаимодействуют друг с другом.

Коммуникационная модель.

Общая память (Shared Memory).

■ Единое адресное пространство.

■ Неявная связь с помощью загрузки и сохранения в память.

○ Обмен сообщениями (Message Passing).

■ Раздельное адресное пространство.

■ Явная связь путем отправки и получения сообщений.

19.2 Синхронизация

● Необходимость в синхронизации возникает каждый раз, когда в системе существуют параллельные процессы.

○ Вилки и соединения (Fork and Join): параллельный процесс может подождать, пока не произойдет несколько событий

(Выполнение далее не

произойдет, пока оба

(Выполнение далее не

произойдет, пока оба

процесса P1 и P2 не завершатся. Их необходимо синхронизировать).

○ Производитель и потребитель (Producer-Consumer): потребительский процесс должен ждать, пока процесс производителя не произведет данные

(Потребитель не может

быть запущен раньше

(Потребитель не может

быть запущен раньше

чем производитель произведет данные).

○ Взаимное исключение: ОС должна гарантировать, что ресурс используется только одним процессом в данный момент времени.

19.3 Потоково-безопасное программирование

Многопоточные программы могут выполняться на одном процессоре с помощью таймшеринга.

Каждый поток выполняется некоторое время (Прерывание по таймеру), а затем ОС переключается на другой поток.

Потоково-безопасные многопоточные программы ведут себя одинаково вне зависимости от того, выполняются и они на нескольких процессорах или на одном процессоре.

Мы будем предполагать, что каждый поток имеет свой собственный процессор для запуска.

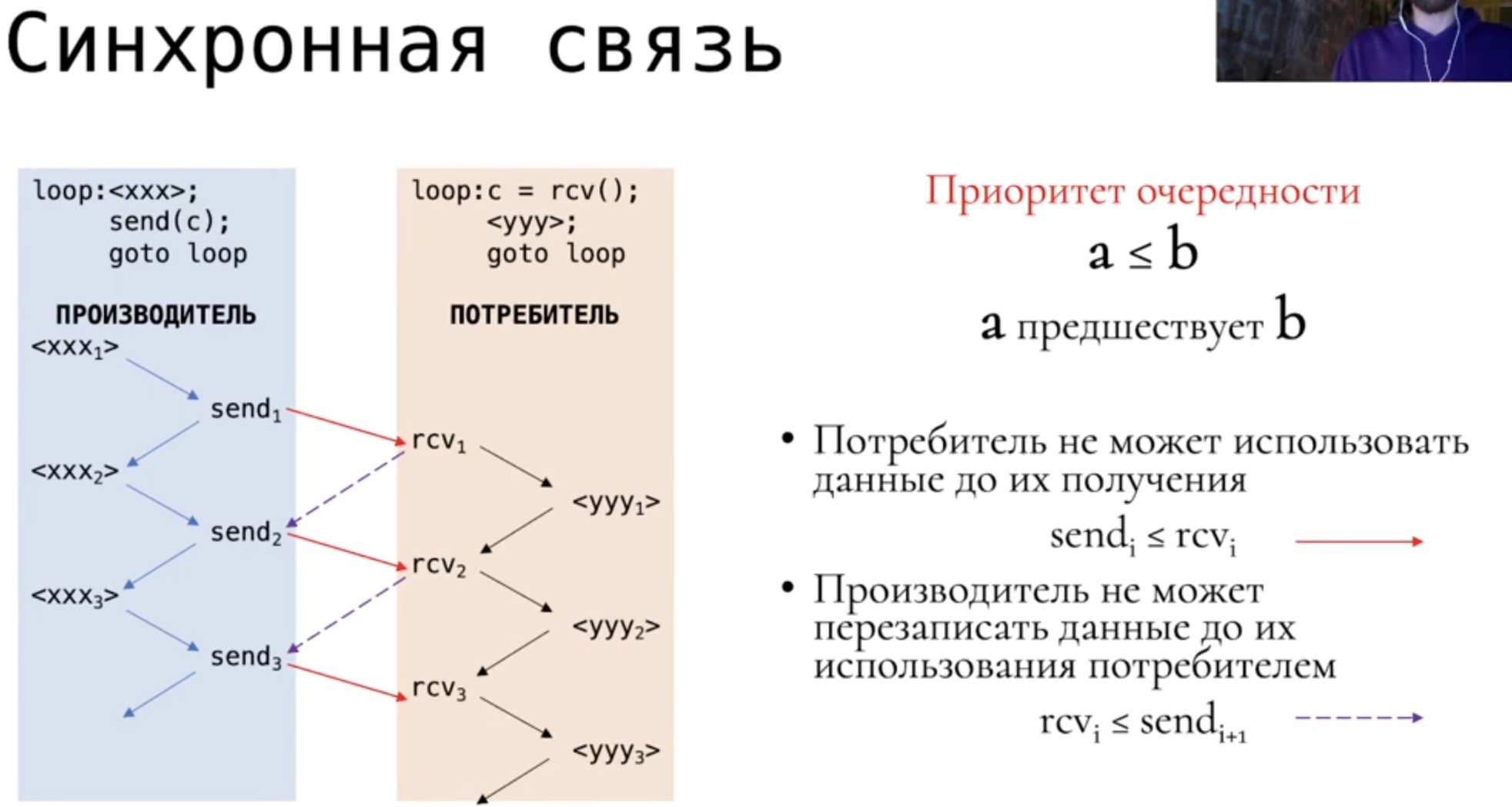

19.4 Синхронная связь

Решения:

Буфер FIFO

Буфер FIFO ослабляет ограничения, связанные с синхронизацией. Производитель может опередить потребителя на N значений. (N - глубина буфера).

Мультиядерность

Каждое ядро имеет свой program counter и может выполнять разные участки программы.

Современные процессоры обычно имеют от 2 до 8 ядер, где каждое ядро имеет собственный кэш для повышения производительности

Ядра могут использоваться совместно для ускорения работы приложения. (Использование многопоточности).

Ядра взаимодействуют друг с другом через память. (За их синхронизацию отвечают, допустим, семафоры)

Когерентность кэш л18 47:24

Когерентность кэша — свойства кэш-памяти, означающее целостность данных, хранящихся в локальных кэшах, разделяемой системы.

Каждая ячейка кэша имеет флаги, описывающие, как ее состояние соотносится с состоянием ячейки с таким же адресом в других процессорах системы.

Необходимо создать иллюзию единой общей памяти, даже если многоядерные системы имеют несколько приватных(собственных) кэшей.

Информация в приватных кэшах обновляется ядрами и эта обновленная информация должна быть доступна всем другим кэшам, которые собираются использовать эту информацию.