ЛР / Основы разработки систем на кристалле (метода)

.pdf

5. Экспорт конфигурационных файлов в Xilinx SDK.

5.1.Нажмите File → Export → Export Hardware.

5.2.В появившемся окне установите галочку напротив Include Bitstream, нажмите ОK. Данное действие автоматически вложит файл Bitstream в архив обертки для данного проекта.

5.3.Найдите в папке проекта директорию с названием имя проекта.sdk

иоткройте ее.

5.4.Проконтролируйте наличие файла-архива с разрешением HDF. Зафиксируйте роль данного архива в протокол.

5.5.Нажмите File →Launch SDK, затем в появившемся окне – ОK. Дождитесь запуска среды Xilinx SDK.

5.6.Нажмите File → New → Board Support Package. Убедитесь, что выбран пункт Standalone, нажмите ОK. Данное действие собрало пакет поддержки платы, подтянув необходимые файлы. Зафиксируйте роль Board Support Package для сборки проекта в протокол.

6. Создание приложения.

6.1.Нажмите File → New → Application Project. В открывшемся окне введите имя приложения (EMIO) и установите переключатель Board Support Package в положение Use existing. Нажмите Next.

6.2.В списке предлагаемых шаблонов приложения выберите Empty, нажмите Finish. На данном этапе создан пустой проект приложения.

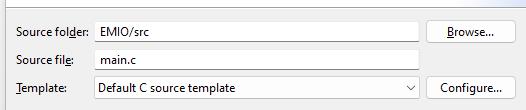

6.3.Нажмите правой кнопкой мыши на папке src проекта в дереве

Project Explorer (рис. 24) и выберите пункт меню New → Source File.

Рис. 24. Добавление файла в проект

20

6.4. В появившемся окне введите имя файла main.c (рис. 25), нажмите

Finish.

Рис. 25. Ввод названия и типа файла, добавляемого в проект

6.5. Введите программу в файл main.c согласно листингу:

#include "xgpiops.h" #include "sleep.h"

int main()

{

static XGpioPs psGpioInstancePtr; XGpioPs_Config* GpioConfigPtr; int xStatus;

GpioConfigPtr = XGpioPs_LookupConfig(XPAR_PS7_GPIO_0_DEVICE_ID);

xStatus = XGpioPs_CfgInitialize(&psGpioInstancePtr,GpioConfigPtr, GpioConfigPtr- >BaseAddr);

if(XST_SUCCESS != xStatus)

print(" PS GPIO INIT FAILED \n\r");

//EMIO is configured as output XGpioPs_SetDirectionPin(&psGpioInstancePtr, 54,1);

// Enable EMIO output XGpioPs_SetOutputEnablePin(&psGpioInstancePtr, 54,1);

//MIO is configured and enable XGpioPs_SetDirectionPin(&psGpioInstancePtr, 7, 1); XGpioPs_SetOutputEnablePin(&psGpioInstancePtr, 7, 1);

while(1) {

XGpioPs_WritePin(&psGpioInstancePtr, 54, 1); usleep(200000); //delay XGpioPs_WritePin(&psGpioInstancePtr, 54, 0); usleep(200000); //delay

XGpioPs_WritePin(&psGpioInstancePtr, 7, 1); usleep(200000); //delay XGpioPs_WritePin(&psGpioInstancePtr, 7, 0);

21

usleep(200000);

}

return 0;

}

Примечание. Обратите внимание, что начальное значение битов EMIO начинается с фиксированным смещением – со значения 54. А бит MIO, подключенный к процессорной подсистеме напрямую, имеет значение 7, что отражено маркировкой на отладочной плате: MIO7 (LD9). Отметьте причину такого смещения в протокол.

Функция XGpioPs_SetDirectionPin устанавливает направление передачи информации. Если последний параметр равен 1 – линия настроена на вывод, а если равна 0 – на ввод.

Функция XGpioPs_WritePin устанавливает соответствующее значение сигнала в линии.

7. Проверка приложения на плате.

7.1.Убедитесь, что jtag-отладчик и UART от платы подключены

ккомпьютеру. Включите питание платы.

7.2.Нажмите правой кнопкой мыши на названии приложения, далее

ввыпадающих списках – Run As → Run Configuration.

7.3.В открывшемся окне нажмите Xilinx C/C++ application (GDB).

7.4.Настройте отладчик по примеру лабораторной работы 1.

7.5.Нажмите Save, а затем Run. Дождитесь компиляции проекта и прошивки платы.

7.6.Нажмите Tools→ Programm FPGA.

Примечание. Обратите внимание, что красный светодиод LD0 начал мигать только после выполнения данного пункта. Такое поведение объясняется тем, что светодиод подключен к плисовой части системы на кристалле и начинает работать только после прошивки кристалла ПЛИС.

7.7.Сверьте ожидаемый результат работы программы с результатом

вконсоли и работы светодиодов на плате.

7.8.Измените программу согласно индивидуальному заданию.

Содержание отчета

1.Задача и цели лабораторной работы.

2.Чертеж блок-схемы проекта с отметками о назначении всех блоков.

3.Блок-схема алгоритма работы программы индивидуального задания.

4.Листинг исходного кода из индивидуального задания с поясняющими комментариями каждой строки.

5.Заметки из протокола.

22

Задание к лабораторной работе

Для выполнения самостоятельной работы создайте отдельное приложение внутри проекта: File → New → Application project. Впишите имя приложения и установите переключатель в положение Use Existing, указав на созданный ранее BSP.

1.Реализуйте одновременное мигание светодиодов LD0, LD2 и LD7

счастотой 5 с.

2.Реализуйте одновременное мигание светодиодов LD1, LD5 и LD4

счастотой 3 с.

3.Реализуйте одновременное мигание светодиодов LD2, LD4 и LD6

счастотой 1 с.

4.Реализуйте поочередное мигание светодиодов LD0, LD9 и LD3 с частотой 2 с.

5.Реализуйте поочередное мигание светодиодов LD4, LD5 и LD6 с частотой 4 с.

6.Реализуйте поочередное мигание светодиодов LD7, LD0 и LD9 с частотой 6 с.

7.Реализуйте поочередное загорание светодиодов LD0, LD2 и LD7

счастотой 1 с.

8.Реализуйте поочередное загорание светодиодов LD2, LD3 и LD4

счастотой 1 с.

9.Реализуйте поочередное загорание светодиодов LD3, LD4 и LD5

счастотой 2 с.

10.Реализуйте поочередное загорание светодиодов LD4, LD5 и LD6

счастотой 3 с.

11.Реализуйте поочередное загорание светодиодов LD9, LD6 и LD1

счастотой 1 с.

12.Реализуйте поочередное загорание светодиодов LD5, LD6 и LD9

счастотой 3 с.

23

Лабораторная работа 3

СОЗДАНИЕ ПРОЕКТА ПРОЦЕССОРНОЙ СИСТЕМЫ ДЛЯ РЕАЛИЗАЦИИ ЛОГИЧЕСКИХ ВЫРАЖЕНИЙ НА ПОРТАХ EMIO

Цель работы

Создание проекта с использованием IP интегратора. Использование

MIO (multiplexed I/O) и EMIO (extended multiplexed I/O) портов для реа-

лизации логических выражений. Проверка проекта на отладочной плате

ZedBoad.

Основные вопросы, изучаемые перед выполнением работы

1.Архитектура системы на кристалле Xilinx Zynq7000.

2.Структура лабораторного макета ZedBoard.

3.Логические операторы, построение комбинационных схем.

Содержание работы

1. Создать новую отдельную директорию для лабораторной работы по аналогии с лабораторной работой 1. Например, полный путь к директории для данной лабораторный работы:

D:/(Год)/(Фамилия) (группа)/soc-lab-3

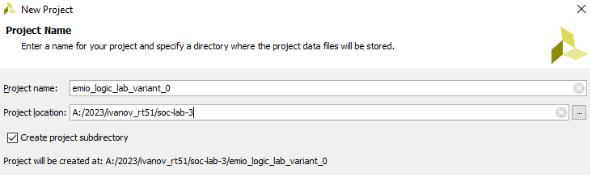

2. Создание проекта в Vivado 2016.4.

2.1. Создайте проект с именем emio logic_lab_variant_(номер вари-

анта) по аналогии с лабораторной работой 1 (рис. 26).

Рис. 26. Окно с примером создания проекта

2.2.Создайте Block Design и добавьте IP процессорной системы Zynq7 по аналогии с лабораторной работой 1.

2.3.Настройте процессорную систему согласно п. 4 лабораторной ра-

боты 1.

24

3. Конфигурация портов.

3.1. Нажмите Peripheral I/O Pins на панели Page Navigator. Активи-

руйте галочку напротив GPIO MIO и GPIO EMIO (рис. 27).

Рис. 27. Окно включения MIO и EMIO

3.2. Нажмите MIO Configuration на панели Page Navigator. Развер-

ните все пункты и активируйте галочку напротив GPIO MIO, установите разрядность GPIO EMIO в 16 бит (рис. 28).

Рис. 28. Окно конфигурирования EMIO

3.3.На данном этапе процессорная система сконфигурирована. Нажмите ОK для выхода из окна настройки блока Zynq7.

3.4.Нажмите правой кнопкой мыши на порт GPIO 0 блока Zynq7

ив выпадающем меню выберите пункт Make External.

3.5.Для проверки правильности конфигурации проекта нажмите Tools

→ Validate Design или клавишу F6. Если ошибок не обнаружено, то повторно сохраните проект. Зарисуйте блок-схему в протокол.

3.6. Итоговый вид блочного проекта показан на рис. 29.

25

Рис. 29. Итоговый вид проекта

снастроенной процессорной системой

3.7.Создайте HDL-wrapper, нажав правой кнопкой мыши на файл

срасширением Bd и выбрав пункт Create HDL-wrapper. Опции при создании обертки укажите по аналогии с лабораторной работой 1.

4. Синтез, настройка ограничений и размещение проекта.

4.1.Запустите синтез и размещение проекта на кристалле ПЛИС.

4.2.После того как процесс синтеза проекта завершится, в появившемся окне выберите пункт Open Synthesized Design, затем нажмите кнопку OK. Убедитесь, что никаких ошибок не появилось.

4.3.После того как окно Synthesis Design откроется, выберите на панели инструментов слой I/O Planing (рис. 30).

Рис. 30. Окно выбора слоя в Synthesized Design

4.4. Свяжите выходы модуля с выводами микросхемы, к которым подключены светодиоды. Для правильного задания параметров выводов микросхемы ПЛИС следует обратиться к документации по плате ZedBoard.

26

Необходим раздел, описывающий светодиоды (табл. 2) и переключатели (табл. 3).

|

Таблица 2 |

|

Соответствие сигналов светодиодов и контактов микросхемы |

||

|

|

|

Имя сигнала |

Пин кристалла Zynq7000 |

|

|

|

|

LD0 |

T22 |

|

|

|

|

LD1 |

T21 |

|

|

|

|

LD2 |

U22 |

|

|

|

|

LD3 |

U21 |

|

|

|

|

LD4 |

V22 |

|

|

|

|

LD5 |

W22 |

|

|

|

|

LD6 |

U19 |

|

|

|

|

LD7 |

U14 |

|

|

|

|

|

Таблица 3 |

|

Соответствие сигналов переключателей и контактов микросхемы |

||

|

|

|

Имя сигнала |

Пин кристалла Zynq7000 |

|

|

|

|

SW0 |

F22 |

|

|

|

|

SW1 |

G22 |

|

|

|

|

SW2 |

H22 |

|

|

|

|

SW3 |

F21 |

|

|

|

|

SW4 |

H19 |

|

|

|

|

SW5 |

H18 |

|

|

|

|

SW6 |

H17 |

|

|

|

|

SW7 |

M15 |

|

|

|

|

ZedBoard имеет восемь пользовательских светодиодов LD0–LD7 и восемь скользящих переключателей SW0–SW7. Светодиоды подключены к выводам микросхемы ПЛИС с напряжением питания +3,3 В, а переключатели – +2,5 В.

4.5.Выберите вкладку I/O Ports для того, чтобы назначить входам

ивыходам модели соответствующие выводы микросхемы.

4.6.Назначьте 8 сигналов для переключателей: gpio_0_tri_io[0]- gpio_0_tri_io[7] присвойте SW[0]–SW[7]. Установите стандарт напряжения ввода/вывода 2.5 В на всех переключателях.

4.7.Назначьте 8 сигналов светодиодов: gpio_0_tri_io[8]- gpio_0_tri_io[15]

присвойте LD[0]–LD[7]. Установите стандарт напряжения ввода-вывода 3.3 В на всех светодиодах.

4.8.Занесите номера соответствий между шиной Emio Gpio и внешними устройствами (светодиоды и переключатели) в протокол.

27

4.9.Сохраните установленную конфигурацию пинов в файл ограничений по аналогии с предыдущими работами.

4.10.Обратите внимание, что структура проекта изменилась: появилась отдельная директория с сохраненным файлом ограничений.

4.11.Откройте данный файл ограничений и проверьте правильность его заполнения.

4.12.Только после успешного синтеза и задания правильных ограничений возможно запустить размещение проекта внутри виртуального кри-

сталла ПЛИС. Нажмите Run Implementation на панели Flow Navigator.

Если появится окно, предлагающее параметры сохранения результатов размещения, то оставьте параметры без изменений и нажмите ОK.

4.13.Статус текущих задач в среде Vivado отмечается в виде анимированного индикатора в правом верхнем углу. После завершения процесса размещения запустите генерирование Bitstream.

5. Экспорт конфигурационных файлов в Xilinx SDK.

5.1.Нажмите File → Export → Export Hardware.

5.2.В появившемся окне установите галочку напротив Include Bitstream, затем нажмите ОK.

5.3.Найдите папку проекта и откройте в ней директорию с названием

имя проекта.sdk.

5.4.Уточните наличие файла-архива с разрешением hdf. Откройте данный архив и проконтролируйте его содержимое.

5.5.Нажмите File → Launch SDK и в появившемся окне – ОK. Дождитесь запуска среды Xilinx SDK.

5.6.Нажмите File → New → Board Support Package. Убедитесь, что выбран пункт Standalone, нажмите ОK.

6. Создание приложения.

6.1.Нажмите File → New → Application project. В открывшемся окне введите имя приложения EMIO-Logic и установите переключатель Board Support Package в положение Use existing. Затем нажмите Next.

6.2.В списке предлагаемых шаблонов приложения выберите Empty

инажмите Finish.

6.3.Нажмите правой кнопкой мыши на папке SRC проекта в дереве

Project Explorer (рис. 31) и выберите пункт меню New → Source File.

6.4. В появившемся окне введите имя файла main.c и нажмите Finish.

28

Рис. 31. Добавление файла в проект

6.5. Разрабатываемый алгоритм представлен в виде схемы, состоящей из логических операций (рис. 32).

SW [7] |

|

|

|

|

|

LED [4] |

||

|

|

|

|

|

|

|

|

|

SW [6] |

|

|

|

|

|

|

||

SW [5] |

|

|

|

|

|

LED [3] |

||

SW [4] |

|

|

|

|

|

|||

|

|

|

|

|

|

|||

SW [3] |

|

|

|

|

|

LED [2] |

||

|

|

|

|

|||||

SW [2] |

|

|

|

|

|

|

|

LED [1] |

|

|

|

|

|

|

|

||

SW [1] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

SW [0] |

|

|

|

|

|

|

LED [0] |

|

|

|

|

|

|

|

|||

Рис. 32. Разрабатываемая схема

Заполните табл. 4–7 истинности для каждого элемента (рис. 33–36) в протоколе.

Таблица 4

Соответствие входных и выходных сигналов

SW[1] |

SW[2] |

LED[1] |

0 |

0 |

|

|

|

|

0 |

1 |

|

1 |

0 |

|

1 |

1 |

|

Таблица 5

Соответствие входных и выходных сигналов

SW[3] |

LED[2] |

0 |

|

|

|

1 |

|

29