Лабораторные работы ВТиИТ

.pdfport(

data_i: in std_logic; clk_i: in std_logic; s : in std_logic;

r : in std_logic; data_out: out std_logic );

end tr;

architecture arch of tr is begin

process (clk_i,s,r) begin

if r='0' then data_out<='0'; elsif s='0' then data_out<='1';

elsif(rising_edge(clk_i)) then data_out <= data_i;

end if;

end process; end arch;

Программа4.3

library ieee;

use ieee.std_logic_1164.all;

entity trjk2 is port(

clk,s,r,j,k: in std_logic; data_out: out std_logic );

end trjk2;

architecture arch of trjk2 is signal q: std_logic;

begin

process (clk,r,s) begin

if r='0' then q<='0';

elsif s='0' then q<='1';

elsif(rising_edge(clk)) then if(j='1') then

if(k='0') then q<='1'; elsif(k='1')then q<=(not(q)); end if;

elsif (j='0') then

if(k='0') then q<=(q or '0'); elsif (k='1') then q<='0'; end if;

end if; end if;

end process; data_out<=q; end arch;

Лабораторная работа № 5.

Исследование счетчиков.

Цель работы: изучение функционирования схем синхронных счетчиков. Сравнительный анализ синхронных счетчиков.

В работе предлагаются для изучения VHDL - программы двоичных четырехразрядных счетчиков: суммирующего, вычитающего и реверсивного. По диаграммам работы проверяется порядок счета счетчиков. Реверсивный счетчик проектируется для работы в кристалле Cyclone EP1C6T144C8.

Порядок выполнения работы.

1.Создать новый проект, открыть VHDLфайл и записать программу 5.1, отражающую функционирование синхронного суммирующего счетчика. Сохранить файл и установить его старшим в иерархии. Откомпилировать файл.

2.Построить временные диаграммы работы счетчика, задав интервал синхроимпульсов 20нс. Сохраненный временной(.vwf) файл не хранится по умолчанию в корзине симулятора, поэтому симуляция должна следовать по пути: Processing – Simulator Tool – через поиск … находите необходимый файл – Start. По окончании симуляции нажмите Report и проанализируйте результат..

3.Открыть новый VHDL - файл и записать программу 5.2, отражающую функционирование синхронного вычитающего счетчика. Сохранить файл под новым именем, установить его старшим в иерархии и откомпилировать.

4.По методике, изложенной в п.2 построить временные диаграммы работы счетчика, задав интервал синхроимпульсов 20нс.

5.Открыть новый VHDL - файл и записать программу 5.3, отражающую функционирование синхронного реверсивного счетчика. Сохранить файл под новым именем, установить его старшим в иерархии и откомпилировать.

6.Построить временные диаграммы работы счетчика. Тактовая частота аналогична первому варианту, интервал реверса – 650нс.

Вернувшись в файл VHDL, cоздать библиотечный модуль реверсивного счетчика.

7.Из папки материалы, пользуясь методикой, описанной в п. лабораторной работы №3 записать в свой проект 3 файла antiring, multiplexor и decoder и создать для каждого библиотечный модуль. В новом файле графического редактора объединить модули счетчика с вновь созданными модулями периферийных устройств. Синхросигнал завести от кнопки через модуль antiring, выходы счетчика соединить со входами data0[..] модуля multiplexor, вход clk модуля multiplexor

обозначить теми же буквами, что записаны в примитиве input для входа clock модуля antiring. Выходы columns модуля multiplexor

поименовать col[3..0], отдельно вывести output, назвав его col[0]. В таблице изменить WIDTH на 4, выходы данных модуля multiplexor связать со входами данных модуля decoder. Выходы модуля decoder вывести через output. Реверс установить от любого тумблера через input. Сохранить файл, установить его старшим в иерархии и откомпилировать.

8.Произвести разводку в кристалл для полученного проекта. Контакты кнопки – pin 59, 60.

9.Запрограммировать кристалл и убедиться в правильности работы схемы.

Отчёт должен содержать: программы функционирования счётчиков и временные диаграммы их работы.

Программа 5.1

library ieee;

use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all;

entity cnt44 is port(

clk: in std_logic; ena : in std_logic; res : in std_logic;

q: out std_logic_vector(3 downto 0) );

end cnt44;

architecture arch of cnt44 is

signal cnt: std_logic_vector(3 downto 0); begin

process (clk,res) begin

if (res = '0') then cnt<=(others=>'0'); elsif(rising_edge(clk)) then

if(ena ='1') then

cnt <=cnt + "0001"; end if;

end if;

end process; q <= cnt; end arch;

Программа 5.2

library ieee;

use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all;

entity cnt441 is port(

clk: in std_logic; ena : in std_logic; res : in std_logic;

q: out std_logic_vector(3 downto 0) );

end cnt441;

architecture arch of cnt441 is

signal cnt: std_logic_vector(3 downto 0); begin

process (clk,res) begin

if (res = '0') then cnt<=(others=>'0'); elsif(rising_edge(clk)) then

if(ena ='1') then cnt <=cnt - "0001"; end if;

end if;

end process; q <= cnt; end arch;

Программа 5.3

library ieee;

use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all;

entity cnt442 is port(

clk: in std_logic; ena : in std_logic; res : in std_logic;

rev : in std_logic;

q: out std_logic_vector(3 downto 0) );

end cnt442;

architecture arch of cnt442 is

signal cnt: std_logic_vector(3 downto 0); begin

process (clk,res) begin

if (res = '0') then cnt<=(others=>'0'); elsif(rising_edge(clk)) then

if(ena ='1') then

if (rev ='0') then cnt <=cnt + "0001"; elsif (rev='1') then cnt <=cnt - "0001"; end if;

end if; end if;

end process; q <= cnt; end arch;

Лабораторная работа № 6. Исследование регистров.

Цель работы: знакомство с работой параллельных и последовательных регистров.

В работе предлагаются для изучения регистры сдвига на 8 разрядов последовательный и последовательно-параллельный . А также параллельный четырехразрядный регистр (буферный и защелка) .

Порядок выполнения работы.

Последовательные регистры.

10.Создать проект. Открыть новый VHDLфайл и записать программу 6.1, отражающую функционирование последовательного регистра на 8 разрядов. Сохранить файл, установить его старшим в иерархии и откомпилировать.

11.Открыть редактор временных диаграмм. Изобразить диаграммы при

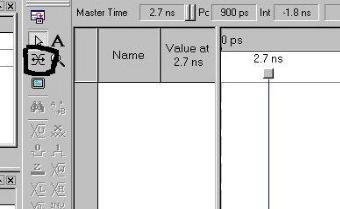

интервалах синхроимпульса – 20нс, данные –при базовом уровне «0» на интервалах от 10нс до 50 нс уровень «1» и от 130нс до 200нс уровень «1». Зарисовать полученные диаграммы, записать задержки. (для изображения отдельных интервалов необходимо воспользоваться иконкой бокового меню, показанной на рисунке)

9.Открыть новый VHDLфайл и записать программу 6.2, отражающую функционирование последовательно-параллельного регистра на 8 разрядов. Сохранить файл под новым именем, установить его старшим в иерархии и откомпилировать.

10.По методике, изложенной в п.2, построить временные диаграммы для последовательно-параллельного регистра.

11.Открыть новый VHDLфайл и записать программу 6.3, отражающую функционирование параллельного регистра на 4 разряда. Сохранить файл под новым именем, установить его старшим в иерархии и откомпилировать.

12.Построить диаграмму работы устройства при следующих параметрах: синхронизация – 20нс; данные – D0,D2 – 35нс, D1,D3 – 50нс; ena – 170нс; ctrl – 200нс.

13.Создать библиотечный модуль устройства.

Отчет должен содержать программы работы исследуемых устройств и их временные диаграммы.

Программа 6.1

library ieee;

use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all;

entity regsdv is port(clk,d_in:in std_logic;

d_out:out std_logic);

end regsdv;

architecture bb of regsdv is

signal shift: std_logic_vector (6 downto 0); begin

process (clk)

variable i: integer range 7 downto 0; begin

if(rising_edge(clk)) then shift(0)<=d_in; for i in 1 to 6 loop shift(i)<=shift(i-1); end loop; d_out<=shift(6);

end if;

end process; end bb;

Программа 6.2

library ieee;

use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all;

entity regsdv1 is port(clk,d_in:in std_logic;

d_out:out std_logic_vector (7 downto 0));

end regsdv1;

architecture bb of regsdv1 is

signal shift: std_logic_vector (7 downto 0); begin

process (clk)

variable i: integer range 7 downto 0; begin

shift(0)<=d_in; if(rising_edge(clk)) then

for i in 1 to 7 loop shift(i)<=shift(i-1); end loop; d_out<=shift;

end if;

end process; end bb;

Программа 6.3

library ieee;

use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all;

entity reg4 is port(

data_i: in std_logic_vector(3 downto 0); clk_i: in std_logic;

ena : in std_logic; ctrl : in std_logic;

data_out: out std_logic_vector(3 downto 0) );

end reg4;

architecture arch of reg4 is

signal regist: std_logic_vector(3 downto 0); begin

process (clk_i) begin

if(rising_edge(clk_i)) then

if(ena ='1') then regist <= data_i; end if;

end if;

end process;

data_out <= regist when ctrl = '1' else "ZZZZ"; end arch;