Otvety_Ekzamen

.pdf1)Типы цифровых устройств…

Эти устройства работают на 2х уровнях напряжения 0 и 1. Все уст-ва должны иметь схемы (логические элементы) где информация хранится, преобразуется и направляется. 2 типа схем: а) преобразования без учета предыдущего состояния (сумматоры, шифраторы и дешифраторы, мультиплексоры и демультиплексоры), б)запоминающие, преобразующие с учетом предыдущего состояния (триггеры, счетчики, регистры) Все цифровые устройства делятся на 2 больших класса: КЦУ и конечные автоматы.

2) Комбинационные циф. уст-ва. Шифратор и Дешифратор.

КЦУ это устройства не содержащие в своей структуре обратной связи, т.о. в каждый момент времени состояние выходов такого уст-ва зависит только от входного воздействия. КЦУ служит для преобразования информации и коммутации. К кодопреобразующим КЦУ относятся шифратор, дешифратор, различные типы кодопреобразователей, коммутационные КЦУ: (де)мультиплексор. Синтез КЦУ начинается с технического задания (определение функционирования), по заданию записываются таблицы функционирования и при необходимости логические уравнения, описывающие уравнения устройства. Для кодопреобразователя синтез производится аналогично рассмотренным устройствам( составляется таблица переключений, для каждого выхода записывается логическое ур-ние относительно входов). Дешифратор это уст-во, позволяющее определить направление по поступившему на входы адресу. В Каждый момент времени активный уровень может появиться только на одном выходе дешифратора, при этом индекс выхода совпадает с двоичным кодом пришедшего на входы адреса. M<=2Nгде N- входы, М-выходы. Шифратор это уст-во, определяющее адрес направления, по которому поступил запрос. В Каждый момент времени активный уровень м.б. только на одном входе уст-ва. При этом на выходах появляется двоичное отображение адреса, совпадающее с индексом входе. М<=log(2)N.

3) Комбинационные циф. уст-ва, де(мультиплексор).

КЦУ это устройства не содержащие в своей структуре обратной связи, т.о. в каждый момент времени состояние выходов такого уст-ва зависит только от входного воздействия. КЦУ служит для преобразования информации и коммутации. К кодопреобразующим КЦУ относятся шифратор, дешифратор, различные типы кодопреобразователей, коммутационные КЦУ: (де)мультиплексор. Синтез КЦУ начинается с технического задания (определение функционирования), по заданию записываются таблицы функционирования и при необходимости логические уравнения, описывающие уравнения устройства. Для любого кодопреобразовtателя синтез может производится аналогично рассмотренным устройствам( составляется таблица переключений, для каждого выхода записывается логическое уравнение относительно входов)

Мультиплексор, это уст-во, соединяющее с единственным выходом тот из входов данных, адрес которого указан на адресных входах. Если мы хотим на выходе собрать инфу со всех каналов: по каналу инфа идет с частотой f, а в нашем случае будет 2f*М.M<=2^N.

Демультиплексор это уст-во, распределяющее инфу с единственного входа на тот из выходов, адрес которого указан на входах.

4) Комбинационные циф. уст-ва. Сумматор

Сумматор, это уст-во, позволяющее получить арифметическую сумму 2х чисел, представленных в двоичном коде. Слагаемые, представленные в двоичной форме, должны иметь одинаковую разрядность. Сумматор нулевого разряда будет иметь 2 входа. Сумматор i-го разряда : разрядные вход и выход суммывнешние выводы устройства.Соединение одноразрядных сумматоров в многоразрядный производится по входам-выходам переноса. Одноразрядный сумматор имеет три входа ( два слагаемых и перенос их предыдущего разряда) и два выхода ( суммы и переноса в следующий разряд)

5) Конечные автоматы,типы конечных автоматов.

КА это уст-ва, содержащие в своей структуре обратные связи. Одна степень обратной связи позволяет хранить информацию – это связь внутри простейшей ячейки. Вторая

степень обратной связи позволяет преобразовывать информацию. В каждый момент времени состояние выхода автомата зависит не только от входного воздействия, но и от состояния выходов в предыдущий момент времени. КА служат для хранения информации, ее преобразований с учетом предыдущего состояния. К КА относятся : триггеры и все схемы построенные на основе триггерных ячеек( счетчики и регистры).

6) Простейший КА.

Простейшим КА явл. триггер. Триггер – конечный автомат, имеющий два устойчивых состояния –«0» и «1». Простейшие триггерные ячейки – T-триггер и асинхронный RSтриггер. Переключательный триггер (Т-триггер) имеет единственный вход и единственный выход. Состояние выхода меняется на противоположное на каждый фронт входного импульса. Для хранения Т-триггер не годится. Хранения инфо производится в триггерах установочного типа. Простейшей ячейкой установочного типа явл. асинхронныйRS триггер. Такой триггер имеет 2 установочных входа: вход установки единицы S(set) и вход установки нуля R(reset) и 2 выхода: прямой и инверсный. Установочным состояние триггера считается состояние прямого выхода, подтвержденное своей инверсией. Установочный уровень одинаков для обоих входов и зависит только от внутренней структуры триггера. Действительно, т.к. элемент И-НЕ управляется нулями, подача «0» навходы R и S приводит к хранению предыдущей информации с помощьюобратных связей. : - в асинхронном RS-триггере в каждый момент времени воздействие возможно только на один вход; - установка состояния происходит с задержкой tзтг = 2tз эл; - минимальная длительность импульса воздействия t и min= tзтг.

7) Функционирование D-триггера с динамическим синхровходом.

D-триггер служит для записи и хранения информации.Установка сигнала в такой схеме происходит с задержкой на инверторе, отсюда и название триггера - D, от слова delay – задержка. Имеет 3 группы входов: а) информационный вход D определяет вид информации, записываемой в триггер ( 0 или 1), б) вход синхронизации С- определяет время записи информации в триггер, в) асинхронные установочные входы S и R- позволяют производить начальную установку триггера. Функционирование: основная запоминающая ячейка на элементах 5 и 6, к ним подходят установочные входы R=1 S=1 (мы ничего не подаем). Представим,что на Q=0, Q(с чертой)=1, в это время сигнал от С=0, на D пришла 1 если С=0, то эл-ты 2 и 3 равны 1, следовательно основная ячейув в режиме хранения ( засчет обратной связи), элемент 1 находится в 0, а эл-т 4 нах.в 1. Далее поступает фронт синхроимпульса и С становится 1, следует что эл-т 3 станет 0 (на выходе), основная ячейка становится 1: Q=1,Q( с чертой)=0.Выход эл-та 3 поддерживает в 1 эл-ты 2 и 4, поэтому схема не зависит от изменения D. Фиксация информации на входе D производится только в момент подачи синхроимпульса, то есть только на фронте.

8) Типы триггеров, назначение входов. См вопросы выше

jk триггер - имеет два информациооных входа! Оба должны быть синхронизированны. Инфо входы работают подобно RS входам. Другое название универсальный тирггер(включает свойства установочного и переключательного) не имеет запрещенных комбинаций.

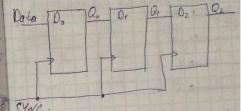

9) Счетчики, классификация по порядку счета.

Счетчики это уст-ва для подсчета синхроимпульса. Основа построения – триггеры переключательного типа. Счетчики можно классифицировать По порядку счета:

- суммирующие (каждое последующее состояние на единицу больше предыдущего,на каждый синхроимпульс триггер меняет свое значение если подать 1,чтобы поменять первый разряд нужно накопить ед. на нулевом разрядеё6второй разряд меняется когда на 1ом и на 2ом разрядах 1);вычитающие (каждое последующее состояние на единицу меньше предыдущего, следующий разряд переключается когда исчерпывается младший разряд);реверсивные (при подаче управляющего сигнала (1) функционируют как вычитающие, при снятии управления, как суммирующие). Граф переключений: 000-001- 010-011-100-101-110-111-000…

10)Счетчики, классификация по способу синхронизации и коэф счета.

Счетчики это уст-ва для подсчета синхроимпульса. Основа построения – триггеры переключательного типа. По способу подачи синхроимпульсов на разрядные триггеры: асинхронные (синхроимпульс подается на каждый последующий триггер с выхода предыдущего разряда); синхронные (синхроимпульс подается одновременно на все триггеры с единого входа синхронизации,а обратные связи устанавливаются с выходов на информационные входы). По коэффициенту счета K (количеству возможных состояний в цикле счета): двоичные (K=2n , где n – количество разрядных триггеров); недвоичные

(K<2n).

11)Принцип построения синхронных счетчиков…

Если строим КА, то наша задача построить связь между выходами и информационными входами триггеров так,чтобы при подаче очередного синхроимпульса совершился нужный переход состояний. Для этого строится таблица переходов и на ее основании таблица воздействия на входы. Затем для каждого входа прописываются связи, относительно предыдущих состояний выхода.

12) Регистры. Классификация

Регистры – устройства для хранения, либо для сдвига информации. Соответственно, функционально регистры могут быть параллельными, либо последовательными.

14) Параллельные регистры.

Регистры – устройства для хранения, либо для сдвига информации.

В них все триггеры подключаются к разрядам шины и информация записывается в них одновременно, по приходу синхроимпульса, аналогично и для считывания. Бывают регистры защелки и буферные регистры.

Регистры защелки:

в момент поступления синхроимпульса, состояние шины D передается шине Q. Синхроимпульсы в этом случае не следуют в общем потоке, а вырабатываются как отдельные управляющие сигналы. Пример, разделения общей внешней шины на шину адреса и шину данных внутри микро процессорной системы. Защелки используются для разделения шин.

Буферные регистры:

Если на одной шине подключено множество регистров, используются буферные регистры. Всегда запись происходит в момент прихода синхроимпульса

С1=1+SYNC - условие записи C2=1 – условие считывания

13) Последовательные регистры, принципы построения и функционирования:

осуществляют сдвиг информации Данные идут по одному проводу (однопроводная схема)

Запись информации – на фронте синхроимпульса. Если задержка триггера сравнима с длительностью фронта синхроимпульса, информация на одном такте может переписаться в несколько триггеров одновременно, во избежание такой ситуации между

триггерами ставятся линии задержки или триггер строится по двухтактной схеме: По спаду синхроимпульса информация выходит из триггера.

График работы

Где крестик: на входе единица Изначально DATA принимает импульс Время задержки – время синхроимпульса. Сдвиг влево (число увеличивается)

Если двигать от старшего к младшему – то будет сдвиг вправо.

Должны быть регистры, которые приведут информацию из последовательного вида в параллельный и наоборот.

15) Структуры регистров с различными способами записи и считывания.

По способу записи/считывания существуют послед-парал регистры и наоборот.

Параллельно-последовательные регистры

N – шина, по которой идет информация

Вмомент SYNC регистр записывает состояние N+ при условии что ena=1 D(i)=N(i)*ena - первый момент времени. После записи мы проталкиваем информацию, тогда D(i)=N(i)*ena V Q(i-1)* ena. Следующая запись будет через 13 тактов, подача сигналов “ena”=1 регулирует счетчик.

Последовательно-параллельные регистры

C2=1, тогда мы считываем информацию. МЫ читаем информацию с целью записать в парал. регистр когда подается синхроимпульс. Чтобы верно считать информацию мы ставим буфер чтения (он запрещает сдвиг информации), при С2=1 «ena” д.б. равна 0 (подача регулируется счетчиком.

16) Регистровые файлы. Принцип построения. Устройства, в которых используются.

Любое оборудование, построенное на многоразрядных ячейках можно назвать регистровым файлом, если аппаратно устанавливается регламент обращения для записи и чтения любой ячейки. (ячейка – буферно-параллельный регистр). Управление по записи и считыванию с ячеек строится с использованием счетчиков и управляющих КЦУ. Устройства построенные на основе регистровых файлов: LIFO – стэк память, это память временного хранения информации, кто последний пришел – первый вышел),

память FIFO. Должен быть REV-счетчик, определяющий число читаемых ячеек (запрет), в котором не было записи. Для стека подключаем буферы запись/чтение. Счетчик физически не связан со входами разрешающими запись/чтение, а только отмечает адрес текущий верхнего регистра.

17) устройства памяти. Общая классификация.

Все устройства памяти относительно процессорной системы м.б. внешними и внутренними. Мы будем смотреть внутреннюю: она м.б. адресной памятью, памятью с последовательным доступом или с ассоциативной памятью.

Вадресной памяти обращение к ячейкам накопителя может производиться по любому выставленному на шине адресу вне зависимости от адреса предыдущего обращения.

Впамяти с последовательным доступом обращение к ячейкам накопителя происходит в строго определенном порядке, регламентируемом счетчиком.

Вассоциативной памяти каждая ячейка содержит информацию, скопированную из основной памяти, т.е. эта информация имеет 2 адреса: адрес основной памяти, адрес собственно в ассоциативной.

По адресу в основной памяти определяется наличие информации в дополнительной (этот адрес также хранится в ассоциативной памяти), это КЭШ память.

18) Память с последовательным доступом

Впамяти с последовательным доступом обращение к ячейкам накопителя происходит в строго определенном порядке, регламентируемом счетчиком.

Построена по принципу регистровых файлов. Регистровый файл имеет структуру, построенную на многоразрядных ячейках (парал. буферных регистрах). Управление по записи и считыванию с ячеек строится с использованием счетчиков и управляющих КЦУ Для того, чтобы не считать больше записанного применяется реверсивный счетчик. Стек представляет собой регистр сдвига, ячейками которого являются параллельные регистры. Для просмотра доступен только первый регистр (нулевой разряд регистра сдвига), адрес которого на каждом такте меняется, обращение регламентируется с помощью реверсивного счетчика. При включении rev, идет запись. Информация продвигается от D(i) к D(i+1)

19) Адресная память. Принцип построения статических ОЗУ.

Адресная память основана на размещении данных в памяти по адресам хранения, в качестве которых служат номера ячеек. Код адреса однозначно определяет номера ячеек, в которых находится требуемая информация. Пример ROM, RAM: DRAM, SRAM (динамическая, статическая память)

Структура SRAM:

CSвход выборки кристалла, W/R – запись/чтение, по N адресным линиям мы можем определить одну из двух ячеек матрицы. N=K/2

Все входы “S” и“R” объединены для одной матрицы. К одной матрице подходит одна линия данных. (т.к в каждый момент времени мы можем активировать только одну ячейку).

Подключение линии данных «0» - вход активен по нулю

Если активен буфер чтения, то мы подключаем ячейку к внутренней линии и мы подкл. ее к внешней линии.

Вход CS – вход адресной области. Если выбор входа CS производится по старшим адресным линиям, это строничная организация, если по младшим – банковая организация. Предположим: общее пространство памяти 4К, а емкость схемы 1К, тогда обращение к схеме производится по 10 адресным линиям (т.к. 1 кбайт=1024 бит=2^10), а чтение по 12 линиям (2^12) для банковой: на дешифратор для направления на CS идет A0A1, с А2 на А11 – на схему, А11 А10 – на CS. – номер дома схема – номер квартиры.

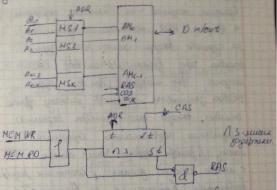

20) адресная память. Общие принципы построения динамических ОЗУ.

Адресная память основана на размещении данных в памяти по адресам хранения, в качестве которых служат номера ячеек. Код адреса однозначно определяет номера ячеек, в которых находится требуемая информация. Пример ROM, RAM: DRAM, SRAM (динамическая, статическая память)

Ячейками накопителя явл: увеличенные емкости, затвористок полевых транзисторов. Емкость мгновенно отработать не может. Активизация ячейки по строке и столбцу производится в 2 этапа. Для этого шина адреса мультиплексируется. Четные линии несут

адрес строки, нечетные адрес столбца.

Ко времени поступления нуля на вход RAS, вход мультиплекс. ADR в нуле, на входах схемы адрес строки. По срезу (нулев. фронту) импульса на вх RAS, адрес записывается в регистре защелки адреса строки. Выходы этого регистра соединены с дешифратором убирающем строку. Выбранная строка переписывается в регистр (при этом емкости разрешаются).

Единица поступила по линии задержки, на входах ADR появляются единицы, на адресных

входах схемы появляется адрес столбца, через время 2t на вход CAS поступает срез импульса, при этом адрес столбца запишется в регистр защелку адреса столбца, выходы этого регистра соединены с мультиплексором, позволяющим определить ячейку в регистре строки. После обмена с шиной данных состояние регистра возвращается в емкости, т.е. до времени 5t – восстановление информации. 5t – конец обращения, т.е RAS=1. Регенерация – поддержание емкости в рабочем состоянии.

21) адресная память. ПЗУ. Общая классификация.

Адресная память основана на размещении данных в памяти по адресам хранения, в качестве которых служат номера ячеек. Код адреса однозначно определяет номера ячеек, в которых находится требуемая информация. Пример ROM, RAM: DRAM, SRAM (динамическая, статическая память).

Пользователь в основном только читает. По конструкции матриц накопителя можно разделить ПЗУ на 2 класса:

1) Имеет матрицу накопителя на диодах: ROM, PROM (репрограммируемые ПЗУ) По адресу выбираем строку если с завода в ячейке «1», то диод есть, если 0 то наоборот.

2)EPROM: предполагалось стирание информации ультрафиолетовыми лучами. (со всех ячеек сразу). Теперь EPROM относится к схемам с исп. плавающего затвора.

Электрическое стирание информации это EEPROM. Как правило это двойной затвор. При электрическом стирании есть возможность стирания информации частями.

24) Общая классификация кристаллов программируемой логики

Кристаллпрограммируемая логическая интегральная схема, используемая для создания |

|||

́ |

́ |

́ |

́ |

цифровых интегральных схем.CPLD – комплексные программируемые логические устройства FPGA –программируемые пользователем вентильные матрицы. Любая логическая схема имеет внутреннюю и внешнюю часть. Схема устройства строится во внутренней части. Во внешней части находятся контактные площадки и все адаптирующие элементы. Любая внутренняя часть для любого типа состоит из логических блоков, определенным образом соединенных между собой. При рассмотрении класса кристалла необходимо рассматривать структуру логического блока, систему межсоединений и строение памяти конфигураций.

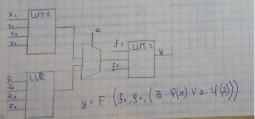

25) ПЛМ и ПМЛ. Простые программируемые логические устройства. Предположим что необходимо синтезировать устройство, описанного следующей системой уравнений:

У этого устройства есть три входа и три выхода. Решение такой системы возможно с использованием двух типов матриц: умножения или сложения. Результат первичного действия «*» - терма. M*t*n –параметры матричных устройств (количество входов, термов, выходов). вход 1 – ток с линии терма уходит на выход (к след. Матрице) 0 – ток с линии терма уходит на вход. Матрица И всегда полнодоступна, т.е. каждый вход потенциально доступен каждому терму. Матрица элементов ИЛИ может быть как полнодоступной, так и не полнодоступной. В неполнодоступной каждому выходу доступна лишь определенное количество термов. В случае полнодоступной матрицы устройство – программируемая логическая матрица , В другом же – программируемая матричная логика. 12*64*16 ПЛМ- в каждый выход доступн 64 терма, ПМЛ-4

26) Общая структура CPLD

Внутреняя часть CPLD представлена логическими блоками, объединенные с помощью программной матрицы соединений.

ЛБ блоки от 2 до 16 Каждый логич. блок имеет структуру ПМЛ с параметрами 36*80*16, он состоит из 16

макро ячеек, в которые на один выход включены 5 термов.

Каждому терму любого ЛБ доступны 36 общих линий программируемой матрицы соединений.

Для увеличения количества сомнОжителей инверсный выход каждого 5-ого терма макроячейки доступен всем термам своего логического блока, т.е. появл. внутри ЛБ еще 16 внутренних соединений. Такое устройство называется разделяемый логический расширитель.

Существует возможность включения до 20 термов на один элемент «или» каскадно, т.е можем включить вместе до 4 макроячеек, в каждой по 5термов.

27) макроячейка. Каждая ячейка включает в себя один триггер(для хранения предыдущего состояния функции), т.е на основе CPLD даже самого крупного невозможно построить устройство имеющие более 256 триггеров.

Для увеличения количества сомнОжителей инверсный выход каждого 5-ого терма макроячейки доступен всем термам своего логического блока, т.е. появл. внутри ЛБ еще 16 внутренних соединений. Такое устройство называется разделяемый логический расширитель. С помощью параллельного расширителя объединяются 4 макроячейки то есть подключение до 20ти термов на один ИЛИ. Подключение термов к ИЛИ происходит с помощью матрицы распределения термов.

Выходы МЯ могут подключаться к выходным элементам, идущим во внеш. часть: или включается в ПМС: ПМС строится по структуре ПЛМ,т.е. появляется возможность связи любых макроячеек друг с другом.

26) принципы построения вентильных матриц (GA).

Вентиль – простейший базовый логический элемент И-НЕ или ИЛИ-НЕ. Эквивал. Вентиль – то количество переходов, из которых можно составить базовый логический элемент.

Внутренняя часть такого кристалла представляет собой матрицу логических блоков.

ЛБ для простейших схем вентильных матриц – это выделенное пространство переходов на основе которых строится узел схемы.

ЛБ объединяются между собой через линии каналов.

В первых вариантах вентильных матриц пытались внедрить безканальную структуру, т.е. соедин. логич. блоков через свободные переходы на границах блоков. Однако такая структура не выносит работу на высоких частотах. каналы также служат для отвода тепла. 28)структура логических блоков FPGA. Структура ЛБ различается по зернистости. Существует мелкозернистые структуры(на основе транзисторных пар или логический вентилей),структуры среднего зерна(основа управляемые мультиплексоры) и крупнозернистые. Блоки крупного зерна строятся на основе запоминающих устройств

LUT. Стандартная LUT имеет 16 ячеек, 4 входа.

Основные недостатки первых 2х поколений это неопределенность задержки на каналах и жесткость конструкции ЛБ.

29) Система межсоединений.

В первых структурах система соединений была безканальная, ЛБ соединялись через граничные переходы, в последующих поколениях появились каналы между ЛБ. Затем блоки стали делить на подблоки ( макроячейки) которые объединялись между собой через локальную матрицу соединений, а ЛБ через глобальную. Локальная матрица соединений использует принцип ПМС в CPLD.

30) Память конфигурации FPGA.

Память конфигурации построена на триггерх. Память конфигурации на основе SRAM может быть распределенной и выделенной. Выделенная память это встроенные блоки памяти LUT( память которая работает по табл истинности).Распределенная память это триггеры в составе ЛБ запоминающий предыдущее состояние схемы и триггеры хранящие сведения о соединении на каналах. Через тран-тор 1 записываем инфо в триггер, дальше триггер управляет тр-ром 2, если в триггере 1 то (.)коммутации есть. CPLD: Память конфигураций построена на основе EEPROM (память распределенная энергонезависимая).

31) Основные различия кристаллов.

Принципиальные различия заключаются в том, что в CPLD содержатся укрупненные ЛБ на основе элементов 2И-НЕ, 2ИЛИ-НЕ, а в FPGA в структуре содержатся более компактные ЛБ на основе таблицы истинности, количество ячеек FPGA превышает кол-во ячеек в CPLD на 1-2 порядка. Алгоритмы программирования интегральных схем заключается в переносе конфигурации матрицы соединения на память интегральной схемы. CPLD содержит энергонезависимую память, поэтому при старте системы ее не надо каждый раз загружать, она сохраняется, а в FPGA при включении каждый раз надо заново загружать конфигурацию.

32) Структуры кристаллов последних поколений.

В схемах 4го и 5го (FPGA) поколений ЛБ объединяются в мегаблоки. Кроме ЛБ в состав магеблока входят встроенные блоки памяти существенно больше емкости ( не 2К, а 16К), схема быстрого умножителя 16на16 и блок управления частотой, в котором кроме изменения фазы основной частоты есть возможность умножения и деления основной частоты, а так же изменение фазы полученной частоты. ЛБ в такой системе условно разделился на 2 части «правую» и «левую», в левой таблицы (LUT), в правой комбинаторная логика объединенная с помощью каналов только для мегаблоков.

33) Протокол JTAG. Структура ТАР

Протокол нужен для проверки(тестирования) схем. ТАР( порт тестирования, через который информация передается на плату(схему, которую мы тестируем)) состоит из 2х основных частей: контролера, сдвиговые регистры, состоящие из ячеек граничного сканирования (BSC), расположенных во внешней области кристалла. Контролер это КА на 16 состояний переключения из одного состояния в другое зависимо от выбора режима. 1ый связь ячейки с внутренней частью, 2ой-связь ячейки с контактной площадкой, 3ий это и то и другое.

34) Протокол JTAG. Режимы работы ячейки.

Протокол нужен для проверки схем. 1ый режим-режим считывания конфигурации или программирования, 2ой-чтение соединений на плате( соединение с контактной площадкой), 3ий-проверка функционирования платы. Ячейка состоит из 2х триггеров. Первая ячейка связана с контактной площадкой, запись всегда производится в первую ячейку, а затем сдвигается в следующие. C1 осуществляет сдвиг в n-ую ячейку, от с2 синхроимпульс позволяет фиксировать инф-цию в триггере Т2 и затем вывести на выход.

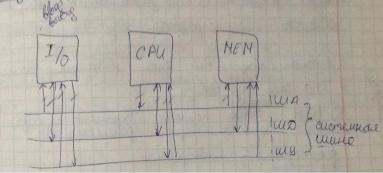

35) Общая структура микропроцессорной системы

Все в блоки в системе д.б. связанны проводами. ША(шина адреса) – однонаправленна, на нее процессор вставляет адрес устройств в пространстве памяти или в пространстве ввода-вывода с которыми должен производится обмен. Обмен производится по ШД(шина данных ) (если ОЗУ, то мы можем и писать и читать, а если ПЗУ то только читать)

ША и ШД группа проводников, на которых записывается число параллельным способом. ШУ(шина управления) состоит из отдельных проводов (пример: прерывание внешних источников, запрос на захват шины)

контроллер винчестера выдаст запрос HOLD на захват шины, HLDAответ, разрешение на захват шины)

3)Основной блок : CPU – Блок центрального процессора

4)I/O – блок ввода-вывода

5)MEM – блок памяти (хранятся и коды и данные)

36)Производительность процессоров, типы микропроцессоров.

Производительность процессоров обратно пропорциональна времени тестовой задачи. Единица времени - период тактовой частоты.

I-кол-во тактов в инструкции, T – число тактов, n – кол-во инструкций на задачу

T*I*n=p

По мере возрастания тактовой частоты начали возникать трудности. Решение: уменьшили кол-во инструкций nдля этого нужно было создавать сложные инструкции( Intel)

Intel CISC(complex instruction set computer )– процессор со сложным набором инструкций. В ядре много сложных устройств (служебные регистры, счётчик).Таким образом кол-во тактов в инструкции при этом увеличивается. Внутренняя память такого процессора содержит небольшое кол-во регистров, каждый из которых несет свою определенную функцию, поэтому могут быть использованы для хранения информации только в отсутствии этой функции в задаче. Поэтому CICS процессоры при выполнении операции могут брать операнды из блока памяти. Это способствует наличию разных форматов у команд одной группы. Но путь понижения «n» не эффективен, поэтому решили, что лучше процессоры у которых I=1. RISC процессоры - процессоры с ограниченным набором инструкций . Основные инструкции однотактовые. Все команды работы вынесены в отдельный блок.

Внутренняя память такого процессора содержит большое кол-во регистров. Формат команд у такого процессора всегда одинаковый – 16 бит и 32 бита.

37)Существует два типа микропроцессорных систем:

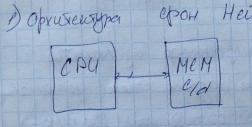

1) Архитектура Фон Неймана

Имеется общая шина данных для общения с памятью, выделяется место и для кодов и для данных. Каждая команда должна быть дешифрована, разделение кодов и данных производится внутри процессорного блока(демультиплексирование на входе)

Имеется общая шина данных для общения с памятью, выделяется место и для кодов и для данных. Каждая команда должна быть дешифрована, разделение кодов и данных производится внутри процессорного блока(демультиплексирование на входе)

Плюсы: пространство памяти можно изменить Минусы: если необходимо взять данные , получается, что на момент выдачи(записи) операнда, прекращается поток инструкции

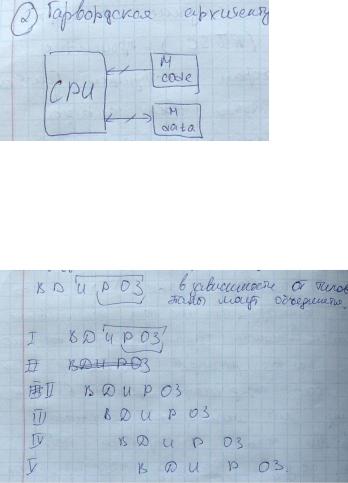

2) Гарвардская Инструкции записываются по одной линии, а данные по другой. Плюсы: процессор не

останавливает на время выдачи операнда, минус: нет возможности распределять пространство памяти.

38)Конвейер. Этапы выполнения операций.

Действия в процессоре производятся конвейерным способом. Процесс выполнения команды можно разделить на этапы (максимум 5): В – выборка, Д-дешифрация, И – исполнение, Р – результат, ОЗ – обратная запись.

В зависимости от типов команды могут объединяться. Если в процессоре выполняются сложные много тактовые команды, то неизбежен простой конвейера.