- •Введение

- •1. Архитектура микропроцессорных систем.

- •1.1. Базовая структура мпс.

- •1.2. Типы межмодульных связей.

- •1.3. Функции средств сопряжения.

- •1.4. Методы адресации элементов.

- •1.5. Способы организации связи с внешними устройствами.

- •1.5.1. Программно-управляемый обмен.

- •1.5.2. Обмен по прерываниям.

- •1.5.3. Прямой доступ к памяти (пдп).

- •1.6. Типы магистралей.

- •1.7. Элементы памяти мпс.

- •1.8. Сопряжение микропроцессора с магистралью.

- •1.9. Аналого-цифровые и цифро-аналоговые компоненты.

- •1.9.1. Цифро-аналоговые преобразователи.

- •1.9.2. Аналого-цифровые преобразователи.

- •1.10. Мп в контуре управления.

- •1.11. Особенности многопроцессорных систем.

- •1.12. Программное обеспечение мпс.

- •2. Разработка микропроцессорных систем.

- •2.1. Формулировка проблемы.

- •2.2. Выбор коллектива разработчиков.

- •2.3. Разработка модели управления объектом.

- •2.4. Разработка алгоритма.

- •2.5. Выбор мп и построение структуры мпс.

- •2.6. Разработка аппаратных средств мпс.

- •2.7. Разработка программного обеспечения мпс.

- •3. Отладка мпс.

- •3.1. Особенности контроля и диагностики мпс.

- •3.2. Источники ошибок при проектировании и виды неисправностей.

- •3.3. Методы и инструментальные средства тестирования.

- •4. Лабораторный практикум.

- •4.1. Указание по технике безопасности.

- •4.2. Описание лабораторного комплекса.

- •4.2.1. Состав.

- •4.2.2. Работа с учебным микропроцессорным комплектом.

- •4.2.3. Работа с кросс-системой.

- •4.2.4. Описание модулей.

- •5. Проведение лабораторных работ.

- •5.1. Порядок выполнения работы.

- •5.2. Указания к отчету.

- •5.3. Варианты заданий.

- •5.4. Лабораторная работа № 1. Разработка математической модели мпс

- •5.5. Лабораторная работа № 2. Разработка концептуального алгоритма мпс

- •5.6. Лабораторная работа № 3. Разработка структурной электрической схемы мпс

- •5.7. Лабораторная работа № 4. Разработка программы мпс

- •5.8. Лабораторная работа № 5. Сборка макета структуры мпс

- •5.9. Лабораторная работа № 6. Отладка подпрограмм взаимодействия с ву

- •5.10. Лабораторная работа № 7. Комплексная отладка макета мпс

- •Список литературы

1.7. Элементы памяти мпс.

Память МПС является ее неотъемлемой и наиболее часто запрашиваемой микропроцессором (и/или ВУ) частью. Поэтому, чтобы получить высокие показатели работы МПС, при проектировании ЗУ необходимо выбирать такие БИС памяти, для которых:

- время обращения было бы меньше цикла чтение-запись МП, иначе быстродействие системы снизится из-за введения асинхронного режима по сигналам ГТ от ЗУ;

- адаптер ЗУ с магистралью был бы минимален (простое управление, одинаковые электрические параметры).

Промышленность выпускает большое количество типов БИС ЗУ, отличающихся емкостью, разрядностью, быстродействием, стоимостью, принципом запоминания (статические и динамические), потребляемой мощностью, конструктивным исполнением. Вид выбранной памяти сильно влияет на вопросы проектирования МПС. Поэтому приведем "грубую" классификацию ЗУ по критериям, принципиально важным для разработки.

Классификация запоминающих устройств (ЗУ).

На рисунке 30 дана упрощенная классификация ЗУ.

Сверхоперативные ЗУ обеспечивают время доступа к информации порядка 10-8…10-9 сек (к ним можно отнести регистры МП, его кэш-память), оперативные ЗУ - 10-7…10-8 сек, полупостоянные ЗУ - 10-2…10-6 сек (Flash-память, винчестеры, CD-накопители и др.). Постоянные ЗУ не изменяют своего состояния в процессе работы МПС.

Устройства последовательного доступа могут просматривать информацию только последовательно (накопители на магнитной ленте, стримеры и др.), параллельно-последовательного доступа – обычно вдоль радиуса и по окружности (два измерения: винчестеры, оптические накопители, ZIP-накопители и др.), произвольного доступа – любой элемент памяти по его адресу, ассоциативного доступа – по маске его содержимого.

|

|

|

Рис.30 |

Механизм запоминания для статических ЗУ основан на триггерном эффекте (реализуемым с помощью логических элементов, магнитными доменами, тонкими оптическими пленками и т.д.), а динамических – на сохранении заряда в некоторой полевой области полупроводниковых материалов. Если статические ЗУ могут сохранять информацию сколь угодно долго (ОЗУ - без выключения питания, ПЗУ - с выключением питания), то для динамических ЗУ необходима регенерация информации из-за потери заряда в рабочей области (токи утечек). Однако они обладают значительно большими объемами памяти и меньшим энергопотреблением по сравнению со статическими ЗУ в тех же конструктивах.

Подключение элемента памяти к МПС.

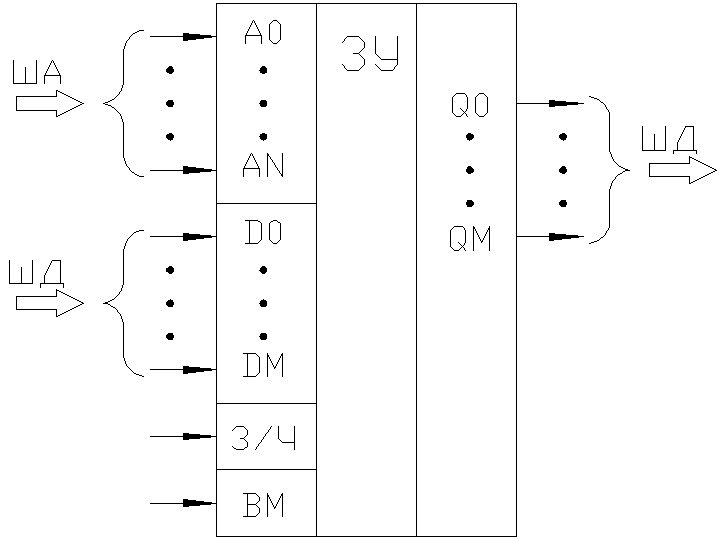

Типичная статическая БИС ЗУ имеет адресные входы, входы и/или выходы данных, управляющие входы записи/чтения и выборки элемента (микросхемы) (см. рис.31). Если количество адресуемых ячеек БИС ЗУ и их разрядность равна соответствующей разрядности шин адреса и данных МПС, то подключение элемента памяти выполняется так, как показано на рисунке 32, где КС – комбинационная схема, реализующая логику "записи-чтения" в конкретный вид запоминающего устройства. Если БИС ЗУ имеет инвертированные относительно D-входа Q-выходы или выходы с открытым коллектором, применяется адаптер, представляющий собой, соответственно, логические инверторы или резисторы, подключенные к источнику питания.

|

|

|

|

Рис.31 |

Рис.32 |

Если объем БИС ЗУ больше адресного пространства МПС, реализуемого шинами адреса, применяют расширенные методы адресации: метод окна, метод базовых регистров, метод банков и метод виртуальной памяти.

Организация блоков памяти.

В процессе конкретного выбора, чаще всего определяемого возможностями разработчика приобрести ту или иную БИС ЗУ и его симпатиями, возникает задача построить блок памяти большой емкости. При этом могут возникнуть следующие трудности.

Элементы памяти имеют недостаточное количество прямоадресуемых ячеек.

Элементы памяти обладают меньшей разрядностью ячеек, чем шина данных МПС.

Цикл "записи-чтения" элемента памяти больше программно-управляемого цикла обмена МП.

Элемент памяти динамичен.

Рассмотрим последовательно пути преодоления указанных трудностей. В первом случае БИС ЗУ объединяются параллельно по младшим адресным шинам и шинам данных, имея разные комбинационные схемы логики управления, связанные с дешифратором адреса от старших адресных шин (см. рис.33.

|

|

|

|

Рис.33 |

Рис.34 |

В случае нехватки разрядов БИС ЗУ объединяются параллельно по адресным шина, имея общую комбинационную схему управления (см. рис.34). Общий случай представлен на рисунке 35.

Для "медленных" ЗУ самым простым решением является использование асинхронного режима обмена с использованием управляющего сигнала "Готовность". Этот сигнал может быть сформирован по фронту управляющих сигналов "Запись" или "Чтение" с помощью схемы одновибратора (см. рис.36).

Блок сопряжения динамических ОЗУ несколько сложнее, так как требуется регенерация хранимой в них информации. Регенерация заключается в периодическом последовательном переборе входных шин адреса БИС ОЗУ. Регенерационная часть блока сопряжения строится на основе синхрогенератора (ГТИ), сдвигового регистра (RG) и мультиплексора (MS), который периодически отключает адресные шины БИС ОЗУ от магистрали и подсоединяет их к сдвиговому регистру. Регенерация может выполняться как с прерыванием обращения МП к ОЗУ, так и без него, если в цикле обращения к ОЗУ можно выделить достаточный временной интервал для работы мультиплексора (см. рис.37). Здесь "ВК" – выбор канала.

|

| |

|

Рис.35 | |

|

|

|

|

Рис.36 |

Рис.37 |