книги / Элементы и структуры систем автоматизации технологических процессов нефтяной и газовой промышленности

..pdfПри хранении битовой информации один из транзисторов (Т1 или Т2) этого триггера находится в открытом состоянии, а другой закрыт. При обращении к этому запоминающему элементу на шине выборки ШВi появляется высокий потенциал. Этот потенциал открывает транзисторы Т4 и Т3, в результате чего источник питания с напряжением Uи.п будет подключен через эти транзисторы к той шине записи/считывания (Di или Di инверсное), для которой соответствующий транзистор (Т1 или Т2) будет закрыт. Таким образом, потенциал (символ) на этих шинах зависит от состояния триггера этого запоминающего элемента.

При записи информации в ЗУ шина выборки ШВi остается активной, при этом подача нулевого потенциала через открытый транзистор Т3 на инверсную шину Di закрывает транзистор Т2 подачей низкого потенциала на его затвор. При этом высоким потенциалом стока транзистора Т2 транзистор Т1 открывается. Таким образом, для записи символа 0 на инверсную шину Di подается низкий потенциал, если же такой потенциал подать на прямую шину Di, то в ЗУ запишется символ 1. Считывание состояния триггера ЗУ производится через шины столбцов Di, которые подключаются к соответствующим усилителям.

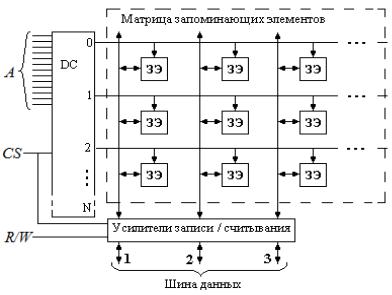

Запоминающие элементы ОЗУ поразрядно собираются в запоминающую матрицу, принципиальная структура которой показана на рис. 69. В этой матрице шины выборки ШВi запоминающих элементов построчно подключены к выходам дешифратора DС. Обращение к каждой из этих шин производится через адресную шину А дешифратора. Информационные шины Di запоминающих элементов матрицы группируются в строки, каждая из которых предназначена для хранения конкретного цифрового сигнала.

Все строки запоминающей матрицы подключены поразрядно к усилителям записи/считывания. Управление процессом работы запоминающей матрицы осуществляется с помощью сигналов CS, R/W, активизация которых обеспечивает переключение матрицы в соответствующий режим работы. Так, для записи

111

в матрицу цифрового сигнала на ее вход CS (разрешение на работу ячейки памяти) подается сигнал высокого уровня, а на адресном входе А ее дешифратора DС выставляется адрес ячейки (строки), в которую необходимо записать двоичное число (цифровой сигнал). Поразрядная запись этого числа производится с шины данных через усилители записи в момент подачи сигнала W (запись). Аналогично подачей сигнала R (чтение) производится вывод на шину данных содержания ячейки матрицы с заданным адресом.

Рис. 69. Структура матрицы запоминающих элементов оперативной памяти

Если дешифратор плоской двумерной матрицы обозначить DСх и одновременно подключить дешифратор DСу (х, у – координаты матричного адреса ячейки), то получим трехмерную запоминающую матрицу с расширенным ресурсом памяти и с обращением к конкретной ее ячейке через адресные координаты Ах, Ау. Включить ячейку такой матрицы можно сигналами CSi (i – номер слоя трехмерной запоминающей матрицы).

112

Постоянное запоминающее устройство

Постоянные запоминающие устройства, или память только для чтения (read only memory – ROM), относятся к устройствам памяти микропроцессорных систем, которые используют только для считывания информации. Информация, записанная в ПЗУ, либо вообще не меняется при работе микропроцессора, либо меняется редко. Постоянные запоминающие устройства имеют многоразрядную (матричную) структуру и выполняются на основе диодных или транзисторных элементов памяти.

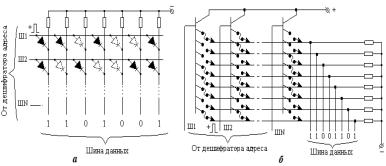

На рис. 70 изображены структуры нескольких вариантов постоянного запоминающего устройства. В одном варианте (рис. 70,а) это устройство выполнено по масочной схеме. Такие ПЗУ относятся к устройствам разовой памяти, которые программируются один раз в заводских условиях с помощью шаблона. Информация в эти ПЗУ записывается построчно на шинах Ш1,Ш2 …ШN (в ячейках памяти) путем наличия или отсутствия диода, соединяющего шину памяти (например, Ш2) с шиной поразрядного считывания числового сигнала. При наличии такого диода импульс высокого потенциала, подаваемый на шину ячейки памяти, при считывании информации поступает в соответствующий разряд линии считывания, что соответствует считыванию (записи) единицы в конкретном разряде двоичного слова. При отсутствии такого диода в соответствующем разряде этого двоичного слова будет зафиксирован (считан) ноль.

Рис.70. Структуры вариантов матрицы элементов постоянного запоминающего устройства

113

Описанная технология хранения постоянной информации является малоэффективной, так как требует заводских условий для записи информации и не позволяет ее оперативно обновлять.

На рис. 70,б изображена структура другого постоянного запоминающего устройства, выполненного по схеме PROM (Programmable ROM). Такие ПЗУ также относятся к устройствам разового программирования, однако запись информации в них не требует заводских условий. Для ПЗУ этого типа необходим специальный программатор, с помощью которого вне заводских условий в разовом порядке записывается информация.

Для записи и хранения информации (программы) в этом ЗУ используют многоэмиттерные транзисторы, базы которых через дешифратор адреса подключены к столбцам (выходам) дешифратора запоминающей матрицы, а эмиттерные входы (строки) отдельного транзистора составляют ячейки памяти, в которых записывается хранимая информация. Эмиттеры всех транзисторов ПЗУ подключены через плавкие перемычки к определенной эмиттерной строке, связанной через сопротивление нагрузки с отрицательным потенциалом. Эмиттерная перемычка, которая

внезапрограммированной исходной матрице всегда находится

внеразрушенном состоянии, может быть расплавлена (разруше-

на) импульсом тока предельной амплитуды |

и длительности. |

В процессе программирования матрицы на |

базу конкретного |

многоэмиттерного транзистора через дешифратор адреса подается сигнал высокого уровня, открывающий эту строку (ячейку памяти). Одновременно на шину данных подаются сигналы, соответствующие символам записываемой информации. Для нулевых символов этой информации в соответствующие разряды ячеек памяти (эмиттерные строки) подаются импульсы тока для плавления перемычек. Подобная операция для каждой эмиттерной строки (ячейки памяти) осуществляется через программатор.

ПЗУ типа ROM и PROM относятся к запоминающим устройствам разового программирования, так как не допускают в таких ячейках стирания старой и записи новой информации.

114

В настоящее время разработаны и применяются в микропроцессорных системах ЗУ типа EPROM и Flash, в которых старая информация может стираться электрическими сигналами, после чего эти устройства вновь готовы для записи новой информации.

Стирание информации в ячейках памяти EPROM производится облучением всего чипа ультрафиолетовыми или рентгеновскими лучами.

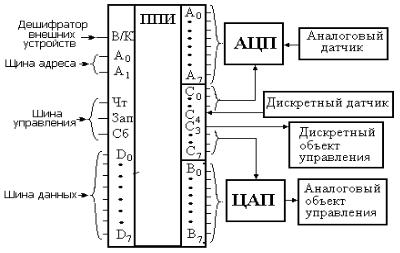

5.11.4. Программируемый параллельный интерфейс, параллельные порты микропроцессорных систем

Программируемый параллельный интерфейс (ППИ) (адаптер параллельной связи) служит для связи микропроцессора

сдискретными или аналоговыми объектами, в качестве которых могут быть датчики аналогового или дискретного типа или аналогичные исполнительные устройства. Этот структурный блок работает независимо от микропроцессора по собственной программе, представленной в виде управляющего слова.

Программируемый параллельный интерфейс (рис. 71) связан с микропроцессором через систему трех шин: шину адреса

ША (по адресным входам А0, А1), шину данных ШД (по входам D0, …, D7) и шину управления ШУ (по входам Чт, Зап, Сб). Вход В/К (выбор кристалла) используется для включения чипа (микросхемы) в работу через сигнал дешифратора внешних устройств. Связь параллельного интерфейса (ППИ) с внешними устройствами производится через цифровые дискретные выходы, которые группируются побайтно в порты (по восемь в одном порте, например В0, В1,…, В6, В7). Для ввода сигналов

саналоговых датчиков в эти порты встраиваются аналогоцифровые преобразователи, а для передачи сигналов к аналоговым исполнительным устройствам − цифроаналоговые преобразователи.

Все структурные элементы этого интерфейса связаны внутренней шиной, к которой с одной стороны примыкают буфер шины данных, устройство управления и регистр управления,

115

а с другой − буферы портов. Буфер шины данных предназначен для промежуточного хранения цифровых сигналов перед их передачей в шину данных или во внутреннюю шину ППИ. В качестве этих сигналов могут быть команды управления параллельным интерфейсом или сигналы, поступающие от внешних устройств или передаваемые для них.

Рис. 71. Структура связей ППИ с микропроцессором

ивнешними устройствами

Врегистре управления ППИ хранится управляющее слово, которое является программой для управления его работой. Исполнение этой программы производится устройством управления с учетом команд, поступающих от микропроцессора через шину управления. Буферы портов служат для промежуточного хранения информации, поступающей от внешних устройств или передаваемой для них.

Обращение микропроцессора к внутренним структурным блокам ППИ производится через комбинацию адресных входов А0 и А1. Структура этой комбинации представлена в табл. 10.

116

Порты параллельного интерфейса могут независимо работать как на ввод, так и на вывод информации. При работе конкретного порта на выводцифрового сигнала этот сигнал направляется микропроцессором по команде «Запись» через шину дан-

|

|

Таблица 1 0 |

|

|

|

|

|

А0 |

А1 |

|

Блоки ППИ |

0 |

0 |

|

Порт А |

1 |

0 |

|

Порт В |

0 |

1 |

|

Порт С |

1 |

1 |

|

Регистр |

|

|

|

управления |

ных в буфер данных ППИ, из которого в соответствии с комбинацией адресных входов этот сигнал направляется в соответствующий порт.

Если этот порт содержит ЦАП, то цифровой сигнал преобразуется на выходе порта в аналоговый. При отсутствии ЦАП

впорте выходной сигнал остается дискретно-цифровым. На выходе порта сигнал остается постоянным до тех пор, пока буфер порта не будет обнулен или пока новый сигнал не поступит

внего из буфера данных.

Работа конкретного порта при вводе сигнала происходит следующим образом. По команде «Чтение», которая поступает от микропроцессора по шине управления, сигнал аналогового датчика кратковременно поступает через АЦП в буфер порта, откуда по внутренней шине он передается в буфер шины данных, а затем по шине данных в микропроцессор. После этого буфер порта обнуляется в ожидании приема нового сигнала по новой команде «Чтение».

Сигналы дискретных датчиков подключаются к конкретному разряду (каналу) буфера порта без АЦП и вводятся аналогичным способом.

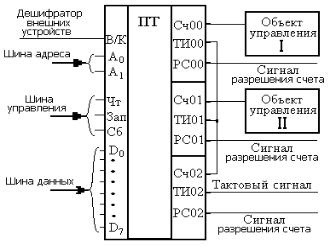

5.11.5. Программируемый таймер

Программируемый таймер (ПТ) в микропроцессорных системах применяется для управления объектами в функции времени. Как правило, в микропроцессорных системах эти устройства применяются для обработки импульсных сигналов.

Все структурные элементы этого устройства работают независимо от микропроцессора по собственной программе, представленной в виде управляющего слова.

117

Программируемый таймер (рис. 72) связан с микропроцессором аналогично программируемому параллельному интерфейсу, т.е. через шину адреса (ША) со входами А0, А1, шину данных (ШД) со входами D0,…, D7 и шину управления (ШУ) со входами Чт, Зап, Сб. Вход В/К используется для включения чипа (микросхемы) в работу через сигнал дешифратора внешних устройств. Связь программируемого таймера с объектами управления производится через выходы двоичных счетчиков.

Рис. 72. Структура связей ПТ с микропроцессором и объектами управления

Основу программируемого таймера составляют двоичнодесятеричные вычитающие счетчики, в которые исходный числовой параметр заносится изначально при установке временного параметра. Этот параметр уменьшается на единицу за каждый тактовый импульс, подаваемый независимо в каждый счетчик. Таймер оснащается несколькими счетчиками, которые работают независимо друг от друга по собственным программам, представленным в виде отдельных управляющих слов.

Обращение микропроцессора к внутренним структурным блокам ПТ производится через комбинацию адресных входов А0 и А1. Структура этой комбинации представлена в табл. 11.

118

Все структурные элементы программируемого таймера связаны внутренней шиной, к которой примыкают буфер шины данных, устройство управления и регистр управления и двоично-десятеричные вычитающие счетчики.

|

|

Таблица 1 1 |

|

|

|

|

|

А0 |

А1 |

|

Блоки ПТ |

0 |

0 |

|

Счетчик 00 |

1 |

0 |

|

Счетчик 01 |

0 |

1 |

|

Счетчик 02 |

1 |

1 |

|

Регистр управ- |

|

|

|

ления |

Буфер шины данных предназначен для промежуточного хранения цифровых сигналов перед их передачей в шину данных или во внутреннюю шину ПТ. В качестве этих сигналов могут быть управляющие слова (программы) для каждого из счетчиков ПТ или сигналы исходного или текущего состояния этих счетчиков. Работа всех структурных блоков программируемого таймера происходит под управлением устройства управления.

В регистре управления хранятся управляющие слова (программы) для каждого счетчика. Исполнение этих программ производится устройством управления с учетом команд, поступающих от микропроцессора через шину управления. Каждый из счетчиков программируемого таймераимеет одинвыходи двавхода.

На один из этих входов подаются тактовые импульсы, после каждого из которых содержание счетчика уменьшается на единицу (для некоторых таймеров тактовый импульс увеличивает числовое содержание счетчика). На другой вход счетчика подается импульс разрешения счета, который является командой разрешения на работу конкретного счетчика.

Выход каждого из счетчиков связан с объектом управления. Выходной сигнал счетчика может принимать состояние нуля или единицы в зависимости от его числового состояния и режима работы.

5.11.6. Программируемый последовательный интерфейс, последовательные порты микропроцессорных систем

Обмен информацией в параллельном коде через параллельные порты (интерфейсы) может быть успешно осуществлен только внутри микропроцессорной системы. Обмен информаци-

119

ей между микропроцессорными системами по этому принципу требует большого количества проводов, так как каждый разряд числового сигнала должен передаваться по отдельному проводу. Кроме того, этот процесс требует дополнительных проводов для передачи сигналов согласования приема и передачи числовых символов.

Проблема обмена информацией между двумя или несколькими микропроцессорными системами с минимальным количеством проводов успешно решается при применении последовательного кода (способа) передачи цифровых сигналов. По этому принципу в двухпроводной линии связи (ЛС) последовательно появляются цифровые двоичные символы с заданной разрядностью. Эти символы отображаются в сигнале в виде наличия или отсутствия импульсов заданной амплитуды и частоты. Для реализации такого способа передачи цифровой информации применяются устройства, которые называются последовательными интерфейсами (последовательными портами).

Последовательный программируемый интерфейс (порт) (ПосПИ) как структурный блок микропроцессорной системы работает независимо от самого микропроцессора по собственной программе, представленной в виде управляющего слова. Связи ПосПИ с управляющим микропроцессором через систему шин или с другим микропроцессором по линии связи показаны на рис.73.

Последовательный интерфейс связан с микропроцессором только через шину данных (ШД) и шину управления (ШУ). Причем в шину управления введены дополнительные связи для управления работой модема. Вход В/К используется, как и в предыдущих устройствах, для включения чипа (микросхемы) в работу через сигнал дешифратора внешних устройств.

С противоположной микропроцессорной системой последовательный интерфейс (порт) данного микропроцессора соединяется по линии связи, в которой выделяются две линии: линия передачи данных и линия синхронизации этой передачи. Данная схема ПосПИ представляет синхронную систему последова-

120