- •2. Этапы выполнения дисковых операций на примере операции «Чтение данных».

- •3. Контроллер fdd. Назначение узлов и регистров контроллера.

- •4. Связь контроллера fdd с накопителем. Физическая реализация интерфейса связи и назначение сигналов интерфейса fdd.

- •5. Блок-схема пк. Назначение чипсетов. Назначение интерфейсов pci, isa, usb, ata, agp, Centronics, rs232c.

- •6. Шина pci. Назначение шины, сигналы шины. Цикл обмена на шине pci.

- •7.Последовательность пакетов при вводе-выводе по шине usb.

- •8.Архитектура шины usb.

- •11. Драйвер принтер (программа int 17h). Операции, используемые при выводе данных на принтер.

- •12. Физическая реализация интерфейса Centronics. Назначение линий интерфейса. Временная диаграмма передачи данных по интерфейсу. Пояснить по диаграмме процесс передачи данных.

- •13. Назначение и организация интерфейса Centronics. Назначение контролера интерфейса (lpt-порта) и его регистров.

- •14.Электрические параметры передаваемых по интерфейсу rs 232c сигналов. Формат асинхронной передачи информации по интерфейсу rs232c.

- •15. Контроллер последовательного интерфейса rs232c (com-порт). Регистры контроллера, программирование контроллера.

- •16.. Назначение сигналов внешнего интерфейса rs 232c.

- •17. Драйвер (программа обслуживания) внешнего интерфейса rs 232. Операции программы и их назначение.

- •18. Назначение и организация интерфейса rs 232c. Суть асинхронного режима передачи данных по интерфейсу.

- •19. Драйвер монитора (программа int 10h). Формирование цветов в графическом режиме для видеосистемы vga.

- •20. Блок-схема и принцип работы графического видеоадаптера agp.

- •21. Режимы работы видеосистем пк. Организация видеопамяти видеоадаптера в текстовых и графических режимах.

- •22. Назначение и принцип работы узла ramdac видеоадаптера. Назначение регистров ramdac, обращение к регистрам.

- •23. Формирование сигналов r, g, b для монитора при работе видеоадаптера cga в графическом режиме.

- •24. Формирование сигналов r, g, b для монитора при работе видеоадаптера cga в текстовом режиме.

- •25.Программа прерывания int 16h (поддержка клавиатуры). Операции программы.

- •26. Назначение контроллера клавиатуры пк. (Основные функции и основные узлы).

- •27. Основные этапы выполнения программы прерывания int 9 (ввод данных из клавиатуры).

- •28. Блок-схема клавиатуры. Формирование данных для передачи в пк. Интерфейс связи клавиатуры с пк. Временная диаграмма передачи данных от клавиатуры в системный блок пк.

- •29. Классификационные характеристики стандартных интерфейсов пк.

- •30 Назначение регистров микросхемы uart, являющейся основой сом-порта, программно доступных cpu. Программирование сом-порта.

29. Классификационные характеристики стандартных интерфейсов пк.

Стандартные интерфейсы ПК делятся на следующие группы:

по функциональному назначению:

локальные

системные

внешние

сетевые

по способу передачи:

последовательные

параллельные

параллельно-последовательные

по типу соединений (передачи):

радиальный

одноточечный

магистральный

по режиму обмена:

симплексный (односторонний)

полудуплексный

дуплексный

мультиплексный

по принципу обмена информацией:

синхронный (тактируемый)

асинхронный (нетактируемый)

30 Назначение регистров микросхемы uart, являющейся основой сом-порта, программно доступных cpu. Программирование сом-порта.

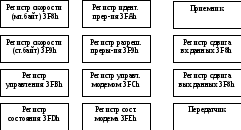

В COM-портах основной микросхемой является специализированная БИС UART (обычно i8250 или 16550A). Микросхемы UART с программной точки зрения представляют собой набор регистров, доступ к которым определяется адресом (смещением адреса регистра относительно базового адреса порта) и значением бита 7 регистра LCR (регистра управления линией).

Рассмотрим назначение регистров COM-порта.

При инициализации задается режим и параметры передачи работы (длина передаваемого слова, число стоповых бит и т.д.). Они заносятся в регистр управления и регистр скорости передачи. Некоторые регистры имеют одинаковые адреса. Поэтому конкретное обращение к регистрам с одинаковыми адресами зависит от регистра управления и начинать инициализацию следует с него.

B7=1

B7=0

B7=1

B7=0

B7=1 RxD

B7=0

B7=0

TxD

B7=0

B7=0

Назначение регистров БИС UART.

Передатчик - промежуточный регистр данных передатчика (только для записи). Данные, записанные в регистр, будут пересланы в выходной сдвигающий регистр (когда он будет свободен), из которого поступят на выход при наличии разрешающего сигнала #CTS. Бит 0 передается (и принимается) первым. При длине посылки менее 8 бит старшие биты игнорируются.

Приемник - буферный регистр принимаемых данных (только для чтения). Данные, принятые входным сдвигающим регистром, откуда они могут быть считаны процессором. Если к моменту окончания приема очередного символа предыдущий не был считан из регистра, фиксируется ошибка переполнения. При длине посылки менее 8 бит старшие биты в регистре имеют нулевое значение.

Регистр младшего байта делителя частоты (скорости передачи). Делитель определяется формуле D=115200/V, где V- скорость передачи (бит/с). Входная частота синхронизации 1,8432 МГц делится на заданный коэффициент, после чего получается 16-кратная частота передачи данных.

Регистр старшего байта делителя частоты (скорости передачи).

Регистр разрешения прерываний и регистр идентификации прерываний используются только в процедурах, в которых необходимо использовать режим прерывания при передаче данных по интерфейсу RS-232C.

Регистр разрешения прерываний. Единичное значение бита разрешает прерывание от соответствующего источника. Назначение бит регистра разрешения прерываний:

биты [7 : 4] = 0 - не используются;

бит 3 - по изменению состояния модема (любой из линий #CTS, #DSR, RI, DCD);

бит 2 - по обрыву (ошибке) линии;

бит 1 - по завершении передачи (передатчик свободен);

• бит 0 - по приему символа (получены данные в приемнике).

Если прерывания разрешены, то при появлении соответствующей ситуации, заданной в регистре разрешения прерываний, в регистр идентификации прерываний в биты В2 и В1 заносится тип прерывания (00 – изменение состояние модема; 01 – передан символ и передатчик пуст; 10 – получены данные для приема микропроцессором; 11 – поступило условие обрыва линии или ошибка приема. При этом бит В0 устанавливается в «1», и формируется аппаратное прерывание (сигнал на линиях IRQ3 или IRQ4). Регистр идентификации прерываний используется только для чтения. Для упрощения программного анализа UART выстраивает внутренние запросы прерывания по четырехуровневой системе приоритетов. Порядок приоритетов (по убыванию): состояние линии, прием символа, освобождение регистра передатчика, состояние модема. При возникновении условий прерывания UART указывает на источник с высшим приоритетом до тех пор, пока он не будет сброшен соответствующей операцией. Только после этого будет выставлен запрос с указанием следующего источника.

Регистр управления обменом (регистр настройки параметров передачи по интерфейсу).

бит В7 – управление доступом к регистрам с одинаковыми адресами;

бит В6 – формирование обрыва линии (посылка нулей);

бит В5 – принудительное формирование бита паритета:

а) В5=0 – контрольный бит генерируется в соответствии с заданными условиями паритета выводимого символа;

б) В5=1 – постоянное значение контрольного бита (при В4=1 – нулевое, при В4= 0 – единичное);

бит В4 – выбор типа контроля: 0 – контроль на нечетность, 1 – контроль на четность;

бит В3 – разрешение контрольного бита: 0 – контрольный бит запрещен, 1 – контрольный бит разрешен;

бит В2 – количество стоп- бит: 0 – 1 стоп-бит, 1 – 2 стоп – бита.

биты [1 : 0] – количество бит данных: 00 – 5 бит, 01 – 6 бит, 10 – 7 бит, 11 – 8 бит.

Регистр состояния обмена. Формат регистра:

бит В7=1 – тайм-аут (ошибка принятых данных в режиме FIFO). В режиме не FIFO бит В7 всегда равен 0;

бит В6=1 – регистр передатчика пуст, передача закончена, данных для передачи нет;

бит В5=1 – буферный регистр передачи пуст и готов принять данные для передачи;

бит В4=1 – обнаружен обрыв линии (постоянная передача нулей);

бит В3=1 – ошибка кадра (неверный стоп-бит);

бит В2=1 – ошибка паритета (ошибка контрольного бита);

бит В1=1 – ошибка переполнения при приеме (принят очередной символ раньше, чем прочитан предыдущий, при этом предыдущий символ теряется);

бит В0=1 – полученные данные готовы для чтения процессором.

Регистр управления модемом. Формат регистра:

биты [7:5]=0 – не используются;

бит В4 – режим работы UART: 0 – рабочий, 1 – диагностический;

бит В3 – разрешение прерываний с помощью внешнего выхода OUT2;

• бит В2 - управление выходным сигналом OUT1 (в рабочем режиме не используется);

бит В1 - управление выходом #RTS;

бит В0 - управление выходом #DTR.

Регистр состояния модема.. Регистр фиксирует состояние и изменение состояний линий управления интерфейса. Формат регистра:

бит В7 – состояние линии DCD;

бит В6 – состояние линии RI;

бит В5 – состояние линии #DSR;

бит D4 – состояние линии #CTS;

бит В3 – изменение состояния линии DCD;

бит В2 – изменение состояния линии RI;

бит В1 – изменение состояния линии #DSR ;

бит В0 - изменение состояния линии #CTS.

Признаки изменения биты [3:0] сбрасываются по чтению регистра.