- •ПРЕДИСЛОВИЕ

- •ЧАСТЬ I. ВАКУУМНАЯ ЭЛЕКТРОНИКА

- •Глава 1. Эмиссионная электроника

- •1.2. Эмиссионная электроника

- •1.2.1. Термоэлектронная эмиссия

- •1.2.2. Термоэлектронная эмиссия с поверхности полупроводников

- •1.2.3. Термокатоды

- •1.2.4. Фотоэлектронная эмиссия

- •1.2.5. Вторичная электронная эмиссия

- •1.2.6. Автоэлектронная эмиссия

- •Контрольные вопросы

- •Глава 2. Движение электронов в вакууме в режиме объемного заряда. Электровакуумные приборы

- •2.1. Диоды

- •2.2. Триоды

- •2.3. Многоэлектродные лампы

- •2.4. Особенности многоэлектродных ламп различного назначения

- •2.5. Генераторные и модуляторные лампы

- •2.6. Электровакуумные приборы диапазона сверхвысоких частот

- •2.6.1. Особенности движения электронов в СВЧ полях

- •2.6.2. Клистроны – приборы с динамическим управлением электронным потоком и резонансными системами

- •2.6.3. Лампы бегущей и обратной волны (ЛБВ и ЛОВ)

- •2.6.4. Лампы со скрещенными полями

- •2.6.5. Усилитель на ЛБВ типа М

- •2.6.6. Генератор на ЛОВ типа М замкнутой конструкции (карсинотрон)

- •2.6.7. Магнетроны

- •2.6.8. Статический режим работы магнетрона

- •2.6.9. Динамический режим работы магнетрона

- •Контрольные вопросы

- •Глава 3. Электронная оптика. Электронно-лучевые приборы

- •3.1. Электронные линзы

- •3.2. Электростатические линзы

- •3.2.1. Диафрагма с круглым отверстием

- •3.2.2. Иммерсионная линза

- •3.2.3. Одиночная линза

- •3.2.4. Иммерсионный объектив

- •3.3. Магнитные линзы

- •3.4. Аберрации электронных линз

- •3.5. Электронно-оптические системы (ЭОС) электронно-лучевых приборов

- •3.6. Отклоняющие системы

- •3.6.1. Электростатическое отклонение электронных пучков

- •3.6.2. Магнитное отклонение электронных пучков

- •3.7. Некоторые особенности электронной оптики интенсивных пучков

- •3.8. Приемные электронно-лучевые трубки

- •3.9. Проекционные ЭЛТ и системы

- •3.10. Запоминающие электронно-лучевые трубки

- •3.11. Передающие электронно-лучевые трубки

- •Контрольные вопросы

- •ЧАСТЬ II. ГАЗОРАЗРЯДНАЯ ЭЛЕКТРОНИКА

- •Глава 4. Элементарные процессы в плазме

- •4.1. Введение

- •4.2. Упругие соударения электронов с атомами и молекулами газа

- •4.3. Неупругие соударения электронов с атомами и молекулами

- •4.3.1. Возбуждение

- •4.3.2. Ионизация

- •4.3.3. Ступенчатые процессы при возбуждении и ионизации молекул электронным ударом

- •4.3.4. Образование и разрушение отрицательных ионов

- •4.3.5. Диссоциация молекул

- •4.3.6. Рекомбинация

- •4.4. Движение электронов и ионов в газе

- •4.4.1. Дрейфовое движение электронов и ионов

- •4.4.2. Диффузия заряженных частиц в условиях разряда

- •Контрольные вопросы

- •Глава 5. Основные виды электрического разряда в газе

- •5.1. Классификация разрядов

- •5.2. Несамостоятельный газовый разряд

- •5.3. Условие развития самостоятельного разряда. Пробой разрядного промежутка

- •5.3.1. Тлеющий разряд

- •5.3.2. Количественная теория катодной области тлеющего разряда

- •5.3.3. Дуговой разряд

- •5.3.4. Искровой разряд

- •5.3.5. Коронный разряд

- •5.3.6. Высокочастотные разряды

- •5.3.7. Разряды на сверхвысоких частотах

- •Контрольные вопросы

- •Глава 6. Газоразрядная плазма

- •6.1. Основные понятия

- •6.2. Диагностика плазмы

- •6.2.1. Метод зондов Лангмюра

- •6.2.2. Оптические методы исследования плазмы

- •6.2.3. Сверхвысокочастотные методы диагностики плазмы

- •6.3. Теории газоразрядной плазмы

- •Контрольные вопросы

- •Глава 7. Газоразрядные приборы

- •7.1. Приборы тлеющего разряда

- •7.1.1. Световые индикаторы

- •7.1.2. Стабилитроны тлеющего разряда

- •7.1.3. Вентили (газотроны) тлеющего разряда

- •7.1.4. Тиратроны тлеющего разряда

- •7.1.5. Переключаемые световые индикаторы

- •7.2.1. Газоразрядные источники света

- •7.3. Ионизационные камеры и счетчики излучений

- •7.3.1. Ионизационные камеры

- •7.3.2. Пропорциональные счетчики

- •7.3.3. Счетчики Гейгера

- •7.4. Разрядники антенных переключателей

- •7.5. Газоразрядные индикаторные панели

- •7.6. Газоразрядные знаковые индикаторы (монодисплеи)

- •7.6.1. ГИП постоянного тока

- •7.6.2. ГИП переменного тока

- •7.6.3. Получение полутоновых изображений на ГИП

- •Контрольные вопросы

- •ЧАСТЬ III. ТВЕРДОТЕЛЬНАЯ ЭЛЕКТРОНИКА

- •8.1. Концентрация носителей заряда в полупроводниках

- •8.2. Электропроводность полупроводников

- •8.3. Диффузионное движение носителей заряда в полупроводниках

- •8.4. Неравновесные носители заряда в полупроводниках

- •8.5. Поверхностные явления в полупроводниках

- •Контрольные вопросы

- •Глава 9. Электрические переходы

- •9.1. Структура и основные параметры n-p перехода

- •9.2. Равновесное состояние n-p перехода

- •9.3. Неравновесное состояние n-p перехода. Явления инжекции и экстракции носителей заряда

- •9.4. ВАХ идеализированного перехода

- •9.5. ВАХ реального n-p перехода

- •9.7. Емкостные свойства n-p перехода

- •9.8. Контакт металл-полупроводник

- •9.9. Гетеропереходы

- •Контрольные вопросы

- •Глава 10. Полупроводниковые диоды

- •10.1. Выпрямительные диоды

- •10.2. Высокочастотные и сверхвысокочастотные диоды

- •10.3. Импульсные диоды

- •10.4. Стабилитроны

- •10.5. Полупроводниковые управляемые емкости (варикапы)

- •10.6. Туннельные и обращенные диоды

- •10.7. Диоды Шотки

- •10.8. Диоды Ганна

- •10.9. Лавинно-пролетные диоды

- •Контрольные вопросы

- •Глава 11. Биполярные транзисторы

- •11.1. Классификация биполярных транзисторов

- •11.2. Физические процессы в транзисторе

- •11.3. Распределение токов в транзисторе

- •11.4. Эффект модуляции ширины базы

- •11.5. Статические вольтамперные характеристики биполярного транзистора

- •11.6. Частотные характеристики биполярного транзистора

- •Контрольные вопросы

- •Глава 12. Тиристоры

- •12.1. Классификация тиристоров

- •12.2. Распределение токов в тиристоре

- •12.3. Особенности работы управляемых тиристоров

- •12.4. Тиристор с симметричной ВАХ

- •Контрольные вопросы

- •Глава 13. Униполярные полупроводниковые приборы

- •13.1. Классификация и основные особенности

- •13.2. Полевые транзисторы с изолированным затвором (МДП-транзисторы)

- •13.4. Дифференциальные параметры МДП-транзистора

- •13.5. Принцип работы полевого транзистора с управляющим n-p переходом

- •13.6. Частотные характеристики МДП-танзисторов

- •13.7. Сравнительная характеристика МДП и биполярного транзистора

- •13.8. Биполярный транзистор с изолированным затвором (IGBT)

- •Контрольные вопросы

- •Глава 14. Светоизлучающие и фотоэлектронные полупроводниковые приборы

- •14.1. Светоизлучающие полупроводниковые приборы

- •14.1.1. Светодиоды

- •14.2. Фотоэлектронные полупроводниковые приборы

- •14.2.1. Поглощение оптического излучения полупроводниками

- •14.2.2. Фоторезистивный эффект и приборы на его основе

- •14.2.3. Фотоэлектрический эффект в n-р переходе

- •14.2.4. Фототранзисторы и фототиристоры

- •14.2.5. Оптоэлектронные пары

- •Контрольные вопросы

- •Глава 15. Полупроводниковые датчики

- •15.1. Датчики температуры

- •15.2. Датчики деформации

- •15.3. Датчики магнитного поля

- •Контрольные вопросы

- •Глава 16. Основы квантовой электроники

- •16.2. Физические основы взаимодействия излучения с веществом

- •16.2.1. Форма и ширина спектральной линии

- •16.3. Устройство и принципы работы лазеров

- •16.3.1. Рабочее вещество

- •16.3.2. Создание инверсии

- •16.3.3. Условия создания инверсной населенности

- •16.3.4. Двухуровневая система

- •16.3.5. Трехуровневые системы

- •16.3.6. Четырехуровневая система

- •16.3.7. Оптические резонаторы

- •16.3.8. Условия самовозбуждения и насыщения усиления

- •16.4. Свойства лазерного излучения

- •16.4.1. Монохроматичность

- •16.4.2. Когерентность

- •16.4.3. Поляризация излучения

- •16.4.4. Направленность и возможность фокусирования излучения

- •16.4.5. Яркость и мощность излучения

- •16.5. Типы лазеров

- •16.5.1. Твердотельные лазеры

- •16.5.2. Рубиновый лазер

- •16.5.3. Неодимовый стеклянный лазер

- •16.5.4. Nd – ИАГ – лазеры

- •16.5.5. Газовые лазеры

- •16.5.6. Атомные лазеры

- •16.5.7. Лазеры на парах металлов

- •16.5.8. Ионные лазеры

- •16.5.9. Молекулярные лазеры

- •16.5.10. Эксимерные лазеры

- •16.5.11. Газовые лазеры в инфракрасной области спектра

- •16.5.12. Химические лазеры

- •16.5.13. Газодинамические лазеры

- •16.5.14. Электроионизационные лазеры

- •16.5.15. Полупроводниковые лазеры

- •16.5.16. Жидкостные лазеры

- •Контрольные вопросы

- •Глава 17. Основы оптоэлектроники

- •17.1. Этапы и перспективы развития оптической электроники

- •17.2. Источники излучения для оптоэлектроники

- •17.3. Фотоэлектронные приемники излучения

- •17.4. Модуляция лазерного излучения

- •17.4.1. Физические основы модуляции лазерного излучения

- •17.4.2. Оптические модуляторы

- •17.4.3. Дефлекторы

- •17.5.1. Элементная база ВОЛС

- •17.5.2. Классификация ВОЛС

- •17.6. Оптические методы запоминания и хранения информации. Оптические (лазерные) диски

- •17.7. Голографические системы хранения и обработки информации

- •17.7.1. Принцип голографии

- •17.7.2. Голографическое запоминающее устройство

- •17.7.3. Голографические схемы записи и считывания информации

- •17.8. Системы отображения информации

- •17.8.1. Особенности зрительного восприятия информации

- •17.8.2. Физические эффекты, используемые для отображения информации

- •17.8.3. Жидкокристаллические индикаторы

- •17.8.4. Жидкокристаллические индикаторные панели

- •17.9. Электролюминесцентные индикаторы

- •17.10. Дисплеи с полевой (автоэлектронной) эмиссией

- •17.11. Отражающие дисплеи (электронная бумага)

- •17.12. Системы отображения информации на основе полупроводниковых светодиодов

- •Контрольные вопросы

- •ЧАСТЬ V. ФУНКЦИОНАЛЬНАЯ, МИКРО И НАНОЭЛЕКТРОНИКА

- •Глава 18. Предмет микроэлектроники

- •18.1. Основные термины и определения

- •18.2. Классификация ИМС

- •18.2.1. Плёночные ИМС

- •18.2.2. Гибридные ИС

- •18.2.3. Полупроводниковые ИМС

- •18.2.4. Совмещенные ИМС

- •18.3. Система обозначений ИМС

- •Контрольные вопросы

- •Глава 19. Биполярные структуры в микроэлектронике

- •19.1. Транзисторы с изоляцией на основе n-p перехода

- •19.2. Транзисторы с диэлектрической изоляцией

- •19.3. Транзисторы с комбинированной изоляцией

- •19.4. Транзисторы типа p–n–p

- •19.5. Многоэмиттерные транзисторы

- •19.6. Многоколлекторные транзисторы

- •19.7. Транзисторы с диодом Шотки

- •19.8. Интегральные диоды и стабилитроны

- •Контрольные вопросы

- •Глава 20. Униполярные структуры в микроэлектронике

- •20.1.1. МДП–транзистор с алюминиевым затвором

- •20.1.3. Конструкция Д–МДП–транзисторов

- •20.1.4. Комплементарные микроэлектронные структуры

- •20.2.1. Пороговое напряжение

- •20.2.2. Вольт-амперные характеристики

- •20.4. Принцип действия МЕП-транзистора

- •20.5. Элементы полупроводниковых постоянных запоминающих устройств (ПЗУ)

- •20.5.1. МНОП-транзистор

- •20.5.3. Двухзатворный МДП–транзистор

- •Контрольные вопросы

- •Глава 21. Микроэлектроника субмикронных СБИС

- •21.2. Методы улучшения характеристик субмикронных МДП-транзисторов

- •21.2.1. Ореол

- •21.2.2. Ретроградное распределение

- •21.2.3. Подзатворный диэлектрик

- •21.2.4. Области стока и истока

- •21.2.5. Напряженный кремний

- •21.3. Субмикронные МДП-транзисторы на диэлектрических подложках

- •21.3.1. Структуры «кремний на изоляторе»

- •21.3.2. Cтруктура «кремний ни на чём»

- •21.4.1. Транзисторы с двойным и с окольцовывающим затвором

- •21.4.2. Транзисторы с вертикальным каналом

- •21.5. Особенности субмикронных транзисторов для аналоговых применений

- •Контрольные вопросы

- •Глава 22. Гетероструктуры в микроэлектронике

- •22.1. Основные свойства гетероперехода

- •22.1.1. Сверхинжекция неравновесных носителей заряда в гетеропереходе

- •22.1.2. Понятие о двухмерном электронном газе

- •22.2. Гетероструктурные полевые транзисторы

- •22.2.1. Транзистор с высокой подвижностью электронов (НЕМТ)

- •22.2.2. Псевдоморфные и метаморфные структуры (р-НЕМТ и m-НЕМТ)

- •22.2.3. НЕМТ на подложках из GaN

- •22.3. Гетеропереходные биполярные транзисторы

- •22.4. Интегральные микросхемы на гетеропереходных полевых транзисторах

- •Контрольные вопросы

- •Глава 23. Пассивные элементы ИМС

- •23.1. Полупроводниковые резисторы

- •23.2. Плёночные резисторы

- •23.3. Конденсаторы и индуктивные элементы

- •23.4. Коммутационные соединения

- •23.4.1. Задержка распространения сигнала

- •23.4.2. Электороимграция

- •Контрольные вопросы

- •Глава 24. Функциональная электроника

- •24.1. Пьезоэлектроника

- •24.2. Оптоэлектроника

- •24.3. Акустоэлектроника

- •24.4. Магнитоэлектроника

- •24.5. Криоэлектроника

- •24.6. Хемотроника

- •24.7. Молекулярная и биоэлектроника

- •24.8. Приборы с зарядовой связью

- •24.9. Диэлектрическя электроника

- •24.10. Приборы на основе аморфных материалов

- •Глава 25. ОСНОВЫ НАНОЭЛЕКТРОНИКИ

- •25.1. Квантовые основы наноэлектроники

- •25.1.1. Квантовое ограничение

- •25.1.2. Интерференционные эффекты

- •25.1.3. Туннелирование

- •25.3. Квантовые транзисторы

- •25.4. Нанотрубки в электронике

- •25.5. Графеновые транзисторы (спинтроника)

- •25.6. Молекулярная электроника

- •25.6.1. Квантовые компьютеры

- •25.7. Заключение

- •Список рекомендуемой литературы

- •CПРАВОЧНЫЙ РАЗДЕЛ

- •Содержание

Глава 19. Биполярные структуры в микроэлектронике

Транзисторы полупроводниковых микросхем имеют существенные отличия от обычных дискретных приборов. По технологическим и ряду других причин, связанных с электрофизическими параметрами полупроводниковых материалов, в микросхемах используют только кремниевые биполярные транзисторы. Наиболее широко применяют n-р-n транзисторы, так как вследствие большей подвижности электронов в базе они имеют более высокие граничные частоты и быстродействие.

Главные различия структур биполярных транзисторов полупроводниковых микросхем и дискретных транзисторов заключаются в том, что первые содержат дополнительные области, изолирующие их от общей полупроводниковой подложки, и все выводы от областей транзистора располагаются в одной плоскости на поверхности подложки. Такая структура называется планарной. Она позволяет соединять транзисторы между собой и

с другими элементами микросхемы пленочными металлическими проводниками, формируемыми на той же поверхности.

Биполярный транзистор n-p-n типа является ключевым элементом полупроводниковых микросхем. Остальные элементы микросхемы выбираются и конструируются таким образом, чтобы они совмещались с основной структурой. Их изготавливают одновременно с созданием n-p-n транзистора, поэтому конструкция и технология изготовления транзисторов

также должна обеспечивать возможность одновременного создания и других элементов (диодов, резисторов, конденсаторов и т. д) на основе полупроводниковых слоев, образованных при формировании эмиттерной, базовой или коллекторной областей транзистора. Таким образом, выбор

физической структуры транзистора однозначно определяет все основные электрические параметры микросхемы. В этом состоит важное требование конструктивно-технологической совместимости элементов полупроводниковых микросхем. Кроме того, к структурам биполярных транзисторов, как и других элементов микросхем, предъявляется специфическое требование – площадь, занимаемая ими на полупроводниковой подложке, должна быть минимально возможной для повышения плотности упаковки элементов и степени интеграции.

В отличие от дискретных полупроводниковых приборов в ИМС важное значение имеет изоляция отдельных элементов ИМС друг от друга. Вид

изоляции в основном определяет конкретную схему технологического процесса. Различают три основных способа:

∙Изоляция с помощью обратно смещенного n-р перехода;

∙ИМС с диэлектрической изоляцией;

∙ИМС с комбинированной изоляцией.

375

Каждый из видов изоляции имеет множество разновидностей и модификаций.

19.1. Транзисторы с изоляцией на основе n-p перехода

Данный способ изоляции получил наибольшее распространение при изготовлении микросхем малой степени интеграции. Поскольку обратный ток изолирующего перехода мал, обеспечивается удовлетворительная

изоляция транзистора от подложки и других элементов кристалла микросхемы. Области, окруженные со всех сторон изолирующим переходом, называют карманами. В них размещают не только биполярные транзисторы, но и другие элементы микросхемы. Обычно в каждом кармане формируют один элемент, но в некоторых случаях размещают несколько биполярных транзисторов, у которых согласно принципиальной электрической схеме соединены коллекторы.

Структура транзистора ИМС данной группы показана на (рис. 19.1).

а)

б) в)

Рис. 19.1. Структура(а) и варианты топологии (б, в) интегрального эпитаксиально-планарного n-p-n транзистора: 1 – изолирующая область, 2 – эпитаксиальный слой, 3 – скрытый слой, 4 – базовая область, 5 – эмиттерная область, 6 – коллекторная приконтактная область

376

Транзистор формируется на высокоомной подложке р–-типа толщиной 200–300 мкм в эпитаксиальном слое n-типа. Локальной диффузией донорных примесей (мышьяка или сурьмы), имеющих малый коэффициент диффузии по сравнению с бором и фосфором, в подложке перед наращиванием эпитаксиального слоя создают скрытый слой n+-типа с низким удельным сопротивлением. Хотя первоначально скрытый слой формируют в подложке, при дальнейших высокотемпературных операциях (эпитаксии, окислении, диффузии примесей) он расширяется в сторону как подложки, так и эпитаксиального слоя.

Диффузией бора через маску из диоксида кремния на глубину, превышающую толщину эпитаксиального слоя, формируют изолирующую область р+-типа, окружающую коллекторную область n-типа с боковых сторон.

Базовую область р-типа получают следующей локальной диффузией бора на глубину 2–3 мкм (глубина залегания металлургической границы коллекторного перехода). Граница базы одновременно является границей коллекторного n-р перехода и определяет его площадь. Последняя локальная диффузия используется для формирования эмиттерной области n+-типа и коллекторной приконтактной области. Донорной примесью в этом случае обычно служит фосфор, обладающий повышенным коэффициентом диффузии и повышенной растворимостью в кремнии.

Впленке диоксида кремния (толщина 0,5...1 мкм), покрывающей поверхность кристалла, создают контактные отверстия, через которые напылением пленки алюминия формируют контакты к эмиттеру, базе, коллектору и подложке. Одновременно создают внутрисхемные проводники, соединяющие элементы микросхемы. Коллекторная контактная область с высокой концентрацией доноров необходима потому, что при напылении пленки алюминия на слаболегированный слой n-типа получается выпрямляющий контакт (диод Шотки), что недопустимо.

К подложке в периферийной части кристалла микросхемы создают омический контакт (на рисунке не показан). При использовании микросхемы на этот контакт подают напряжение, при котором изолирующий переход всегда смещен в обратном направлении.

Вструктуре дискретного транзистора отсутствуют изолирующие р+- области, а контактная n+-область и вывод коллектора расположены снизу. Поэтому ряд параметров рассмотренного транзистора хуже, чем у дискретного: выше сопротивление коллекторной области, имеется ток утечки

вподложку, ниже граничная частота и быстродействие из-за влияния барьерной емкости изолирующего n-р перехода.

Основное достоинство метода изоляции n-р переходом – простота технологии формирования изолирующих областей р+-типа. Для их создания применяют такие же технологические процессы (фотолитографию, диффузию примесей), что и для получения основных областей транзистора – базовой и эмиттерной. Однако изоляция n-р переходом не является совершенной: обратный ток этого перехода резко увеличивается при

377

повышении температуры и под воздействием ионизирующих излучений. Изолирующий переход вносит барьерную емкость, которая снижает

граничную частоту аналоговых микросхем и увеличивает задержку переключения импульсных схем.

Кроме того, изолирующие области n+-типа занимают значительную площадь кристалла (по сравнению с площадью основных областей транзистора), так как их ширина должна быть больше удвоенной толщины эпитаксиального слоя. Это условие связано с изотропностью процесса диффузии: примеси диффундируют не только в глубь эпитаксиального слоя, но и в боковом направлении – под маску.

Важной конструктивной особенностью эпитаксиально-планарных транзисторов является скрытый слой n+-типа, предназначенный главным

образом для уменьшения объемного сопротивления коллекторной области и напряжения насыщения транзистора. Уменьшение удельного сопротивления

коллекторной области за счет увеличения степени легирования всего объема нерационально, так как снижается напряжение пробоя перехода коллектор– база и увеличивается емкость этого перехода, что ухудшает характеристики транзистора. Решением данной проблемы является создание скрытого высоколегированного n+-слоя на границе коллектора и подложки.

Низкоомный скрытый слой шунтирует расположенный над ним более высокоомный коллекторный слой n-типа и в десятки раз уменьшает

объемное сопротивление коллекторной области между коллекторным переходом и коллекторной контактной областью.

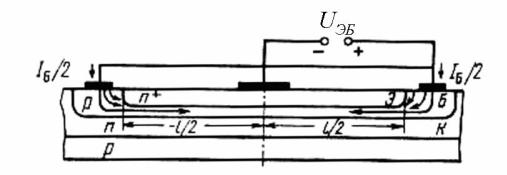

В области средних и больших токов (> 1 мА) существенную роль играет эффект вытеснения тока в эмиттере. При увеличении рабочего тока в транзисторе происходит увеличение плотности тока эмиттера. Напряжение в

любой точке эмиттерного перехода представляет собой разность внешнего напряжения UЭБ и падения напряжения в объеме базы, которое возрастает по мере удаления этой точки от базового контакта (рис. 19.2). В результате напряжение в центральной части эмиттера меньше напряжения у его краев, и край эмиттера приобретает большее прямое смещение, чем середина его площади, значит, внешние области эмиттера будут работать при больших плотностях тока по сравнению с внутренними. Это в свою очередь приводит

к повышению рекомбинационных потерь носителей в области краев эмиттера и уменьшению коэффициента усиления.

Рис. 19.2. Эффект оттеснения эмиттерного тока

378

Для уменьшения этого эффекта необходимо выбирать топологию мощных транзисторов таким образом, чтобы обеспечить максимальное отношение периметра эмиттера к его площади. Для транзистора средней мощности можно использовать две эмиттерные области, включенные параллельно, для мощного транзистора использовать «гребенчатую» структуру, т.е. область в которой эмиттерные и базовые области чередуются

(рис. 19.3).

Для уменьшения сопротивления коллектора также используют семеричную конфигурацию коллектора (рис. 19.3). В этом случае коллекторный ток протекает к эмиттеру с трех сторон, и сопротивление коллектора оказывается примерно в три раза меньше, чем в структуре с одним выводом коллектора. Для конструкции транзистора симметричной конфигурацией облегчается разработка топологии металлической разводки,

так как в ней оказывается возможным часть коллекторной области разместить под окислом, а поверх оксида над коллектором провести проводник к эмиттерной или базовой области.

а) |

б) |

Рис. 19.3. Поперечное сечение (а) и топология (б) биполярного n-p-n

транзистора повышенной мощности с симметричным коллектором и эмиттером гребенчатой структуры

В структуре транзистора, изолированного n-р переходом, помимо основного транзистора существует паразитный р-п-р транзистор. Его эмиттером является базовый слой основного транзистора, базой – коллекторная область со скрытым слоем, а коллектором является подложка.

Рис. 19.4. Схема включения паразитного р-п-р транзистора

379