книги / Проектирование устройств и систем с высокоскоростными соединениями

..pdf

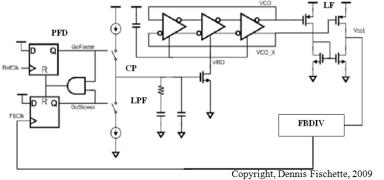

•CP (Charge Pump) – схема зарядовой накачки, преобразующая длительность импульсов фазовой ошибки в аналоговый сигнал тока;

•LPF (Low-Pass Filter) – фильтр нижних частот (контурный фильтр LP – Loop Filter), интегрирующий фазовую ошибку в ви-

де тока в управляющее напряжение для VCO;

•VCO (Voltage Controlled Oscillator) – низкоамплитудный генератор, управляемый напряжением (ГУН);

•LS (Level Shifter) – схема сдвига уровня, усиливающая

выходной сигнал VCO до полного размаха;

• FBDIV (Feedback Divider) – делитель тактовой частоты в обратной связи.

Рис. 1.15. Схема фазовой автоподстройки частоты

PLL использует VCO для генерации тактовой частоты FbClk, следующей за опорной частотой FrefClk. Равновесие PLL наступит, когда фронты FbClk и FrefClk совпадут. Полоса пропускания PFD и LPF находится в пределах 2 МГц. Следовательно, отслеживание джиттера зависит от характера среза и выброса/затухания частотной характеристики LPF. В табл. 1.1 приведена таксономия PLL.

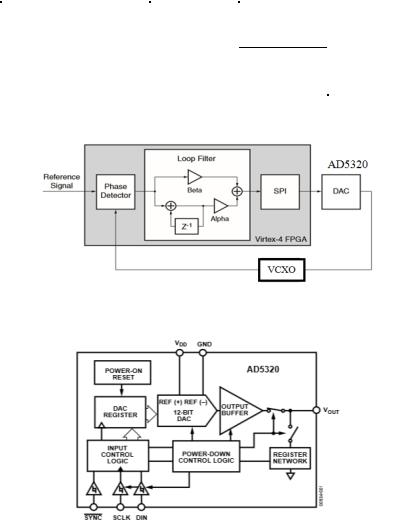

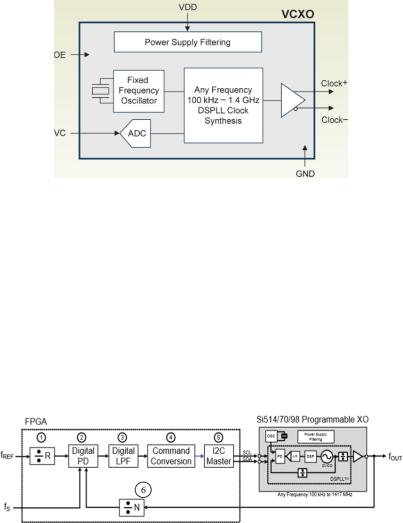

Программируемые ИС, такие как FPGA, в своем составе могут иметь средства для создания PLL. На рис. 1.16 приведена схема DPLL (Digital PLL) на базе FPGA Xilinx Virtex-4 (Justin Gaither. Digital Phase-Locked Loop Reference Design, Application Note: Virtex-4, FPGAs XAPP854) и внешних ЦАП с синхронным

21

интерфейсом SPI (рис. 1.17) и ГУН (VCXO – Voltage Controlled Crystal Oscillator) фирмы Silicon Labs (рис. 1.18).

|

|

|

Таблица 1 . 1 |

||||

|

Виды PLL |

|

|

|

|

|

|

|

|

|

Сигнал |

|

|

|

|

Вид PLL |

PFD |

|

|

LP |

|||

|

ошибки PLL |

|

|||||

|

|

|

|

|

|

||

LPLL (линейная PLL) |

аналоговая |

|

аналоговая |

|

аналоговая |

||

DPLL (цифровая PLL) |

цифровая |

|

аналоговая |

|

аналоговая |

||

ADPLL (полностью циф- |

цифровая |

|

цифровая |

|

цифровая |

||

ровая PLL) |

|

|

программная |

|

|

|

|

SPLL (программная PLL) |

программная |

|

|

программная |

|||

|

|

|

|

|

|

||

|

|

|

|

|

AD5320 |

|

|

|

|

|

|

|

|

|

|

Рис. 1.16. DPLL на базе FPGA Virtex-4

Рис. 1.17. ЦАП Analog Dvices AD5320

22

Рис. 1.18. ГУН фирмы Silicon Labs

На рис. 1.19 приведена схема ADPLL на базе FPGA Altera EP3C25F324 (Introduction to FPGA-based ADPLLs. AN575, Silicon Labs), где обозначено:

1 – делитель опорной частоты;

2– цифровой фазовый детектор;

3– цифровой фильтр нижних частот (LF);

4– формирователь команд для программируемых генерато-

ров Si514, Si570 и Si598 фирмы Silicon Labs;

5– мастер интерфейса I2C;

6– делитель в обратной связи;

fs – частота дискретизации.

Рис. 1.19. ADPLL на базе FPGA Altera EP3C25F324

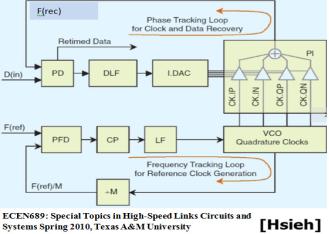

Выделитель тактовой частоты и данных. На вход CDR по-

дается не периодический сигнал, как в PLL, а сигнал последовательных данных. Нарис. 1.20 приведенасхемаCDR, гдеобозначено:

F(rec) и F(ref) – выделенная и опорная тактовые частоты;

23

PD (Phase Detector) – фазовый детектор, ширина выходных импульсов которого пропорциональна разности фаз сигналов

D(in) и F(rec);

CP – схема зарядовой накачки, преобразующая длительность импульсов рассогласования фаз в напряжение;

DLF (Loop Filter) – контурный фильтр (фильтр нижних частот), интегрирующий фазовую ошибку между F(rec) и D(in);

I.DAC – цифроаналоговый преобразователь; PI (Phase Interpolator) – фазовый интерполятор;

: M – делитель тактовой частоты на M в обратной связи; CK.IP, CK.IN, CK.QP, CK.QN – синфазные и квадратурные

составляющие многофазного VCO для PI.

Рис. 1.20. Схема выделения тактовой частоты и данных

PLL в составе CDR генерирует многофазный тактовый сигнал, используемый PI. PI смешивает входные тактовые сигналы с определенным сдвигом фаз для получения наилучшего положения F(rec) относительно входных данных. Например, 5-разряд- ный код, выдаваемый I.DAC (цифровое преобразование сигнала ошибки фазы), представляет на интервале в 90° шаг по смеще-

нию фазы 90°/(25 – 1) = 2,9°.

В отличие от PLL, CDR не может отслеживать высокочастотный джиттер.

24

1.3. FPD-LINK – ПРИМЕР РЕАЛИЗАЦИИ СКОРОСТНОГО ВВОДА-ВЫВОДА

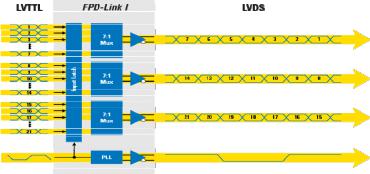

В 1996 г. National Semiconductor разработала открытый стандарт Flat Panel Display Link (FPD-Link) скоростного цифро-

вого видеоинтерфейса для связи узла обработки графической информации с устройствами отображения информации (LCD, TFT-дисплеи) [3]. FPD-Link использует LVDS-драйверы для передачи 18 бит сырого RGB-видеосигнала. Драйверы LVDS передают видеоданные по трем витым парам, по четвертой паре передается синхросигнал (синхронизация от источника)

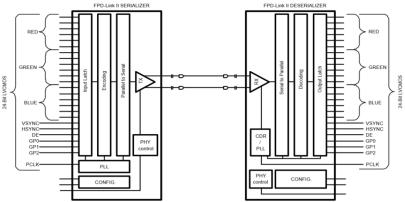

В 18-битных RGB-приложениях каждый из трех цветов кодируется 6 битами плюс бит для горизонтальной синхронизации, бит для вертикальной синхронизации и бит для сигнала разрешения. Получается 21-разрядный сигнал в каждом такте синхронизации. Тогда если тактовая частота равна 50 MГц, то каждый из трех LVDS каналов FPD-Link должен передавать данные на частоте 350 MГц. Таким образом, общая скорость передачи по трем каналам будет 1050 Mбит/c. На рис. 1.21 представлена схема сериализации 21-разрядного несимметричного видеосигнала, принятого в FPD-Link. На рис. 1.22 приведена блок-схема современного сериализатора и десериализатора FPD-Link II фирмы Texas Instruments [4] для 18-битного RGB-дисплея. Это вариант передачи с самосинхронизацией. PCLK = 5…43 MГц, длина витой пары до 10 м.

Рис. 1.21. Схема сериализации FPD-Link

25

Рис. 1.22. Блок-схема FPD-Link II для 18-битного RGB-дисплея

1.4. ВЫСОКОСКОРОСТНОЙ (МУЛЬТИГИГАБИТНЫЙ) ВВОД-ВЫВОД

Для повышения качества функционирования устройств разработчики стремятся уменьшить такие параметры, как число выводов компонент, EMI, стоимость, и повысить эффективность кроссплат. Поэтому они все больше обращаются к технологии высокоскоростного ввода-вывода, главным преимуществом которой является скорость. Для обмена данными между микросхемами, печатными платами или блоками на сегодня ничто не может конкурировать с высокоскоростными последовательными соединениями – скорость от 1 до 12 Гбайт/с и нагрузка от 0,8 до 10 Гбайт. Наряду с малым числом выводов устраняются и проблемы SSO. Мульти-

гигабитные трансиверы MGT (Multigigabit Transceiver), другое название SERDES (Multigigabit Serializer/Deserializer) – это выбор разработчиков в случае, когда необходимо быстро передать большой объем данных.

1.4.1. Преимущества и недостатки высокоскоростного ввода-вывода

Рассмотрим преимущества высокоскоростного ввода-вывода: 1. Максимальный поток данных. Некоторые большие программируемые логические интегральные схемы (FPGA) содер-

26

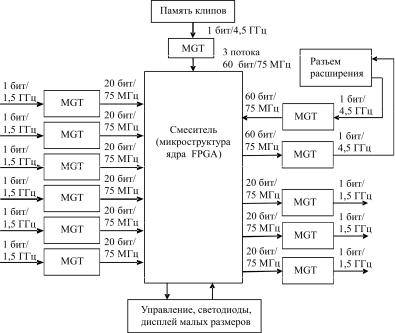

жат 20 или более 10 Гбайт MGT с общей полосой пропускания 200 Гбайт/с. На рис. 1.23 приведена реализация смесителя видеопотоков высокого разрешения (20 бит/75 МГц): 6 входных потоков и 3 выходных потока к другим микросхемам, 3 входных потока и 3 выходных потока на разъем расширения, 3 входных потока из памяти клипов.

Рис. 1.23. Смеситель видеопотоков высокого разрешения по технологии SERDES

2. Число выводов. Число выводов является первой проблемой, которая возникает, когда хотят ввести и вывести большое количество данных из микросхемы на печатную плату. Число выводов всегда ограничено. Хотя тенденция к постоянному увеличению сохраняется, их никогда не хватает. В табл. 1.2 приведены результаты оценки числа выводов для последовательного и параллельного вариантов реализации смесителя видеопотоков высокого разрешения.

27

|

|

|

Таблица 1 . 2 |

Сравнительная оценка числа выводов |

|||

|

|

|

|

Наименования выводов |

Направление |

Параллельный |

Последовательный |

Входы 1–6 |

Вх. |

120 |

12 |

Память клипов |

Вх. |

60 |

2 |

Входы расширения |

Вых. |

60 |

2 |

Выходы расширения |

Вх. |

60 |

2 |

Выходы 1–3 |

Вых. |

60 |

6 |

Управление/статус |

Вх. |

48 |

48 |

Управлениесветодиодами |

Вых. |

12 |

12 |

Управление/статус |

Вых. |

52 |

52 |

LCD-драйвер |

Вых. |

48 |

48 |

Всего |

|

520 |

184 |

Время проектирования печатной платы и ее стоимость сильно возрастают, когда используется большое число выводов. Оно также очень важно для выбора соединителя для кабеля. Использование всех выводов микросхем в корпусе типа BGA (Ball Grid Array) может оказаться сложной задачей при разводке печатной платы.

3.SSO. Разработчик должен учитывать параметр SSO, когда использует параллельные несимметричные соединения. При одновременном переключении большого количества сигналов возникает значительный шум в общем проводе («земля»). Разработчик для решения проблемы SSO может использовать симметричные линии связи, но это удвоит число выводов.

4.EMI. Высокоскоростное последовательное соединение обычно генерирует меньшее электромагнитное излучение, чем медленная многопроводная шина. Это связано с высокой целостностью гигабитного сигнала.

5.Стоимость. Использование MGT часто приводит к меньшей стоимости всей системы. Меньшая по размерам и более дешевая упаковка ИС, соединители с меньшим количеством контактов делают более легкой разработку печатной платы.

6.Предопределенные протоколы. Еще одно достоинство MGT связано с наличием предопределенных протоколов и стандартных интерфейсов от Aurora до XAUI и их решений для раз-

личных нужд.

28

Рассмотрим недостатки высокоскоростного ввода-вывода: 1. Необходимо обращать внимание на вопросы, связанные с целостностью сигналов. Некоторые разработчики говорят

о 90%-ном уровне ошибок в их первых проектах с использованием MGT. Чтобы улучшить положение, возможно, придется выполнять аналоговое моделирование и использовать более сложные схемы обхода.

2.Могут увеличиться расходы на печатную плату в связи

снеобходимостью согласования линий связи, использования высокоскоростных разъемов и кабелей.

3.Цифровое моделирование сталкивается со сложностью схем и малой временной базой сигналов.

1.4.2. Использование высокоскоростного ввода-вывода

1.Взаимодействие между интегральными микросхемами на печатной плате в основном происходило в параллельном виде, так как необходимое количество логики для создания сериалайзера/десериалайзера намного превосходило количество освобождающейся логики в результате уменьшения числа выводов. С переходом на глубокосубмикронные технологии огромное количество логики стало размещаться на малой площади кристалла. Поэтому SERDES удалось включить в состав микросхемы за небольшую плату. Это привело к снижению числа выводов, а значит, к уменьшению и удешевлению корпуса ИС и улучшению SSO (меньше выводов, дифференциальные сигналы). Также уменьшилось число слоев печатной платы, потребление энергии.

2.Взаимодействие между печатными платами через кросс-

плату. Большинство протоколов параллельных шин подошло к черте, за которой добавление новых разрядов данных физически невозможно из-за ограничения числа выводов разъемов. Расфазировка тактового сигнала и расфазировка данных, время нарастания и спада сигналов, джиттер ограничивают возможности увеличения тактовой частоты. Удвоенная скорость передачи может помочь, но она часто требует симметричной передачи сигналов, что значительно увеличивает число выводов. Перекре-

29

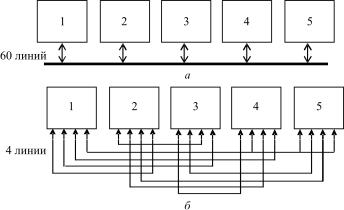

стные помехи в параллельных шинах с трудом поддаются управлению. Альтернативой является последовательная кросс-плата, обеспечивающая индивидуальные дифференциальные связи каждой платы с каждой. Рис. 1.24 иллюстрирует параллельную и последовательную организацию кросса.

Наиболее важным различием между параллельным и последовательным кроссом является метод доступа к пропускной способности. В параллельном кроссе, когда один узел передает, остальные узлы принимают и блокируют передачу. Все узлы разделяют доступную полосу пропускания. В случае последовательных шин каждый узел имеет индивидуальную линию с каждым из остальных узлов. Фактически все узлы одновременно взаимодействуют друг с другом. Преимущества такого кросса состоят в следующем:

•высокая полоса пропускания;

•уменьшенное число выводов;

•определенная полоса пропускания между парой узлов;

•встроенность необходимых решений в SERDES;

•облегченная поддержка протоколов.

Рис. 1.24. Параллельное (а) и последовательное (б) соединение плат

3. Взаимодействие между блоками. Неверным является представление о том, что высокоскоростное взаимодействие между блоками невозможно без оптического волокна. Много свя-

30