- •1Двоичные переменные и двоичные сигналы. Цифровые устройства и их параметры.

- •2. Двоичные коды и операции над ними.

- •3. Регистры. Устройства с наличием отключенного состояния выходов.

- •4. Постоянные и оперативные запоминающие устроства.

- •5. Структура простейшей микропроцессорной системы.

- •6. Структура центрального процессора.

- •7. Структура команды и способы адресации.

- •8Система команд. Команды пересылки.

- •10Система команд. Команды логических операций.

- •12. Структура микроконтроллера avr.

- •13. Организация памяти.

- •N – устанавливается в 1, если старший 7ой байт результата равен 1. И 0, если 0.

- •14. Порты ввода-вывода.

- •15. Система команд. Команды пересылки.

- •16. Система команд. Команды логических операций.

- •16. Система команд. Команды логических операций.

- •17. Система команд. Команды арифметических операций.

- •18. Система команд. Команды битовых операций.

- •19. Система команды. Команды передачи управления.

- •20. Модуль ацп.

- •21. Система прерываний.

- •22. Таймеры-счетчики.

- •23. Интерфейс spi.

- •24. Модуль usart.

23. Интерфейс spi.

Модуль SPI служит для организации последовательного интерфейса, для связи микроконтроллера с различными внешними устройствами. Ими могут быть АЦП, ЦАП, и т. д.

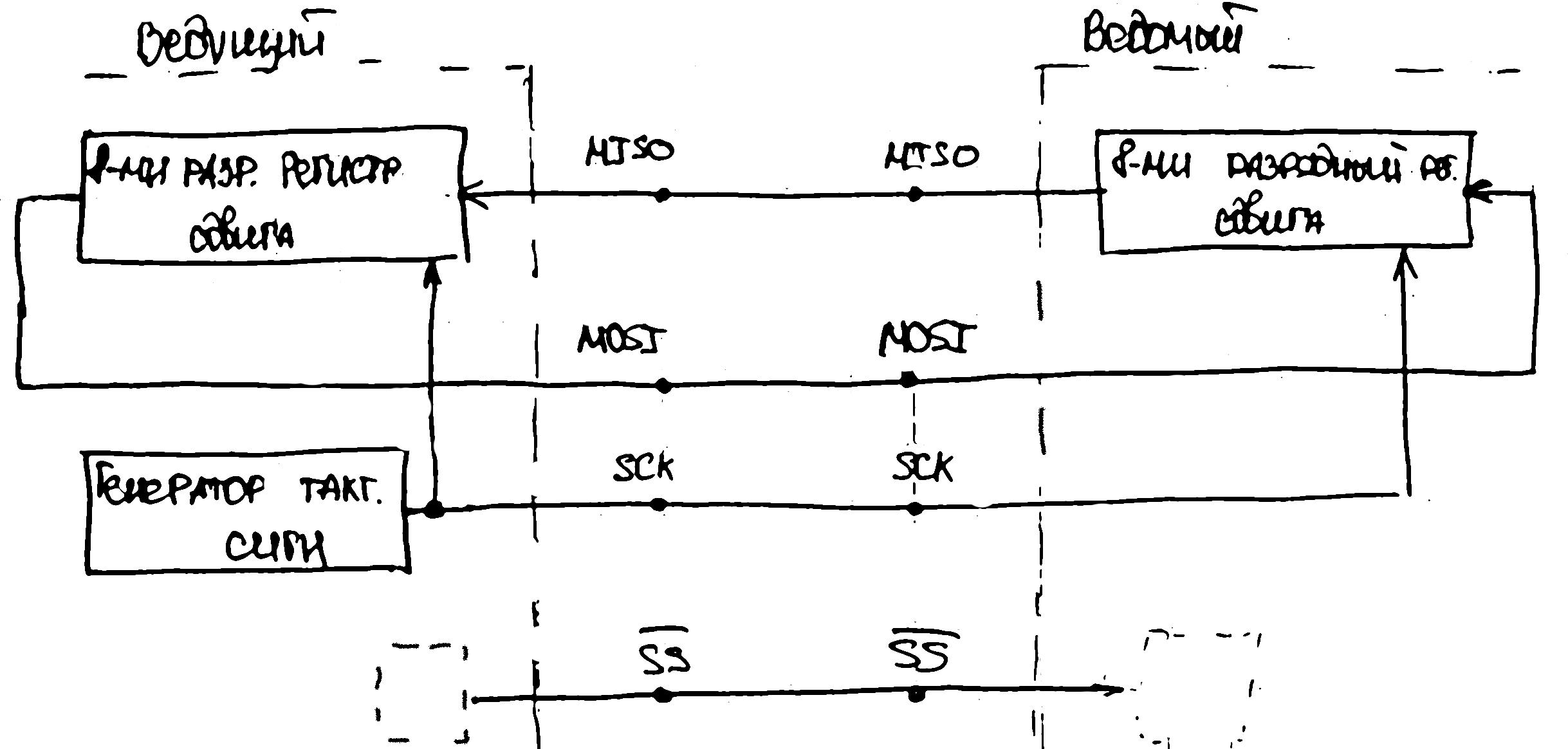

Принцип работы интерфейса SPI объясняется следующим рисунком:

Для организации интерфейса требуется четыре линии связывающие устройства, между которыми имеется связь. Выделяют две стороны: ведущая (микроконтроллер) и ведомая (ЦАП, АЦП).

SS – управляющая линия.

Ведущая линия всегда является источником тактового сигнала и сигнала SS.

Работа интерфейса SPI.

Сдвиговые регистры загружают информацию о данных, которые необходимо передать, причем ведущая сторона загружает в регистры данные, которые необходимо передать ведомому и наоборот.

После загрузки данных в регистр ведущего начинается процесс обмена данными между ведущей и ведомой сторонами. Для этого ведущая сторона формирует 8 импульсов синхронизации, которые поступают на регистр сдвига ведущей стороны и по линии SCK поступают на регистр сдвига ведомого. По каждому импульсу сдвига в регистрах ведущей и ведомой сторон осуществляется сдвиг информации на один разряд.

Сдвиг в регистрах осуществляется влево, при этом старший разряд регистра сдвига ведущей стороны по линии MOSI поступает в младший разряд регистра сдвига ведомой стороны.

После того как сформировалось 8 импульсов синхронизации содержимое регистра ведущей стороны окажется в регистрах ведомой. Содержимое регистра ведомой стороны - в регистрах ведущего.

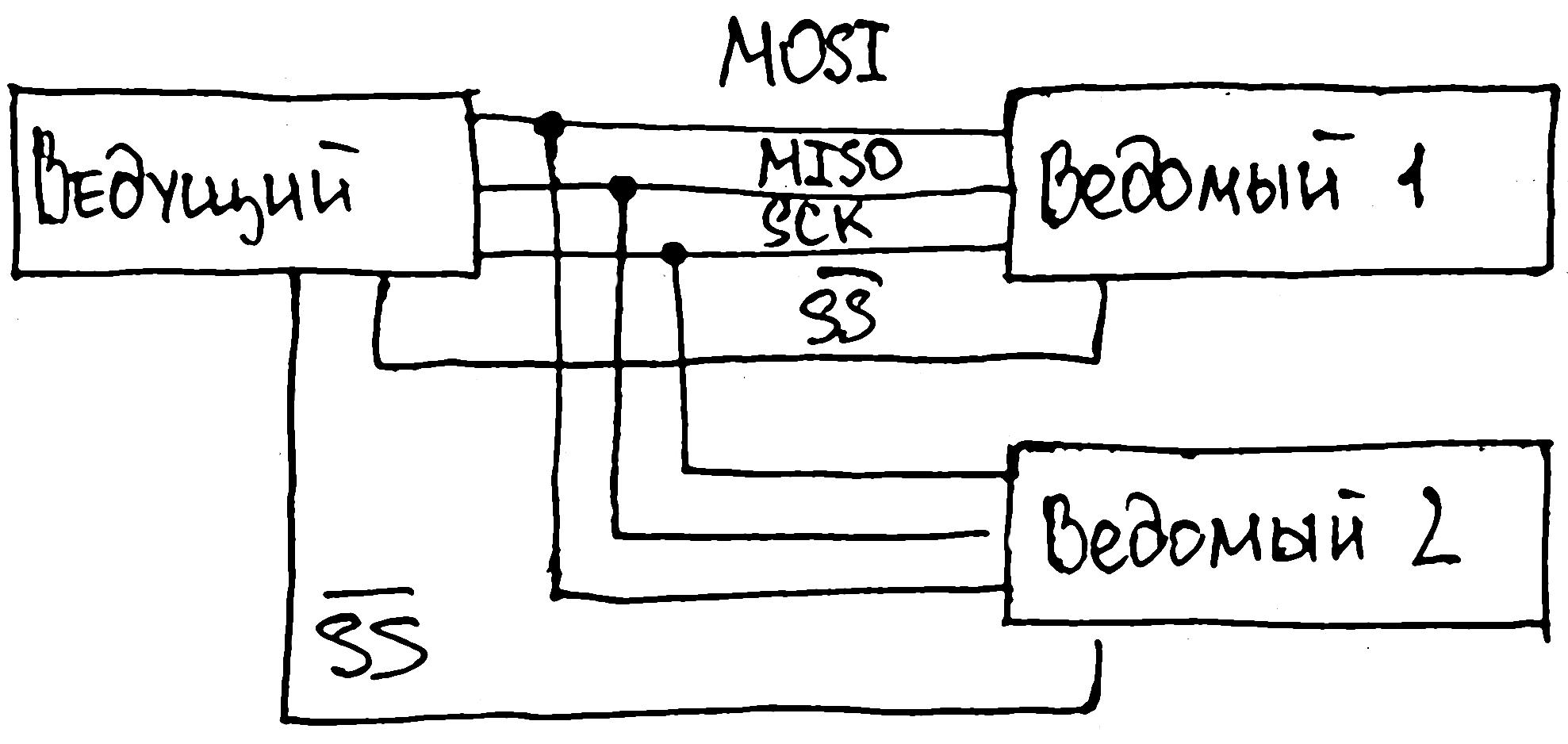

При организации интерфейса SPI могут участвовать несколько ведомых и одна ведущая сторона.

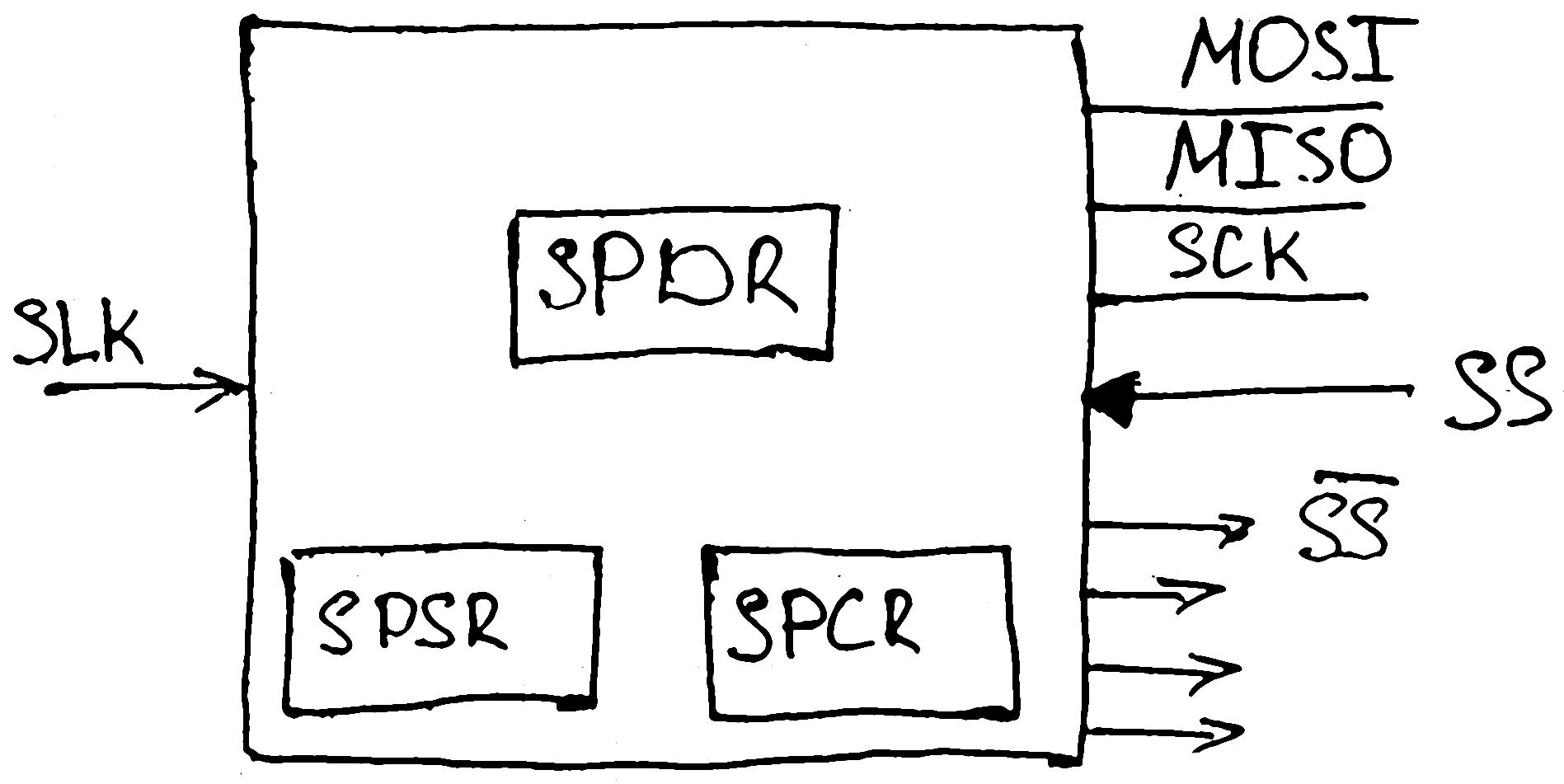

Модуль SPI.

SPDR – регистр данных. В него помещаются данные, которые необходимо передать и по окончанию цикла обмена помещать принятые данные.

SPCR – регистр управления модулем.

SPSR – регистр состояния модуля.

Если она настроен как ведущая сторона, то она является источником синхронизации SCK.

Если ведомая сторона, то по линии SCK принимает 8 импульсов для синхронизации.

Если ведущая, то модуль является источником сигнала SS. Сигнал для ведомых посылается по какому-либо порту.

В SPCR имеются биты:

- разрешенные прерывания от SPI (событие прерывания связано с циклом обмена).

- включение модуля SPI. При установке в «1» - включен; «0» - выключен.

- порядок передачи данных (с младшего или старшего).

- выбор ведущего (ведущий или ведомый).

- полярность тактового сигнала.

- фаза тактового сигнала.

- «2 бита» скорость передачи (деление частоты).

SPSR:

- разряд деления частоты (совместно с двумя битами SPCR).

- флаг прерывания «1» при разрешении обмена.

- флаг конфликта записи.

24. Модуль usart.

Модуль USART предназначен для организации последовательной передачи данных. Модуль синхронно-асинхронной передачи данных. В случае асинхронной передачи данных используются две линии (TxD и RxD). По TxD данные передаются, по линии RxD они принимаются. Прием и передача независимы.

В случае синхронной передачи используются линии TxD, RxD и XCK – линия синхронизации. Прием и передача не зависят друг от друга (XCK представляет собой последовательность передачи импульсов, служат для улучшения передачи).

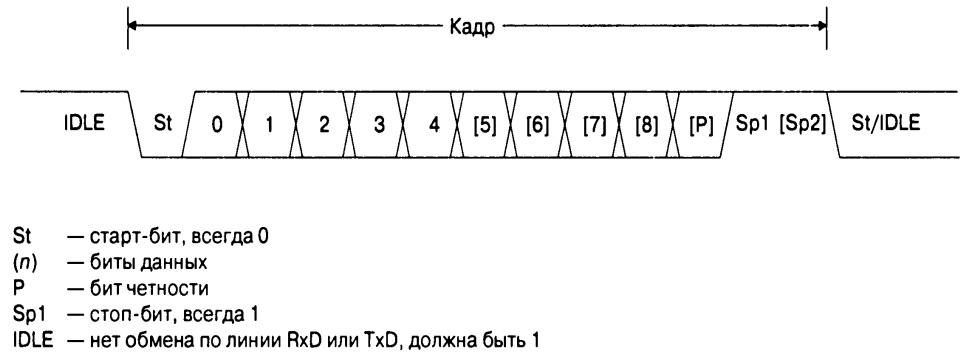

Данные по интерфейсу USART передаются кадрами. Структура кадра имеет следующий вид:

[ ] – необязательные кадры.

При отсутствии первый сигнал.

После стартового бита передаются 5÷9 бит. Далее передается бит четности. После окончания кадра 1 или 2 стоповых бита.

UCSRA:

- имеется флаг завершения приема. Устанавливается в «1», если в буферном устройстве приемника имеются непрочитанные данные, установка флага в «1» может вызвать прерывание, если оно разрешено.

- флаг завершения передачи. «1» - если передатчик передал весь и в буферном регистре нет новых данных. Может вызвать прерывание, если оно разрешено.

- флаг опустошения регистра данных. «1» - если данные, помещенные в буферный регистр передатчика переданы в передатчик. Может вызвать прерывание, если оно разрешено.

- флаг ошибки кадрирования. «1» - если обнаружен неверный стоповый бит. Не вызывает прерываний.

- флаг переполнения. «1» - если приемник принимает информацию, а буферное устройство приемника заполнено.

- флаг ошибки контроля четности. Бит четности паритета устанавливается в «1» или «0» таким образом, чтобы суммарное количество единиц в информационной части кадра вместе с битом паритета было четным.

Структура модуля USART:

UBRRH

UBRRL

Устройство

синхронизации

Буферное

устройство приемника

Приемник

Буферный

регистр передатчика

Передатчик

UCSRA

UCSRB

UCSRC

XCK

RxD

TxD

CLK

ШД

UCSRB:

- разрешение прерывания по завершению приема.

- разрешение прерывания по завершению передачи

- разрешение прерывания при опустошении буферного регистра передатчика.

- разрешение приема.

- включение/выключение передатчика.

- бит, определяющий формат кадра.

UCSRC:

- (2 бита) + 1 из UCSRB определяют формат кадра 5, 6, 7, 8 или 9 бита в кадре.

- бит, определяющий четность и нечетность контроля.

- бит, определяющий количество стоповых битов.