книги из ГПНТБ / Дроздов Е.А. Многопрограммные цифровые вычислительные машины

.pdf— прямым током базы /б. Пр открытого транзистора и, следова тельно, коэффициентом насыщения К„.

Величины Ек и Есм должны быть такими, чтобы напряжения Uэ. в, Дк.э и Uu.б не превышали предельно допустимых. Ток /к. „0м также не должен превосходить предельно допустимый /к. доп. Для повышения надежности и долговечности транзисторов рабочие токи и напряжения выбираются на 30—50% меньшими максимально до пустимых.

Входные характеристики транзистора и выбранные £ к и Есм позволяют ориентировочно оценить требуемую амплитуду выход ного напряжения схемы И. Это в свою очередь дает возможность выбрать величину питающего напряжения Еп.

Пусть, например, для построения элемента используется тран зистор, имеющий допустимое напряжение Дк.э.доп=+5 в и оста точное напряжение на коллекторе в режиме насыщения UK.э. Нас=

=0,1 ч- 0,5 в. Предположим, что с учетом данных выше рекоменда ций выбрано пониженное напряжение коллекторного питания Ек=

=+3 в. В этом случае без учета сопротивления нагрузки ампли

туда переключаемого выходного напряжения Д«Пых= Дк— Ul{,a,mc =

= (2,9ч-2,5) б.

Согласно приведенным в § 4.4 рекомендациям следует выби рать £„= (2 = 5)А«вых. В рассматриваемом примере Еп должно быть не менее 5—6 в, что в два раза превосходит Ек. Этим объяс няется то обстоятельство, что в диодно-транзисторных схемах для питания диодных схем и транзисторных усилителей часто прихо дится использовать источники различных номиналов напряжений.

Напряжение Еи совместно с резистором Ru образуют источник тока

|

/ R = As. пР + А? > |

(4.Ю ) |

||

|

хи |

г |

см |

|

где /б. Пр — прямой |

ток базы, |

определяющий режим работы от |

||

крытого |

транзистора |

Т; |

Есм от источника Е„. |

|

/„ — ток, протекающий |

к |

источнику |

||

К СМ

При выбранном 1к.ном прямой ток базы /е.пр определяет степень насыщения транзистора. Для уменьшения влияния нестабильности коэффициента усиления транзистора и управляющего напряжения на базе желательно выбирать ток базы возможно большей вели чины. Однако при этом растет степень насыщения транзистора, определяемая коэффициентом насыщения Ки.

|

|

Кп = |

^ б * пр |

> |

(4.11) |

|

|

|

"7 |

|

|||

|

|

|

'к.ном |

|

|

|

где |

В — коэффициент |

усиления |

по |

току в схеме |

с общим эмит |

|

тером. |

|

|

|

|

|

|

В |

Степень насыщения влияет на время выключения транзистора. |

|||||

схемах, в которых |

транзисторы |

работают в |

насыщенном ре- |

|||

120

жиме, как в данном случае, коэффициент насыщения Ки выбирают в пределах 1,5—5. Тогда

|

*Н Лс. |

(4.12) |

^ б . П р |

в и |

|

|

|

Как показано на рис. 4.19, время закрывания t3акр транзистора слагается из времени рассасывания tp неосновных носителей в базе и времени спада t c коллекторного тока в активной области, т. е.

г'закр = ^р+^с. |

Это |

суммарное |

время |

1 6 . |

|||||

не |

должно |

превышать |

требуемое |

h. пр |

|||||

время г'тр переключения выходного |

0 - |

||||||||

напряжения. |

В |

рассматриваемой |

|||||||

схеме |

управление |

закрыванием |

Irf. одр |

||||||

транзистора осуществляется с по |

|

||||||||

мощью |

обратного тока |

базы / б. обр, |

|

||||||

который при сигнале низкого уров |

|

||||||||

ня в точке б |

протекает |

через RCm |

|

||||||

к клемме —Есм. Поэтому |

поглоти |

|

|||||||

тель тока, состоящий из R Cm и |

источ |

|

|||||||

ника —Есм, должен быть рассчитан |

|

||||||||

так, |

чтобы обеспечивалась |

требуе |

Рис. 4.19. Эпюры входного и вы |

||||||

мая |

скорость рассасывания |

неос |

|||||||

новных |

носителей |

в |

базе |

и закры |

ходного токов транзистора |

||||

вания транзистора.

Таким образом, в данной схеме открытый и закрытый режимы работы транзистора обеспечиваются разными источниками пита ния и разными цепями формирования токов /б.пр и /б. обр-

К входу 3 могут подключаться дополнительные диодно-рези сторные вентили, аналогичные имеющемуся в схеме элемента. Если открыт основной вентиль схемы и открываются дополнительные вентили, то прямой ток базы /б.пр транзистора Т в общем случае будет расти в соответствии с зависимостью

б . п р • I ~ |

(4.13) |

|

где /=1, 2, 3 ...—общее число открытых вентилей на входе транзи стора.

В соответствии с этим будет увеличиваться и коэффициент на сыщения Ка транзистора согласно (4.11). Например, пусть /р =

= 1,2 |

ма, /„ =0,2 |

да и /=2н-4, |

тогда |

в соответствии |

с (4.13) |

|

ХМ |

|

ма. Предположим, что / к.ноы= |

||

прямой ток базы /б.Пр будет 2 ,2 -т-4,6 |

|||||

= 10 |

ма и В = 20 ч-40. |

Тогда по формуле |

(4.11) получим, |

что в за |

|

висимости от коэффициента усиления транзистора В и количества открытых на входе вентилей коэффициент насыщения Ки может меняться в пределах 4,4— 18,4.

При неизменном /б.обр большее насыщение приведет к увеличе нию времени рассасывания неосновных носителей в базе транзи

121

стора. В результате суммарное время /закР может превысить тре буемое время tTp. Поэтому данное обстоятельство является при чиной ограничения, накладываемого на допустимое количество I

одновременно открытых входных вентилей. |

последующей схемы |

||

При открытом транзисторе Т' ток /р |

|||

переключается в его коллекторную цепь. Этот ток, |

являющийся |

||

по сути дела током нагрузки / и, |

равен |

|

|

£„■ |

Уд1пр — к.эТ' |

|

(4.14) |

/н = ' |

|

|

|

|

|

|

|

Сумма п токов / ц, текущих к коллектору транзистора, совмест |

|||

но с током /R, = j r k ) не должна превышать |

/к.иом- |

Таким обра< |

|

зом, |

|

|

|

Лс. ном — Ы |

|

(4.15) |

|

я < |

|

|

|

У диодно-транзисторных интегральных схем типа |

И — ИЛИ — |

||

НЕ с простым однотранзисторным инвертором, подобных изобра женной на рис. 4.16, а, коэффициент объединения m по входам И обычно равен 6—8, а коэффициент объединения по входам ИЛИ составляет 3—4. Усилитель-инвертор оказывается в состоянии управлять четырьмя — шестью входами вентилей, аналогичных имеющемуся в схеме данного элемента.

Среднее время задержки ^зхр распространения сигналов в эле ментах, у которых m, I и п не превышает указанные выше пре делы, обычно не больше 50—70 нсек, а средняя рассеиваемая мощ ность ЛСр модуля типа Ml равна 20—30 мет. Для указанных на рис. 4.16 номиналов питающих напряжений сопротивления рези

сторов Rh=(24-4) |

kom\ |

Rk= (0,75-ь 1) ком\ RCM=(3-r-10) |

ком. |

При построении |

из |

таких элементов тактированных |

сложных |

логических схем, в которых моменты продвижения информации от мечаются тактовыми сигналами, частоты следования последних обычно не превышают 0,5—1 Мгц.

§4.6. Транзисторные логические элементы

Влогических элементах такого типа транзисторы используются не только как усилители сигналов, но и как простейшие ключи, комбинации соединений которых реализуют различные логические

функции. Быстродействие транзисторных элементов определяется в основном типом используемых транзисторов и способом их вклю чения в схемах. Существует много вариантов транзисторных логи ческих схем, имеющих различные скорости переключения. У наи более быстродействующих из них задержки распространения сиг налов составляют единицы наносекунд.

Одно из основных достоинств транзисторных логических схем заключается в том, что хорошие формирующие свойства транзи

122

сторов позволяют почти полностью, а в ряде случаев и совсем исключить всевозможные индуктивно-емкостные корректирующие цепи, оставив из пассивных компонентов только нагрузочные ре зисторы. Такие элементы хорошо поддаются микроминиатюри зации.

В настоящее время промышленностью выпускаются различные варианты гибридных и монолитных интегральных схем. Рассмо трим принципы построения и работы основных типов таких микро схем.

Транзисторные логические схемы с непосредственными связя ми (ТЛ НС-схемы). Поиски способов построения наиболее простых полупроводниковых схем, удобных для изготовления по интеграль

У, г- Зь +0,8в U0J * + 0,36

Ш

% |

. » а Г |

ч ! |

и0 I fy[j] |

~1_ |

|

RAЛ |

~ г |

|

- щ |

|

|

|

|

|

|

||

/ Р л п |

|

| h.np^ |

( Р л т з |

|

|

|

|

|

|||

JL |

± |

Л . |

Рис. 4.20. Последовательная |

цепь непосредственно связанных |

транзисторов |

ной технологии, привели к созданию так называемых транзистор ных схем с непосредственными связями. В такой схеме (рис. 4.20) коллектор одного транзистора соединяется непосредственно с ба зой другого без каких-либо переходных элементов. Исследования свойств транзисторов показали, что при малых напряжениях кол лекторного питания (например, для кремниевых в пределах от +3 до +5 в) ключевой режим работы транзисторов последовательно включенных инверторов достаточно просто может быть обеспечен лишь за счет разницы в падениях напряжения в насыщенном ре жиме на переходах база — эмиттер и коллектор — эмиттер. На пример, когда прямым током базы /б.Пр транзистор Т1 открыт и находится в режиме насыщения, остаточное напряжение £/„.н на его коллекторе недостаточно для открывания транзистора Т2.

Рассмотрим совмещенные на одном графике (рис. 4.21) харак теристики IK=f (UK) и /б = /(^б) транзистора, включенного по схе ме с общим эмиттером. На графике построена нагрузочная прямая

—iLn—- для резистора RK, проведенная из точки Ек. Она Пересе-

кает характеристику /K=f(f/„) в точке а. Из анализа характери стик следует, что при полностью открытом транзисторе, работаю щем в области насыщения, остаточное напряжение на его коллек торе UK.n меньше базового напряжения отсечки Uб.0тсЭто озна чает, что, подавая сигнал непосредственно с коллектора открытого транзистора на базу аналогичного другого транзистора, можно

123

надежно удерживать последний в закрытом состоянии. При закры вании транзистора (например, Т2 на рис. 4.20) напряжение на его коллекторе повышается и, дойдя до величины Uб.отс, начинает от крывать следующий управляемый им транзистор ТЗ. Ток, проте кающий через резистор Rk, переключается в базу управляемого транзистора и вводит его в режим насыщения.

При открывании транзистора нагрузки ТЗ ток коллектора за крывающегося транзистора Т2 начинает зависеть не только от из менения его внутреннего сопротивления. Сказывается шунтирую-

Рис. 4.21. Совмещенные входная и выходные характеристики транзистора

щее действие входного сопротивления нагрузки. С ростом прямого

тока базы транзистора ТЗ коллекторный ток |

транзистора Т2 на- |

|

чинает уменьшаться быстрее, т. е. теперь / к = |

р |

_ |

—^ |

—- — /б. пр.Дан |

|

ное обстоятельство отражено на совмещенных характеристиках из ломом нагрузочной линии и более крутым ее спадом при UK> >Т^б.отсПри вхождении транзистора ТЗ в режим насыщения оста-> точное напряжение на коллекторе закрывшегося транзистора Т2 фиксируется на некотором уровне UKмакс=^б.н, где Uб.н— напря жение на базе транзистора в режиме насыщения.

Схема на рис. 4.22, а с параллельно включенными кремниевыми транзисторами Т1 — ТЗ типа п — р — п реализует логическую опе

рацию И — НЕ |

для сигналов низкого уровня |

напряжения (U0) и |

||||

ИЛИ — НЕ |

для |

сигналов высокого уровня |

(Ui). Когда |

на всех |

||

трех входах |

низкие напряжения |

(uxi = их2 ~ и х3 = U0) , |

то |

все тран |

||

зисторы закрыты и напряжение |

ивых имеет высокий |

уровень. По |

||||

124

этому если низкое напряжение на входах и выходе соответствует коду 1, то выходной сигнал связан с входными сигналами логи

ческим соотношением Р=Х\Х2х3, где Р — ыВЫх, *i — их1 и т. д. При подаче иа любой из трех входов сигнала высокого уровня (£/О соответствующий этому входу транзистор открывается и на вы ходе напряжение уменьшается. Следовательно, если на входах и выходе коду 1 соответствует высокий уровень напряжения, то схема

реализует логическую операцию Р = х{ \/ x2\Jх 3 (рис. 4.22,6). ■Обычно на практике такого рода схемы рассматривают именно

как элементы ИЛИ — НЕ для сигналов высокого уровня. Когда анализируются вентильные схемы, реализуемые на таких элемен-

Рис. 4.22. Типовой элемент ИЛИ — НЕ, используемый |

в транзисторных схе |

||

|

мах с непосредственными связями: |

|

|

а — принципиальная схема; 6 — условное обозначение схемы, |

реализующей |

функцию |

|

P = .v, v |

в — условное обозначение схемы, реализующей функцию |

Р = x tXiX% |

|

тах (ИЛИ — НЕ), логические связи между входами и выходами

записывают для инверсий переменных, т. е. Р = х \Jy=xy. Функцио нальной схеме на рис. 4.22, в, рассматриваемой как схема совпаде

ния для лт, х2 и *з, будет соответствовать логическая связь Р =

= х 1 х2х3.

При расчете схемы прямые базовые токи открытых транзисто ров выбираются таким образом, чтобы транзисторы находились в режиме насыщения и на их коллекторах было бы остаточное на пряжение UK,н, меньшее напряжения отпирания (С/б.отс) управляе мых транзисторов. Тогда все последующие транзисторы, соединен

ные с коллекторами открытых |

транзисторов, |

будут закрыты. |

|

У кремниевых |

транзисторов обычно t/K.H~0,l |

в, а Нб.Отс~0,7н- |

|

-5-0,8 в. |

на коллекторах |

запертых транзисторов стремятся |

|

Напряжения |

|||

к +ЕК, но, как было отмечено выше, этому препятствуют базовые токи следующих открытых транзисторов. Эти напряжения зависят от соотношений величин резисторов RK и сопротивлений открытых переходов база — эмиттер. В схемах на кремниевых транзисторах они обычно составляют 0,85—1,5 в.

125

Нагрузочные резисторы RK рассчитываются таким образом, чтобы при закрытом транзисторе обеспечивалась выдача тока, до статочного для поддержания в открытом состоянии п транзисторов нагрузки.

Интегральные монолитные схемы с непосредственными связями имеют достаточно высокое быстродействие. Средние задержки рас пространения /З.ср в таких элементах составляют 10—25 нсек. При малых напряжениях источников питания они потребляют сравни тельно немного энергии. Для указанного выше диапазона Дер их средние мощности рассеяния Рср соответственно находятся в пре делах 10—2 мет.

У|

щJ

Рис. 4.23. Резисторно-транзисторная логическая схема

Однако, несмотря на такие показатели, схемы с непосредствен ными связями имеют ограниченное применение. Объясняется это в первую очередь недостатками, являющимися следствием чрез мерно высоких требований к параметрам транзисторов, составляю щих такие схемы.

Для непосредственного подключения к выходу одной схемы не скольких входов других схем особенно необходимо, чтобы входные характеристики транзисторов имели малые разбросы (в пределах нескольких процентов). В противном случае прямые базовые токи Iб.пр, текущие из одного управляющего коллекторного узла к па раллельно включенным базам открытых транзисторов, будут рас пределяться неравномерно. Это может привести к неустойчивой работе транзисторов одних инверторов и к чрезмерному перенасы щению других. Кроме того, при этом снижается нагрузочная спо собность управляющих инверторов из-за чрезмерного поглощения тока транзисторами, имеющими малые входные сопротивления и, следовательно, более низкие напряжения на базах.

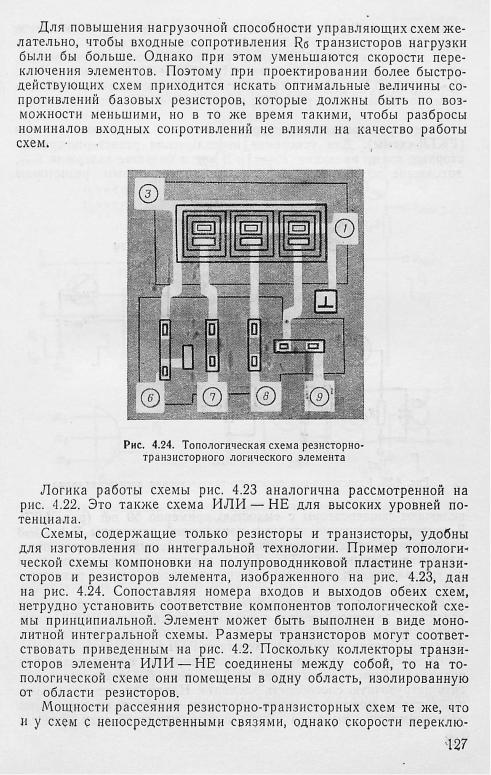

Резисторно-транзисторные логические схемы (РТЛ-схемы). Чтобы уменьшить разбросы входных сопротивлений инверторов, в базовые цепи их транзисторов включают резисторы Ra (рис. 4.23). Сопротивления этих резисторов могут быть от нескольких десят ков ом до 1—1,5 ком.

126

чения меньше. Время задержки распространения £а.Ср у элементов типа РТЛ бывает от 35—50 до 100 и более наносекунд.

У элементов с ^.ср^ЮО нсек средние мощности рассеяния Рср

обычно не превышают 1—2 мет. При |

£'к= + 3 в уровни сигналов |

U0= + (0,2-т-0,4) в, U\ = + (1,2ч-2,2) в. |

Нагрузочные способности |

схем, подобных схеме рис. 4.23, составляют 4 —8 входов аналогич

ных схем.

Резисторно-конденсаторно-транзисторные логические схемы (РКТЛ-схемы). Для ускорения переключения резисторно-транзи сторных схем, имеющих ЯСр=1-=-2 мет и большие задержки /З.ср, доходящие до 500 нсек, параллельно высокоомным резисторам

Рис. 4.25. Резнсторно-конденсаторно-транзисторная логическая схема

включают конденсаторы с емкостью примерно 50 пф |

(рис. |

4.25). |

В моменты изменения входных напряжений резисторы |

Rpl |

— Re3 |

шунтируются этими конденсаторами, тем самым форсируя |

пере |

||

ключение транзисторов Т1— ТЗ. В статическом |

состоянии |

связи |

|

с управляющими схемами |

осуществляются |

через резисторы |

|

Rel—ИбЗ. |

ускоряющих конденсаторов средние |

||

В результате применения |

|||

задержки распространения сигналов в схемах типа РК.ТЛ полу чаются в пределах 100—300 нсек. Остальные их электрические параметры такие же, как и у схем типа РТЛ.

Включение в выходную цепь эмиттерного повторителя, как показано на рис. 4.25 (транзистор Т4 и диод Д), позволяет повы сить нагрузочную способность элемента. Например, если сигналом

«вых2 схема |

может управлять четырьмя — шестью |

аналогичными |

ей схемами, |

то к выходу 1 можно подключить до 25 |

схем. Диод Д |

128

ускоряет спад на выходе напряжения «ПЫх i в момент запирания

транзистора Т4.

Транзисторные логические элементы на переключателях тока (ТЛПТ-схемы). В рассмотренных выше схемах транзисторы рабо тают в режиме насыщения, что ограничивает возможности увели чения частот их переключения до 1—2 Мгц. Допустимые частоты

Рис. 4.26. Логическая |

схема на переключателе тока |

с объединенными |

а — принципиальная схема |

эмиттерами: |

б — его возможное |

типового универсального элемента; |

условное изображение на функциональных схемах: * — принципиальная схема рас ширителя входной логики типового элемента

переключения существенно повышаются (до 10 Мгц и более) в схемах, в которых транзисторы работают в ненасыщенных режи мах. Одним из примеров таких схем является транзисторная схе ма с объединенными эмиттерами, изображенная на рис. 4.26, а. Принцип действия ее основан на переключении тока либо в тран зистор Т4, либо в один, два или все три транзистора Т1 — ТЗ. Это переключение осуществляется входными сигналами их\ — их3, из* меняющимися, например, от U0= +3,5 в до U\ = +4,2 б. Изменение входных сигналов в указанном диапазоне происходит симметрично относительно уровня +3,85 в, подаваемого в виде опорного

129