- •Модуль 6 Процессоры общего назначения

- •Лекция 15.

- •Особенности архитектуры IA-32 (на примере семейств Р6 и Р7)

- •Характеристики процессоров семейства Р6, Р7

- •Совместимость микропроцессоров

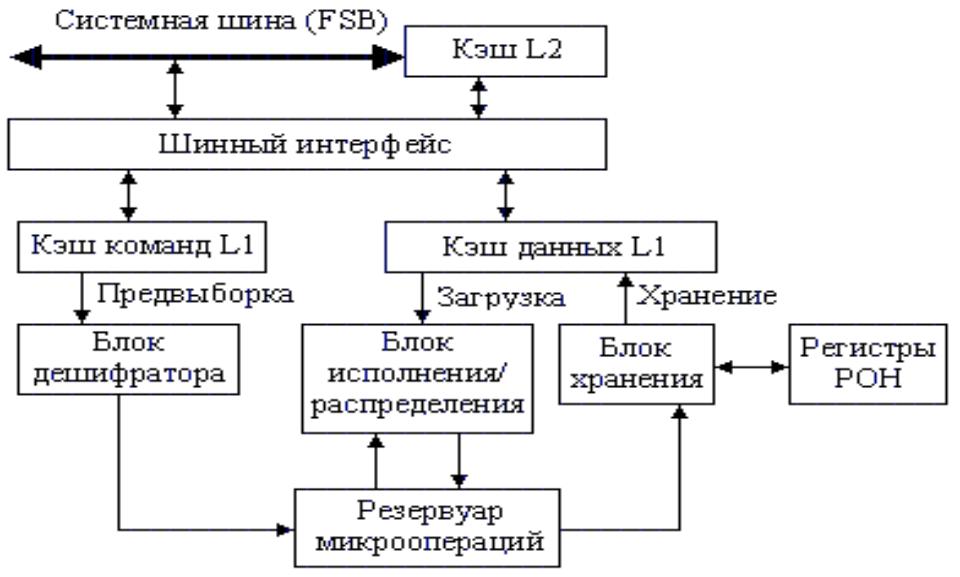

- •Рис. Функциональная схема процессора типа P6

- •Функциональная схема МП типа P6

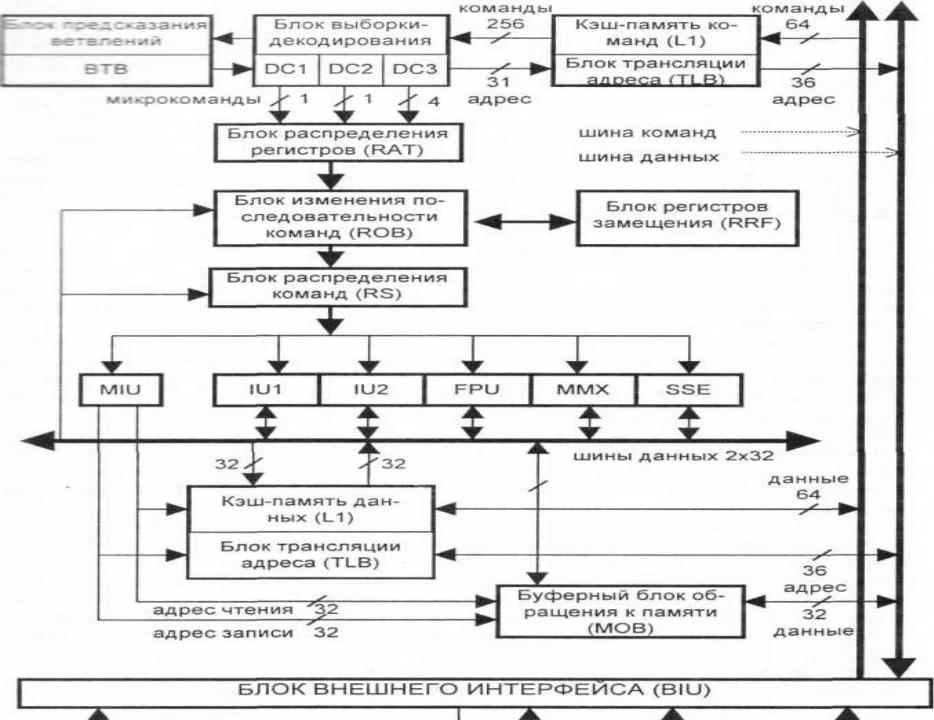

- •СТРУКТУРА ПРОЦЕССОРОВ INTEL P6,Р7

- •Структура микропроцессора Pentium

- •СТРУКТУРА ПРОЦЕССОРОВ INTEL P6,Р7 (продолжение)

- •СТРУКТУРА ПРОЦЕССОРОВ INTEL P6,Р7 (продолжение)

- •СТРУКТУРА ПРОЦЕССОРОВ INTEL P6,Р7 (продолжение)

- •СТРУКТУРА ПРОЦЕССОРОВ INTEL P6,Р7 (продолжение)

- •СТРУКТУРА ПРОЦЕССОРОВ INTEL P6,Р7 (продолжение)

- •СТРУКТУРА ПРОЦЕССОРОВ INTEL P6,Р7 (продолжение)

- •СТРУКТУРА ПРОЦЕССОРОВ INTEL P6,Р7 (продолжение)

- •СТРУКТУРА ПРОЦЕССОРОВ INTEL P6,Р7 (продолжение)

- •СТРУКТУРА ПРОЦЕССОРОВ INTEL P6,Р7 (продолжение)

- •СТРУКТУРА ПРОЦЕССОРОВ INTEL P6,Р7 (продолжение)

- •СТРУКТУРА ПРОЦЕССОРОВ INTEL P6,Р7 (продолжение)

- •СТРУКТУРА ПРОЦЕССОРОВ INTEL P6,Р7 (продолжение)

- •СТРУКТУРА ПРОЦЕССОРОВ INTEL P6,Р7 (продолжение)

- •Режимы работы процессоров Р6,Р7.

- •Защищенный режим

- •Режим системного управления

- •Архитектура IА-64

- •Архитектура IА-64

- •Архитектура IА-64

- •Архитектура Itanium

- •Основные аппаратные компоненты Itanium 1/3

- •Основные аппаратные компоненты Itanium 2/3

- •Основные аппаратные компоненты Itanium 3/3

- •Преимущества Itanium по сравнению х86 :

- •Недостатки Itanium:

- •Лекция 16

- •Регистры процессоров IA-32

- •Регистры процессоров IA-32

- •Регистры общего назначения

- •Регистры общего назначения IA-16 и их коды

- •Регистры общего назначения IA-32 и их коды

- •Сегментные регистры

- •Регистры сегментов

- •Указатель команд EIP/IP

- •Регистр флагов EFLAGS

- •Младшие шестнадцать битов регистра EFLAGS (биты 15-0) представляют 16- разрядный регистр флагов FLAGS,

- •Регистр флагов EFLAGS

- •Значение признаков в регистре EFLAGS ( продолжение)

- •Регистр флагов EFLAGS

- •Значение признаков в регистре EFLAGS ( продолжение)

- •Значение признаков в регистре EFLAGS ( продолжение)

- •Регистры блока обработки чисел с плавающей точкой

- •Регистры блока обработки чисел с плавающей точкой

- •Формат содержимого регистра TW

- •Формат содержимого регистра FPSR

- •Формат содержимого регистра FPCR

- •Формат содержимого регистра FPCR

- •Регистр управления FPCR

- •Регистр управления FPCR

- •Регистры — указатели команд FIP и данных FDP

- •Системные регистры

- •Регистр управления CR0 1/3

- •Регистр управления CR0 2/3

- •Регистр управления CR0

- •Регистры управления CR1,CR2, CR3

- •Регистр CR4

- •Регистры системных адресов GDTR, IDTR, LDTR. TR

- •Регистры отладки DR0-DR7

- •Внутренняя кэш-память

- •Кэш-память L1.

- •Кэш-память уровня L2

- •Структура кеш-памяти

- •Адресация кэш-памяти

- •Соответствие основной памяти и кеш-памяти

- •Выбор замещаемой строки кеш-памяти

- •Когерентность основной памяти и кэш-памяти

- •Режимы работы кеш-памяти в процессорах Р6

- •Лекция 17.

- •Форматы команд и способы адресации

- •Общий формат команды

- •Формат команд

- •Кодировка регистров общего назначения

- •Байт адресации MOD R/M

- •Байт адресации MOD R/M

- •Непосредственная адресация

- •Эффективный адрес операнда ЕА

- •Адресация 32-разрядных операндов

- •Байт адресации SIB

- •Формирование 16-разрядного ЕА

- •Формирование 32-разрядного ЕА(байт SIB отсутствует)

- •Формирование 32-разрядного ЕА (байт SIB присутствует)

- •Кодировка индексных и базовых регистров в байт SIB

- •Непосредственная адресация

- •Разрядность операндов и относительных адресов в Р-режиме

- •Регистровая адресация

- •Косвенно-регистровая адресация

- •Прямая (абсолютная) адресация

- •Базовая адресация

- •Индексная адресация

- •Базово-индексная адресация

- •Базово-индексная адресация со смещением

- •Дополнительные способы адресации

- •Индексная адресация с масштабированием

- •Базово-индексная адресация с масштабированием

- •Базово-индексная адресация со смещением и масштабированием

- •Относительная адресация

- •Адресация устройств ввода-вывода

- •Сегментация памяти

- •Кодировка сегментных регистров

- •Выбор сегментного регистра

- •Выбор сегментных регистров и относительного адреса

- •Лекеция 18

- •Классы и группы системы команд

- •Пересылка данных без преобразования и с преобразованием, ввод-вывод данных, загрузка эффективного адреса и

- •Арифметические операции

- •Логические и сдвиговые операции

- •Операции с битами, байтами и со строками символов

- •Команды управления программой

- •Команды операций над числами с плавающей точкой

- •Операции ММХ и SSE

- •Модуль 7 Защищенный режим микропроцессоров IA-32

- •Лекция 19

- •Режимы МП IA-32

- •Сегментация памяти в защищенном режиме

- •Таблицы дескрипторов

- •Таблица GDT, LDT и IDT

- •Выбор дескрипторов

- •Регистры GDTR, LDTR, IDTR

- •Выборка дескрипторов из таблиц GDT и LDT

- •Загрузка регистров GDTR, LDTR

- •Защита доступа к GDTR и LDTR

- •Формирование линейного адреса

- •Общий формат дескриптора

- •Обобщенный вид дескриптора

- •Атрибуты сегмента.

- •Атрибуты сегмента.

Модуль 6 Процессоры общего назначения

(микропроцессоры IA-32)

Лекция 15

Особенности архитектуры и структуры МП IA-32.

Лекция 16

Регистровые структуры МП IA-32.

Лекция 17

Форматы команд и способы адресации МП IA-32.

Лекеция 18

Система команд микропроцессоров х86.

Лекция 15.

Архитектура и структура МП IA-32.

Микропроцессоры фирм Intel и AMD, широко используются в современных компьютерах, системах управления телекоммуникационным оборудованием и др.

•В данном пособии подобрана информация по архитектуре микропроцессоров фирмы Intel семейств Р6 и Р7.

•Процессоры семейства Р6, Р7,продолжая общую линию микропроцессоров Intel 80x86, имеют ряд архитектурных и структурных особенностей по сравнению с предыдущими моделями.

•Общее процессорное ядро является основой семейства. Например, МП Pentium Pro, Pentium II и III относятся к семейству Р6, а Pentium 4 к семейству Р7.

Микропроцессорные системы. Лекция 15. Архитектура и структура МП IA-32.

Особенности архитектуры IA-32 (на примере семейств Р6 и Р7)

•Гарвардская структура с разделением потоков команд и данных с помощью введения отдельных внутренних блоков кэш-памяти для хранения команд и данных, а также шин для их передачи;

•Суперскалярная архитектура, обеспечивающая одновременное выполнение нескольких команд в параллельно работающих исполнительных устройствах;

•Динамическое исполнение команд, реализующее изменение последовательности команд (выполнение команд с опережением — спекулятивное выполнение), использование расширенного регистрового файла (переименование регистров), эффективное

предсказание ветвлений;

•Двойная независимая шина, содержащая отдельную шину для обращения к кэш-памяти 2-го уровня (выполняется с тактовой частотой процессора) и системную шину для обращения к памяти и внешним устройствам (выполняется с тактовой частотой системной платы).

Микропроцессорные системы. Лекция 15. Архитектура и структура МП IA-32.

Характеристики процессоров семейства Р6, Р7

•32-разрядная внутренняя структура;

•Использование системной шины (36 р. адреса и 64 р. данных);

•Раздельная внутренняя кэш-память уровня (L1) для команд и для

данных емкостью по 16 кбайт;

•Поддержка кэш-памяти команд и данных уровня (L2) емкостью до 2 Мбайт;

•Kонвейерное исполнение команд с реализацией 12 и 20 ступеней;

•Предсказание направления программного ветвления;

•Ускоренное выполнение операций с плавающей точкой;

•Приоритетный контроль при обращении к памяти (защищенный режим);

•Поддержка реализации мультипроцессорных систем;

•Наличие внутренних средств, обеспечивающих самотестирование, отладку и мониторинг производительности.

Микропроцессорные системы. Лекция 15. Архитектура и структура МП IA-32.

Совместимость микропроцессоров

•Характеристики процессоров семейств Р6 и Р7 позволяют эффективно работать с разнообразным программным обеспечением под управлением операционных систем:

•MS-DOS, Windows, OS/2 и ряда других.

•Исполняемый код для этих процессоров полностью совместим с кодом предыдущих моделей МП Intel 80x86 (8086, 8088, 80186, 80188, 80286, 80386, 80486, Pentium, Pentium MMX, Pentium Pro, Pentium II и III, Pentium 4,

•поэтому для них может использоваться весь объем ранее разработанного программного обеспечения.

Микропроцессорные системы. Лекция 15. Архитектура и структура МП IA-32.

Рис. Функциональная схема процессора типа P6

Функциональная схема МП типа P6

Принципиальное отличие этого семейства состоит в том, что команды x86 преобразуются во внутренние RISC-подобные команды, называемые микрокомандами. Микрокод – это элементарная инструкция, которая выполняется одним из шести блоков процессора параллельно. Это позволяет устранить многие ограничения, свойственные набору команд x86, такие как нерегулярность кодирования команд, операции целочисленных пересылок «регистр – память» и переменная длина непосредственных операндов. МП семейства P6 имеют трехходовую суперскалярную конвейерную архитектуру. Термин “трехходовая суперскалярная” означает, что, используя технику параллельной обработки, процессор может в среднем за один такт декодировать, диспетчеризировать и выполнить три команды.

СТРУКТУРА ПРОЦЕССОРОВ INTEL P6,Р7

•Общая структура процессоров семейства Р6 показана на рис.1.1.

•Гарвардская внутренняя структура реализуется путем разделения потоков команд и данных, поступающих от системной шины через блок внешнего интерфейса в отдельные кэш-память команд и кэш-память данных и

•Шиной кэш-памяти второго уровня (L2),

•Блок внешнего интерфейса (BIU — Bus Interface Unit) реализует протоколы обмена процессора с системной шиной, к которой подключается память, контроллеры ввода/вывода, другие активные устройства системы.

Микропроцессорные системы. Лекция 15. Архитектура и структура МП IA-32.

|

|

|

|

команды |

|

|

команды |

Блок предсказания |

Блок выборки- |

256 |

Кэш-память команд |

64 |

|||

|

|

||||||

ветвлений |

декодирования |

|

|

(L1) |

|

||

ВТВ |

DC1 |

DC2 |

DC3 |

|

Блок трансляции |

|

|

|

адреса (TLB) |

|

|||||

|

|

|

|

31 |

36 |

||

микрокоманды |

1 |

1 |

4 |

|

|

||

адрес |

|

|

адрес |

||||

|

Блок распределения |

|

|

шина команд |

|

||

|

регистров (RAT) |

|

|

|

|||

|

|

|

шина данных |

|

|||

|

|

|

|

|

|

|

|

|

Блок изменения |

|

Блок регистров |

|

|||

|

последовательности |

|

|

||||

|

|

замещения (RRF) |

|

||||

|

команд (ROB) |

|

|

||||

|

|

|

|

|

|||

|

Блок распределения |

|

|

|

|

||

|

команд (RS) |

|

|

|

|

||

MIU |

IU1 |

|

IU2 |

FPU |

MMX |

SSE |

|

|

|

|

|

|

|

шины данных 2х32 |

|

|

|

|

|

|

|

|

данные |

Кэш-память данных |

|

|

|

64 |

|||

|

|

|

|

||||

|

(L1) |

|

|

|

|

|

|

Блок трансляции |

|

|

|

|

|||

|

адреса (TLB) |

|

|

|

|

36 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

адрес |

адрес чтения |

32 |

|

|

|

Буферный блок обращения |

|

|

|

|

|

к памяти (МОВ) |

|

|||

|

|

|

|

|

данные |

||

адрес записи |

32 |

|

|

|

|

|

32 |

Б Л О К В Н Е Ш Н Е Г О И Н Т Е Р Ф Е Й С А (B I U) |

|

||||||

шина кэш-памяти |

|

|

|

|

|

|

|

второго уровня |

|

|

|

|

|

|

|

Кэш-память второго |

|

Сигналы |

Данные D[63:0] |

Адрес А[35:3] |

уровня (L2) |

|

управления |

|

ВЕ[7:0] |

|

|

|

|

|

Системная шина