МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ

РОССИЙСКОЙ ФЕДЕРАЦИИ

Федеральное государственное образовательное

учреждение высшего образования

«Юго-Западный государственный университет»

Лабораторная работа №2

По дисциплине «Аппаратные средства вычислительной техники»

Выполнил: Бунина А.В.

студент группы ИБ-01б

Проверил: Шевелев С.С.

доцент

Курск, 2022

Задание к лабораторной работе №2

1. Формирование логических условий работы рассматриваемой схемы или узла путём составления таблицы истинности для каждого из выходов комбинационной схемы.

2. Получение по таблице истинности или на основании использования методов минимизации минимальных нормальных форм в дизъюнктивной или конъюнктивной форме (ДНФ или КНФ).

3. Преобразование минимальных нормальных форм к виду, соответствующему выбранному (или заданному) набору логических элементов (логическому базису).

4. Построение комбинационной схемы.

Индивидуальное задание для выполнения (вариант 2.3).

построение одноразрядного сумматора на сдвоенном мультиплексоре 4→1 (74153 или К155КП2);

разработку схемы сопряжения мультиплексоров 8→1 (74151 или 155КП7) и 4→1 (74153) с целью получения устройства с функциями мультиплексора 16→1.

Применительно к данному лабораторному практикуму этот перечень нужно дополнить этапом исследования (моделирования) комбинационной схемы с помощью программы Multisim на предмет проверки правильности её функционирования.

Теоретические сведения

Существующие электронные схемы принято делить на два класса - аналоговые и цифровые. Аналоговые схемы предназначены для преобразования и обработки сигналов, изменяющихся по закону непрерывной функции (это различного рода усилители, генераторы, модуляторы, фильтры и т.д.). Цифровые схемы оперируют с сигналами, изменяющимися по закону дискретной функции. При этом в большинстве случаев эта функция является двоичной, так как возможные её значения определяются символами двоичного алфавита: 0 или 1. Этим дискретным значениям в схеме соответствуют два хорошо различающихся уровня напряжения: высокий или H-уровень (high -высокий) и низкий или L-уровень (low - низкий). Величины H- и L- уровней зависят только от типа используемой транзисторной технологии и, например, для TTL- технологии они составляют

.

.

В свою очередь электронные схемы в вычислительной техникепо принципу функционирования принято делить на два типа -комбинационные и последовательностные (цифровые автоматы).

Комбинационной называют схему с n входами и m выходами, для которой совокупность выходных сигналов в данный момент времени полностью определяется совокупностью входных сигналов для этого же момента времени и не зависит от входных сигналов, действующих в предыдущие моменты времени. Последнее замечание отличает комбинационную схему от цифровых автоматов, которым посвящены последующие работы.

Задача анализа комбинационных схем сводится к нахождению системы логических (булевых) функций, определяющих логику работы такой схемы. Синтез является задачей, обратной анализу, и заключается в построении комбинационной схемы по заданным условиям работы. Эти условия определяют количество входов и выходов схемы, а также закон соответствия двоичных наборов входных и выходных переменных (сигналов).

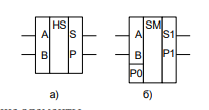

Сумматоры. Простейшим суммирующим элементом является полусумматор. Он имеет два входа А и В и два выхода: S (cумма ) и P (перенос) (рис.1 ,а).

Рис. 1. Суммирующие элементы

Обозначением полусумматора служат буквы НS (Нalf Sum). Его работа описывается уравнениями

Процедуру сложения двух n – разрядных двоичных чисел можно представить следующим образом. Сложение цифр А0 и В0 младшего разряда дает бит суммы S0 и бит переноса P1. В следующем разряде производится сложение цифр А1, В1, и Р1, которое формирует бит суммы S1 и перенос Р2.

Полный одноразрядный сумматор имеет три входа (рис.1,б): два для слагаемых А и В и один для сигнала переноса с предыдущего разряда.

На рис. 3.12 показана схема, поясняющая принцип действия n- разрядного сумматора с последовательным переносом. Число сумматоров здесь равно числу разрядов. Выход переноса Р каждого сумматора соединен со входом переноса следующего, более старшего разряда. На входе переноса сумматора младших разрядов установлен “0”, так как сигнал переноса сюда не поступает.

Рис. 2. Сумматор с последовательным переносом.

Слагаемые А i и Bi складываются во всех разрядах одновременно, а перенос Р поступает с окончанием операции сложения в предыдущем разряде.

Быстродействие многоразрядных сумматоров подобного вида ограничено задержкой переноса, так как формирование сигнала переноса на выходе старшего разряда не может произойти до тех пор, пока сигнал переноса младшего разряда не распространится последовательно по всей схеме.

Время переноса можно уменьшить, вводя параллельный перенос, для чего применяют специальные узлы – блоки ускоренного переноса. Они имеют достаточно сложную схему даже для n = 4 и с увеличением числа разрядов сложность настолько возрастает, что изготовление их становится нецелесообразно.

В виде отдельных микросхем выпускаются одноразрядные, двухразрядные и четырехразрядные сумматоры. В семействе ТТЛ это микросхемы соответственно К155ИМ1, ИМ2 и ИМ3.