- •1 Introduction

- •2 Description

- •2.1 Device overview

- •2.2 Full compatibility throughout the family

- •2.3 Overview

- •2.3.2 Embedded Flash memory

- •2.3.3 CRC (cyclic redundancy check) calculation unit

- •2.3.4 Embedded SRAM

- •2.3.5 Nested vectored interrupt controller (NVIC)

- •2.3.6 External interrupt/event controller (EXTI)

- •2.3.7 Clocks and startup

- •2.3.8 Boot modes

- •2.3.9 Power supply schemes

- •2.3.10 Power supply supervisor

- •2.3.11 Voltage regulator

- •2.3.14 RTC (real-time clock) and backup registers

- •2.3.15 Timers and watchdogs

- •2.3.17 Universal synchronous/asynchronous receiver transmitters (USARTs)

- •2.3.18 Serial peripheral interface (SPI)

- •2.3.20 Ethernet MAC interface with dedicated DMA and IEEE 1588 support

- •2.3.21 Controller area network (CAN)

- •2.3.24 Remap capability

- •2.3.27 Temperature sensor

- •2.3.29 Embedded Trace Macrocell™

- •3 Pinouts and pin description

- •4 Memory mapping

- •5 Electrical characteristics

- •5.1 Parameter conditions

- •5.1.1 Minimum and maximum values

- •5.1.2 Typical values

- •5.1.3 Typical curves

- •5.1.4 Loading capacitor

- •5.1.5 Pin input voltage

- •5.1.6 Power supply scheme

- •5.1.7 Current consumption measurement

- •5.2 Absolute maximum ratings

- •5.3 Operating conditions

- •5.3.1 General operating conditions

- •5.3.3 Embedded reset and power control block characteristics

- •5.3.4 Embedded reference voltage

- •5.3.5 Supply current characteristics

- •5.3.6 External clock source characteristics

- •5.3.7 Internal clock source characteristics

- •5.3.8 PLL, PLL2 and PLL3 characteristics

- •5.3.9 Memory characteristics

- •5.3.10 EMC characteristics

- •5.3.11 Absolute maximum ratings (electrical sensitivity)

- •5.3.12 I/O current injection characteristics

- •5.3.13 I/O port characteristics

- •5.3.14 NRST pin characteristics

- •5.3.15 TIM timer characteristics

- •5.3.16 Communications interfaces

- •5.3.18 DAC electrical specifications

- •5.3.19 Temperature sensor characteristics

- •6 Package characteristics

- •6.1 Package mechanical data

- •6.2 Thermal characteristics

- •6.2.1 Reference document

- •6.2.2 Selecting the product temperature range

- •7 Part numbering

- •Appendix A Application block diagrams

- •A.1 USB OTG FS interface solutions

- •A.2 Ethernet interface solutions

- •A.3 Complete audio player solutions

- •A.4 USB OTG FS interface + Ethernet/I2S interface solutions

- •Revision history

STM32F105xx, STM32F107xx |

Application block diagrams |

|

|

Appendix A Application block diagrams

A.1 USB OTG FS interface solutions

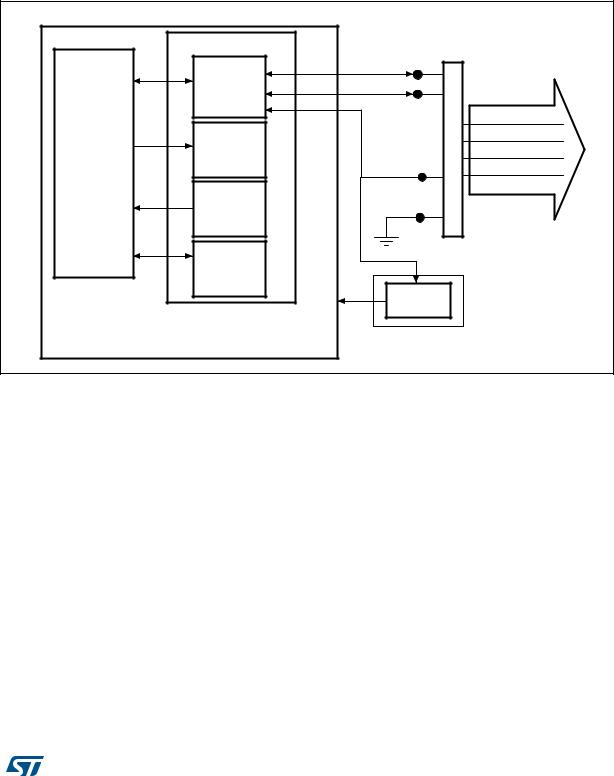

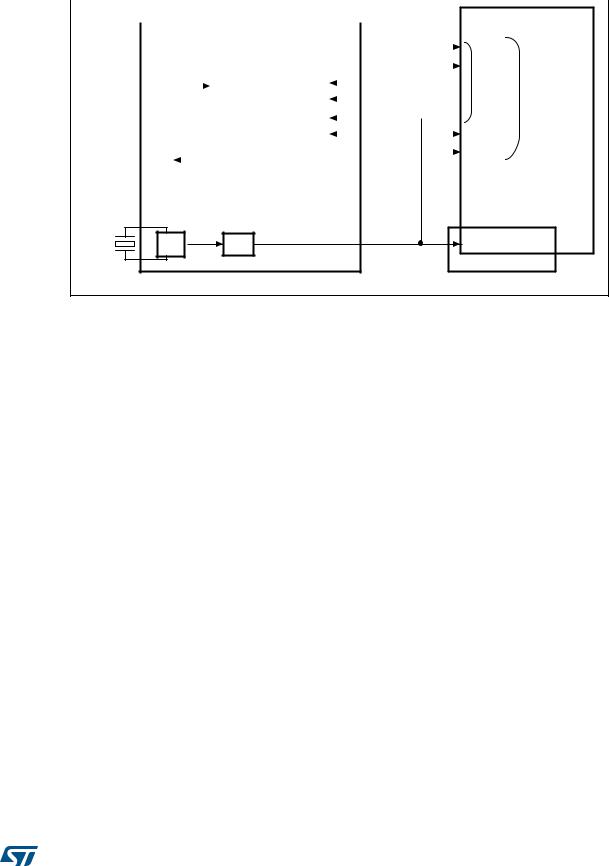

Figure 46. USB OTG FS device mode

STM32F105xx/STM32F107xx |

|

|

|

|

|

OTG PHY |

|

|

|

|

USB |

DP |

|

|

|

|

|

|

|

|

Full-speed |

DM |

connector |

|

|

transceiver |

To host |

||

|

|

|||

|

|

|

DP |

|

USB |

|

|

DM |

|

OTG |

HNP |

|

-B |

VBUS |

Full-speed |

|

VBUS |

USB Micro |

VSS |

core |

|

|||

|

|

|

||

|

ID |

VSS |

|

|

|

|

|

|

|

|

SRP |

|

|

|

|

VDD |

5 V to VDD |

|

|

|

|

Regulator(1) |

|

|

|

|

|

|

ai15653b |

1. Use a regulator if you want to build a bus-powered device.

DocID15274 Rev 7 |

91/104 |

Application block diagrams |

STM32F105xx, STM32F107xx |

|

|

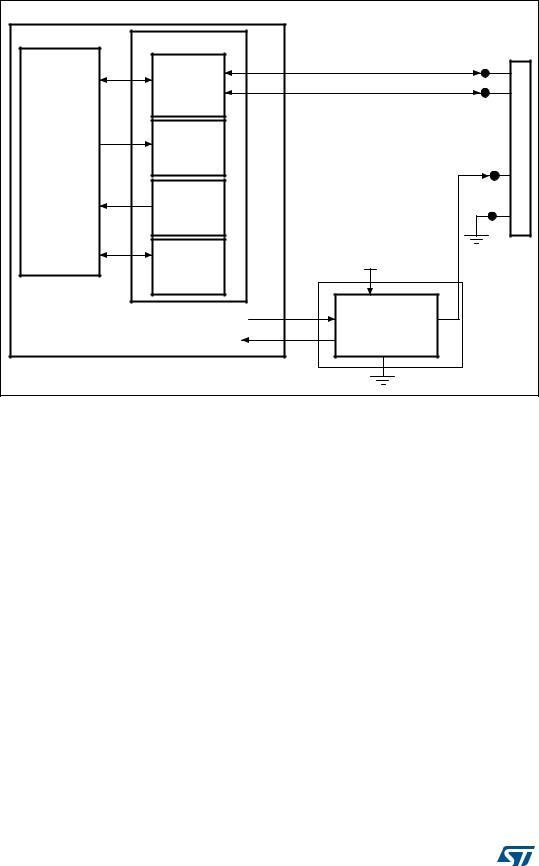

Figure 47. Host connection

STM32F105xx/STM32F107xx |

|

|

|

|

|

|

OTG PHY |

|

|

|

|

|

USB |

|

|

DP |

|

|

full-speed/ |

|

|

DM |

A connector |

|

low-speed |

|

|

||

|

|

|

|

||

|

transceiver |

|

|

|

|

USB |

|

|

|

|

|

OTG |

HNP |

|

|

|

|

Full-speed |

|

|

|

VBUS |

td- |

core |

|

|

|

|

S |

|

|

|

|

USB |

|

|

ID |

|

|

VSS |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

(2) |

|

|

|

SRP |

|

VDD |

|

|

|

|

|

|

|

|

|

|

EN |

Current-limited |

5 V |

|

|

GPIO |

power distribution |

|

||

|

GPIO + IRQ |

OVRCR |

switch |

|

|

|

flag |

STMPS2141STR(1) |

|

|

|

|

|

|

|

||

|

|

|

|

ai15654b |

|

1. STMPS2141STR needed only if the application has to support bus-powered devices.

92/104 |

DocID15274 Rev 7 |

STM32F105xx, STM32F107xx |

Application block diagrams |

|

|

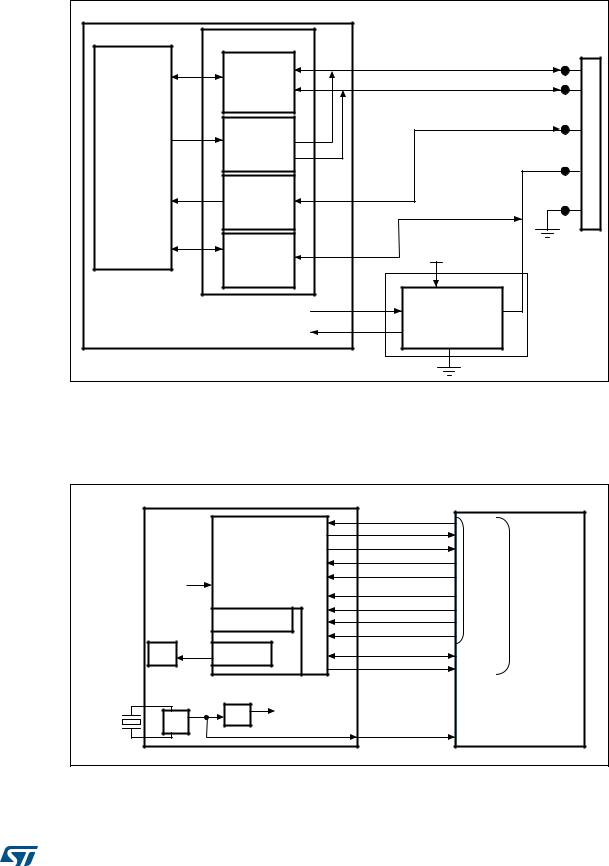

Figure 48. OTG connection (any protocol)

STM32F105xx/STM32F107xx |

|

|

|

|

|

OTG PHY |

|

|

|

|

USB |

|

DP |

|

|

full-speed/ |

|

DM |

connector |

|

low-speed |

|

||

|

|

|

||

|

transceiver |

|

ID |

|

|

|

|

||

USB |

|

|

|

|

|

|

|

-AB |

|

OTG |

HNP |

|

VBUS |

|

Full-speed |

|

|

Micro |

|

core |

|

|

|

|

|

ID |

|

VSS |

USB |

|

|

|

|

|

|

SRP |

|

VDD |

|

|

|

|

|

|

|

|

EN |

Current-limited |

|

|

GPIO |

power distribution 5 V |

|

|

|

GPIO + IRQ |

OVRCR |

switch |

|

|

flag |

STMPS2141STR(1) |

|

|

|

|

|

||

|

|

|

ai15655b |

|

1. STMPS2141STR needed only if the application has to support bus-powered devices.

A.2 Ethernet interface solutions

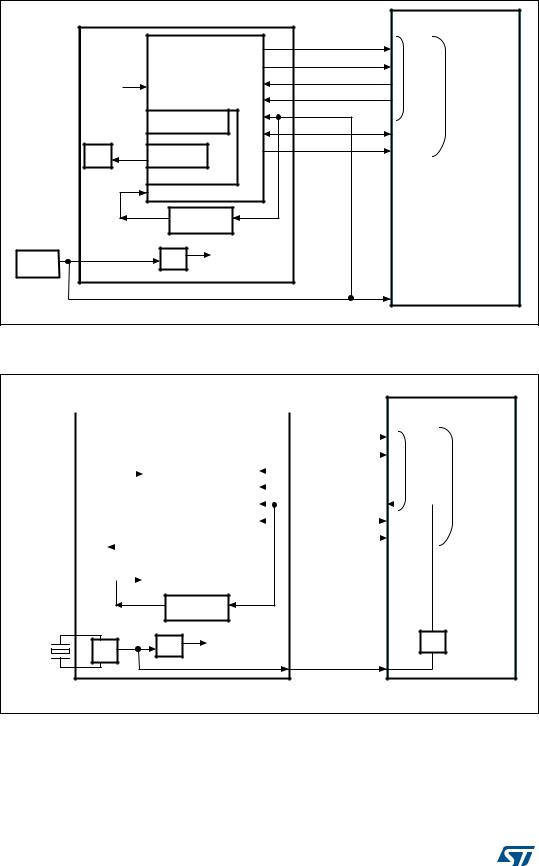

Figure 49. MII mode using a 25 MHz crystal

|

|

STM32F107xx |

|

|

|

MCU |

Ethernet |

|

MII_TX_CLK |

|

|

|

MII_TX_EN |

|

|

|

MAC 10/100 |

MII_TXD[3:0] |

|

|

|

|

|

MII_CRS |

|

|

|

|

MII_COL |

|

HCLK(1) |

|

MII_RX_CLK |

|

|

|

|

|

|

|

|

|

|

MII_RXD[3:0] |

|

|

IEEE1588 PTP |

MII_RX_DV |

|

|

|

Timer |

|

MII_RX_ER |

|

|

input |

|

|

|

TIM2 |

trigger Timestamp |

|

MDIO |

|

|

comparator |

|

MDC |

|

|

|

|

|

|

|

|

|

PPS_OUT(2) |

XTAL |

|

PLL |

HCLK |

|

25 MHz |

OSC |

|

PHY_CLK 25 MHz |

|

|

|

|

||

Ethernet

PHY 10/100

MII

= 15 pins

MII + MDC = 17 pins

XT1

ai15656

1.HCLK must be greater than 25 MHz.

2.Pulse per second when using IEEE1588 PTP, optional signal.

DocID15274 Rev 7 |

93/104 |

Application block diagrams |

STM32F105xx, STM32F107xx |

|

|

Figure 50. RMII with a 50 MHz oscillator

|

|

STM32F107xx |

|

|

|

Ethernet |

|

MCU |

|

|

|

|

|

|

PHY 10/100 |

|

Ethernet |

|

RMII_TX_EN |

|

|

|

|

|

|

|

RMII_TXD[1:0] |

|

|

||

|

|

MAC 10/100 |

RMII |

||||

HCLK(1) |

|

|

RMII_RXD[1:0] |

||||

|

|

RMII_CRX_DV |

= 7 pins |

||||

|

|

|

|

|

RMII + MDC |

||

|

|

|

|

RMII_REF_CLK |

|

||

|

|

IEEE1588 PTP |

|

= 9 pins |

|||

|

Timer |

MDIO |

|

|

|

||

|

|

|

|

|

|

||

|

input |

|

|

MDC |

|

|

|

TIM2 |

trigger |

Timestamp |

|

|

|

|

|

|

|

|

|

|

|||

|

comparator |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

/2 or /20 |

|

|

|

|

|

2.5 or 25 MHz synchronous |

50 MHz |

|

|

|

|||

OSC |

|

PLL |

HCLK |

|

|

|

|

50 MHz |

|

|

|

|

|

|

|

|

|

|

|

PHY_CLK |

50 MHz |

XT1 |

50 MHz |

|

|

|

|

|

|

|

ai15657 |

1. HCLK must be greater than 25 MHz.

Figure 51. RMII with a 25 MHz crystal and PHY with PLL

|

|

|

|

|

|

STM32F107xx |

|

|

|

Ethernet |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

PHY 10/100 |

|

|

MCU |

|

|

|

|

|

|

|

|

|

RMII_TX_EN |

|||

|

|

|

|

|

Ethernet |

|

|

|

|

|||||

|

|

|

|

|

|

|

RMII_TXD[1:0] |

|

|

|

||||

|

|

|

|

|

|

MAC 10/100 |

|

|

|

|

||||

|

HCLK(1) |

|

|

|

RMII_RXD[1:0] |

|

RMII |

|||||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

RMII_CRX_DV |

|

|||||

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

= 7 pins |

||

|

|

|

|

|

|

|

|

|

|

|

RMII_REF_CLK |

|

REF_CLK RMII + MDC |

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

Timer |

IEEE1588 PTP |

|

|

|

MDIO |

|

|

= 9 pins |

||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

input |

|

|

|

|

|

MDC |

|

|

|

|||

|

TIM2 |

trigger |

Timestamp |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

comparator |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2.5 or 25 MHz |

|

/2 or /20 |

50 MHz |

|

|

|

synchronous |

|

|

|||

XTAL |

OSC |

PLL |

HCLK |

|

PLL |

|

25 MHz |

|

|

PHY_CLK |

25 MHz |

XT1 |

|

|

|

|

||||

|

|

|

|

|||

ai15658

1. HCLK must be greater than 25 MHz.

94/104 |

DocID15274 Rev 7 |

STM32F105xx, STM32F107xx |

|

|

|

|

|

|

Application block diagrams |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 52. RMII with a 25 MHz crystal |

|

|

|

||||||

|

|

|

|

|

|

|

STM32F107xx |

|

|

|

Ethernet |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PHY 10/100 |

|

|

|

|

MCU |

|

|

|

|

|

|

|

|

RMII_TX_EN |

||||

|

|

|

|

|

|

Ethernet |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

RMII_TXD[1:0] |

|

|

|

|||||

|

|

|

|

|

|

|

MAC 10/100 |

|

|

|

|

|||||

|

|

|

HCLK |

|

|

|

RMII_RXD[1:0] |

|

RMII |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

RMII_CRX_DV |

|

= 7 pins |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

50 MHz |

|

RMII_REF_CLK |

|

50 MHz |

RMII + MDC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

IEEE1588 PTP |

|

|

|

|

|

= 9 pins |

|||

|

|

|

|

Timer |

|

|

MDIO |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

input |

|

|

|

|

|

MDC |

|

|

|

|||

|

|

|

TIM2 |

trigger |

Time stamp |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

comparator |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

XTAL |

OSC |

|

50 MHz |

25 MHz |

PLLS |

XT1/XT2 |

|

|

|

|

NS DP83848(1) |

ai15659b

1.The NS DP83848 is recommended as the input jitter requirement of this PHY. It is compliant with the output jitter specification of the MCU.

DocID15274 Rev 7 |

95/104 |