DOCS / вычтехника / PIC16_2014

.pdf2.Налаштувати необхідну швидкість обміну (табл. 6.1);

3.Прийняти пакет даних та перевіряти його формат (табл. 6.1);

4.Якщо пакет даних прийнято вірно, то необхідно зчитати стан порту B, змінити стан порту A, сформувати та передати пакет підтвердження, а в противному випадку – пакет помилки (табл. 6.1);

5.Повторювати пункти 3 та 4.

Таблиця 6.1 Варіанти завдань для лабораторної роботи №6*

№ |

Швидкість, |

Пакет, що приймається |

Пакет |

Пакет |

|

бод |

підтвердження |

помилки |

|||

|

|

||||

|

|

|

|

|

|

1 |

9600 |

55h, BA0, BA1, BA2, BA3 |

55h, BBx |

55h, FFh |

|

|

|

|

|

|

|

2 |

19200 |

AAh, BA3, BA2, BA1, BA0 |

AAh, BBx |

AAh, EEh |

|

|

|

|

|

|

|

3 |

2400 |

33h, BA2, BA3, BA0, BA1 |

33h, BBx |

33h, AAh |

|

|

|

|

|

|

|

4 |

1200 |

CCh, BA1, BA0, BA3, BA2 |

CCh, BBx |

CCh, 55h |

|

|

|

|

|

|

|

5 |

9600 |

A5h, BA2, BA1, BA3, BA0 |

A5h, BBx |

A5h, 0Fh |

|

|

|

|

|

|

* – для всіх варіантів тактова частота мікроконтролеру дорівнює 4 МГц, байти BA0-BA3 можуть приймати тільки значення 00h та FFh (що відповідає рівню логічного 0 та 1 для виводів RA0-RA3); байт BBx має вигляд xxxx0000, де xxxx – стан виводів RB7-RB4; початковий стан молодшої частини порту A – 1111.

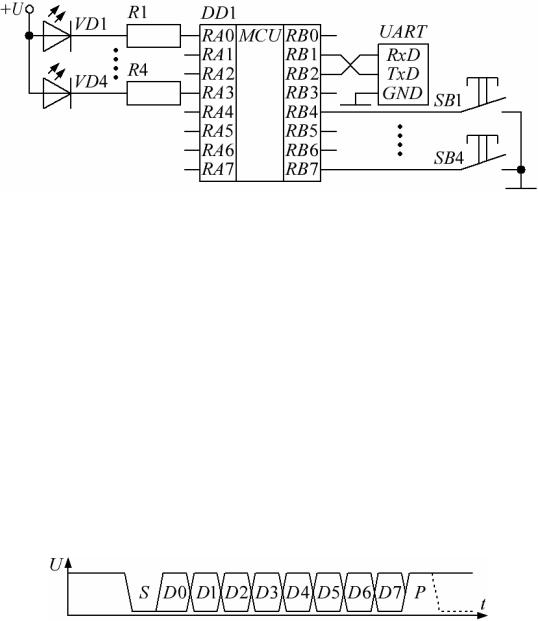

Для оцінки результатів виконання програми слід використовувати засоби емуляції, які надаються середовищем розробки MPLAB, а також схему, яку наведено на рис. 6.1. Схема забезпечує індикацію стану виводів RA0-RA3 за допомогою світлодіодів VD1-VD4, струм через які обмежується резисторами R1-R4. До виводів RB1 (RxD) та RB2 (TxD) підключено зовнішній пристрій з інтерфейсом послідовного порту (UART). Виводи передавача (TxD) та приймача (RxD) є однонаправленими, тому вивід RxD

21

мікроконтролеру з’єднано із вивідом TxD зовнішнього пристрою та навпаки.

Рис. 6.1 Схема підключення світлодіодів, клавіш та зовнішнього пристрою з інтерфейсом послідовного порту (UART)

Теоретичні відомості

В стані паузи на лініях TxD та RxD присутній рівень логічної 1 (рис. 6.2). Передача починається з видачі стартового біта (S), який потрібен для виявлення початку обміну приймачем. Стартовий біт завжди дорівнює логічному 0, тобто приймач починає прийом по першому спадаючому фронту сигналу. За нім передаються біти даних (D0-D7) молодшим бітом вперед. Після передачі бітів даних видається стоповий біт (P), який повинен дорівнювати логічної 1. За стоповим бітом може слідувати стан паузи або може починатися передача наступного байту.

Рис. 6.2 Часова діаграма передачі байту Швидкість обмину передавача повинна співпадати із швидкістю

обміну приймача. Якщо ці швидкості не співпадають, то приймач буде отримувати некоректну інформацію. Для часткового контролю швидкості може використовуватися стоповий біт. Якщо приймач отримує на місті стопового біту логічний 0, то фіксується помилка кадру. Байт, що

22

прийнято з помилкою кадру, повинен бути відкинутий. Швидкість обмину задається у вигляді дільника в регістрі SPBRG. Для асинхронного обміну

існує два режиму: низькошвидкісній (BRGH=0) та високошвидкісній

(BRGH=1). Швидкість обмину розраховується за формулами:

V= FOSC / [ 64∙( SPBRG +1)] |

(низькошвидкісній режим), |

V= FOSC / [ 16∙( SPBRG +1)] |

(високошвидкісній режими), |

де FOSC – тактова частота мікроконтролеру. |

|

Окрім передачі 8 біт даних |

в одному кадрі, існує можливість |

9-бітної передачі. Додатковий біт може використовуватись для контролю передачі (наприклад, біт парності) або для зазначення певних ситуацій.

Мікроконтролери PIC16F627/PIC16F628 забезпечують підтримку апаратного детектування адреси за допомогою додаткового біту. Якщо додатковий біт дорівнює логічному 0, то прийнятий байт відкидається.

Якщо додатковий біт дорівнює логічної 1, то генерується переривання, а

прийнятий байт порівнюється з адресою пристрою. Такий режим дозволяє ефективно працювати пристрою з інтерфейсами RS-422 та RS-485.

Контрольні запитання

1.Наведіть часову діаграму передачі байту за допомогою УАПП.

2.Навіщо потрібні стартовий та стоповий біти?

3.Розрахуйте значення регістру SPBRG в двох режимах для швидкості 9600 бод при тактовій частоті 4 МГц.

4.Розрахуйте мінімальний час, який потрібен для передачі 100 байт на швидкості 19200 бод.

5.Розрахуйте співвідношення між кількістю бітів даних та загальною кількістю бітів для 8-бітної та 9-бітної передачі.

6.Для чого може використовуватися додатковий біт у 9-бітної передачі?

23

ДОДАТКИ

Додаток А. Стенд для апаратного налагодження програм

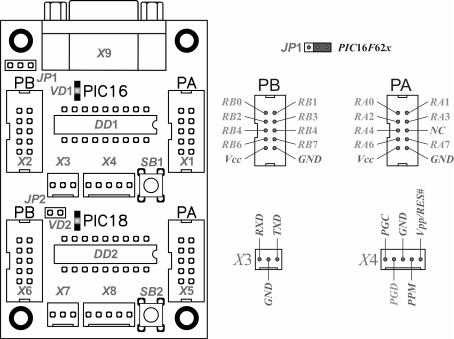

На рис. Д.1 наведено зовнішній вигляд стенду для апаратного налагодження програм та функціональність роз’ємів.

Рис. Д.1 Стенд для апаратного налагодження програм Зі складу стенду використовуються:

DD1 – мікроконтролер PIC16F62x;

X1, X2 – роз’єми для підключення зовнішніх пристроїв до портів A та B;

X3 – роз’єм для підключення зовнішніх пристроїв до виводів УАПП;

X4 – роз’єм для підключення програматору;

X9 – роз’єм для підключення живлення стенду;

JP1 – перемикач для вибору сімейства мікроконтролерів (PIC16 або

PIC18);

SB1 – клавіша скидання мікроконтролеру PIC16F62x;

VD1 – світлодіод, який показує, що обрано сімейство PIC16.

24

Додаток Б. Система команд мікроконтролерів сімейства PIC16

Таблиця Д.1 Система команд

Мнемокод |

|

Опис команди |

|

Трива- |

Зміна |

|||

команди |

|

|

лість* |

прапорів |

||||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

1 |

|

2 |

|

|

|

|

3 |

4 |

|

|

|

|

|

||||

|

|

Байт-орієнтовані команди |

|

|

||||

|

|

|

|

|

||||

addwf f,d |

Додавання регістрів w та f |

|

1 |

C, DC, Z |

||||

|

|

|

|

|

||||

andwf f,d |

Логічне ″І″ регістрів w та f |

|

1 |

Z |

||||

|

|

|

|

|

|

|

|

|

clrf f |

Скидання регістру f |

|

|

|

|

1 |

Z |

|

|

|

|

|

|

|

|

|

|

clrw |

Скидання регістру w |

|

|

|

|

1 |

Z |

|

|

|

|

|

|

|

|

|

|

com f,d |

Інверсія регістру f |

|

|

|

|

1 |

Z |

|

|

|

|

|

|

|

|

|

|

dec f,d |

Декремент регістру f |

|

|

|

|

1 |

Z |

|

|

|

|

|

|

|

|

|

|

|

Декремент |

регістру |

|

f |

та |

пропуск |

|

|

decfsz f,d |

наступної |

команди |

у |

|

разі |

нульового |

1(2)** |

Не діє |

|

результату |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

inc f,d |

Інкремент регістру f |

|

|

|

|

1 |

Z |

|

|

|

|

|

|

|

|

|

|

|

Інкремент |

регістру |

|

f |

та |

пропуск |

|

|

incfsz f,d |

наступної |

команди |

у |

|

разі |

нульового |

1(2)** |

Не діє |

|

результату |

|

|

|

|

|

|

|

|

|

|

|

|

||||

iorwf f,d |

Логічне ″АБО″ регістрів w та f |

|

1 |

Z |

||||

|

|

|

|

|

||||

movf f,d |

Пересилання даних з регістру f |

|

1 |

Z |

||||

|

|

|

|

|

|

|

||

movwf f |

Пересилання даних |

з |

|

регістру w до |

1 |

Не діє |

||

регістру f |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

nop |

Немає операції |

|

|

|

|

1 |

Не діє |

|

|

|

|

|

|||||

rlf f,d |

Циклічний зсув регістру f ліворуч через |

1 |

C |

|||||

перенос |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

25

Продовження табл. Д.1

1 |

2 |

|

|

|

3 |

4 |

|

|

|

|

|||

rrf f,d |

Циклічний зсув регістру f праворуч через |

1 |

C |

|||

перенос |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

||

subwf f,d |

Віднімання регістру w від регістру f |

|

1 |

C, DC, Z |

||

|

|

|

|

|

|

|

swapwf f,d |

Обмін напівбайтів регістру f |

|

|

1 |

Не діє |

|

|

|

|

|

|||

xorwf f,d |

Логічне ″Виключне АБО″ регістрів w та f |

1 |

Z |

|||

|

|

|

|

|

||

|

Біт-орієнтовані команди |

|

|

|

||

|

|

|

|

|

|

|

bcf f,b |

Скидання біта b у регістрі f |

|

|

1 |

Не діє |

|

|

|

|

|

|

|

|

bsf f,b |

Встановлення біта b у регістрі f |

|

|

1 |

Не діє |

|

|

|

|

|

|

|

|

btfsc f,b |

Пропуск наступної |

інструкції |

в |

разі, |

1(2)** |

Не діє |

якщо біт b в регістрі f дорівнює 0 |

|

|

||||

|

|

|

|

|

||

|

|

|

|

|

|

|

btfss f,b |

Пропуск наступної |

інструкції |

в |

разі, |

1(2)** |

Не діє |

якщо біт b в регістрі f дорівнює 1 |

|

|

||||

|

|

|

|

|

||

|

|

|

|

|||

|

Команди управління та операцій з константами |

|

||||

|

|

|

|

|

||

addlw k |

Додавання регістру w та константи k |

|

1 |

C, DC, Z |

||

|

|

|

|

|

||

andlw k |

Логічне ″І″ регістру w та константи k |

|

1 |

Z |

||

|

|

|

|

|

|

|

call k |

Виклик процедури |

|

|

|

2 |

Не діє |

|

|

|

|

|

|

|

clrwdt |

Скидання сторожового таймеру |

|

|

1 |

TO, PD |

|

|

|

|

|

|

|

|

goto k |

Безумовний перехід |

|

|

|

2 |

Не діє |

|

|

|

|

|||

iorlw k |

Логічне ″АБО″ регістру w та константи k |

1 |

Z |

|||

|

|

|

|

|||

movlw k |

Пересилання константи k до регістру w |

1 |

Не діє |

|||

|

|

|

|

|

||

retfie |

Повернення з процедури |

обробки |

2 |

Не діє |

||

переривання |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|||

retlw k |

Повернення з процедури та пересилання |

2 |

Не діє |

|||

константи k до регістру w |

|

|

||||

|

|

|

|

|

||

|

|

|

|

|

|

|

return |

Повернення з процедури |

|

|

2 |

Не діє |

|

|

|

|

|

|

|

|

26

Продовження табл. Д.1

1 |

2 |

3 |

4 |

|

|

|

|

|

|

sleep |

Перехід в режим енергозбереження |

1 |

TO, PD |

|

|

|

|

|

|

sublw k |

Віднімання регістру w від константи k |

1 |

C, DC, Z |

|

|

|

|

|

|

xorlw k |

Логічне ″Виключне АБО″ регістру w та |

1 |

Z |

|

константи k |

||||

|

|

|

||

|

|

|

|

* – тривалість зазначено у машинних циклах (1 машинний цикл дорівнює 4

періодам тактової частоті мікроконтролеру); ** – якщо виконується пропуск наступної команди, то тривалість дорівнює

2 машинним циклам, в іншому випадку – 1 машинному циклу.

Список умовних позначень f – адреса регістру (від 0x00 до 0xFF);

w – робочий регістр;

b – номер біта у 8-розрядному регістрі (від 0 до 7); k – константа (дані або мітка);

d – покажчик адресата результату операції:

якщо d=0 (замість 0 може використовуватись символ w), то результат збережуться у регістрі w,

якщо d=1 (замість 0 може використовуватись символ f), то результат

збережуться у регістрі f (за замовчанням d=1);

C – прапор перенесення/позики;

DC – прапорець десяткового перенесення/позики;

Z – прапорець нульового результату;

PD – прапорець ввімкнення живлення;

TO – прапорець переповнення сторожового таймеру.

27