БДЗ / BDZ_2_otchyot_demo

.docxЗадание на семестр

по курсу «СБИС для ТКС»

Второй этап

Таблица 1. Данные варианта

№ |

Архитектура |

Разрядность, бит |

Частота дискретизации, не менее |

ENOB, бит, не менее |

Ток потребления, не более |

Fully differential |

5 |

SAR |

9 |

50 кГц |

8 |

0,9 мА |

Да |

Теория

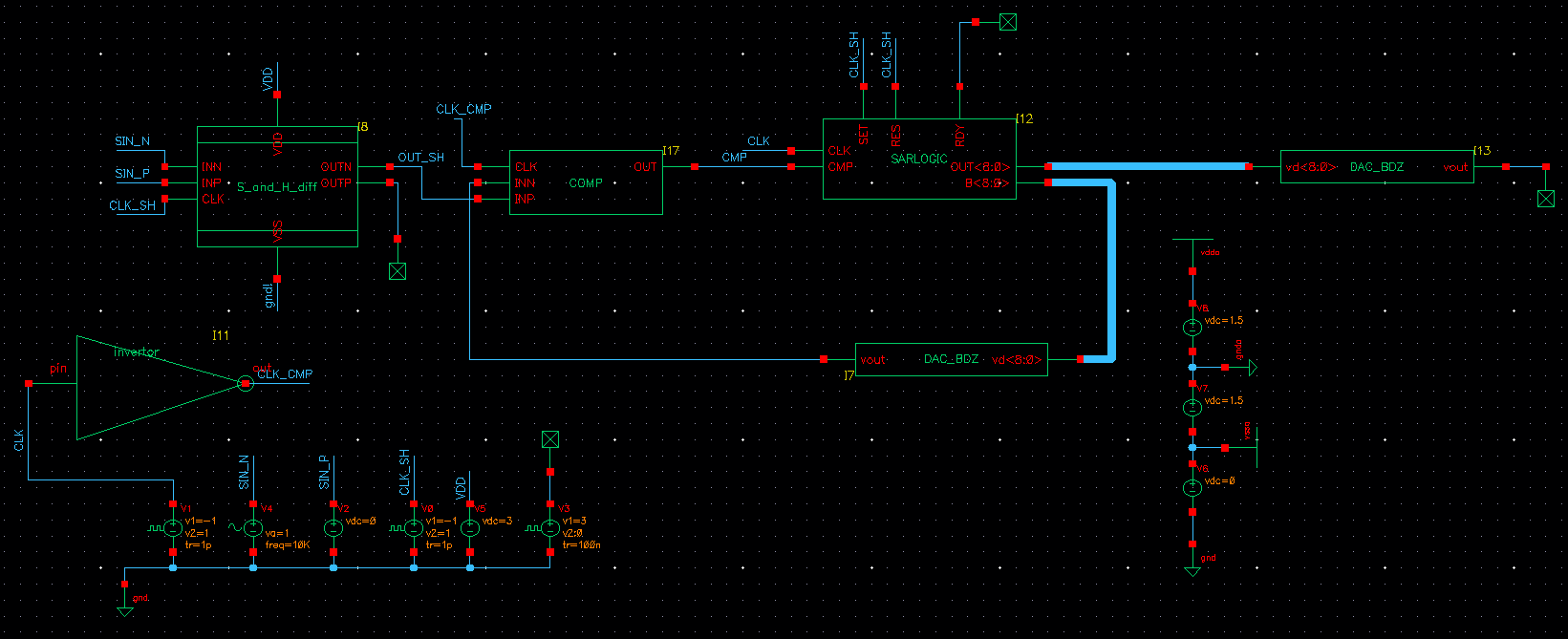

АЦП SAR состоит из трех основных частей: цифро-аналогового преобразователя и S&H, компаратора и логики SAR. Прежде чем углубляться в характеристики устройств, входящих в состав АЦП последовательного приближения, давайте разберемся, как выполняется преобразование с помощью алгоритма последовательного приближения с учетом архитектуры, показанной на рис. 1. Преобразование выполняется в течение нескольких тактов, начиная с MSB. Информация, полученная в каждом тактовом периоде, затем используется для генерации следующего значимого бита. В начале преобразования входное напряжение измеряется схемой S&H. На следующем шаге определяется старший бит, сравнивая дискретизированное напряжение с половиной диапазона полной шкалы. Опорное напряжение компаратора обеспечивается ЦАП, управляемым логической схемой. В зависимости от выхода компаратора старший бит будет равен «0» или «I», и он будет сохранен в регистре SAR в логической схеме. Из оценки MSB можно определить, в какой половине бинарного дерева поиска должно быть установлено следующее опорное напряжение. Фактически это означает, что дискретизированный сигнал сравнивается с V/4 или 3V/4 соответственно. Эта процедура повторяется для каждого бита до младшего разряда.

Следующие подразделы посвящены описанию блоков, образующих АЦП последовательного приближения, на основе топологий, найденных в литературе.

Устройство выборки и хранения – схема, запоминающая напряжение на входе в определённый момент времени. Устройство, представленное на схеме АЦП, получает два информационных сигнала на негативный и позитивный вход соответственно, а также управляющий сигнал. Управляющий сигнал представляет собой тактовый сигнал, который при переходе по фронту через 0 запоминает напряжения информационных сигналов. На выходы поступает разность этих напряжений. Таким образом, устройство выборки и хранения, представленное на схеме, фиксирует значения напряжений поступающих на него информационных сигналов в определённые моменты времени, и подаёт на выход их разность.

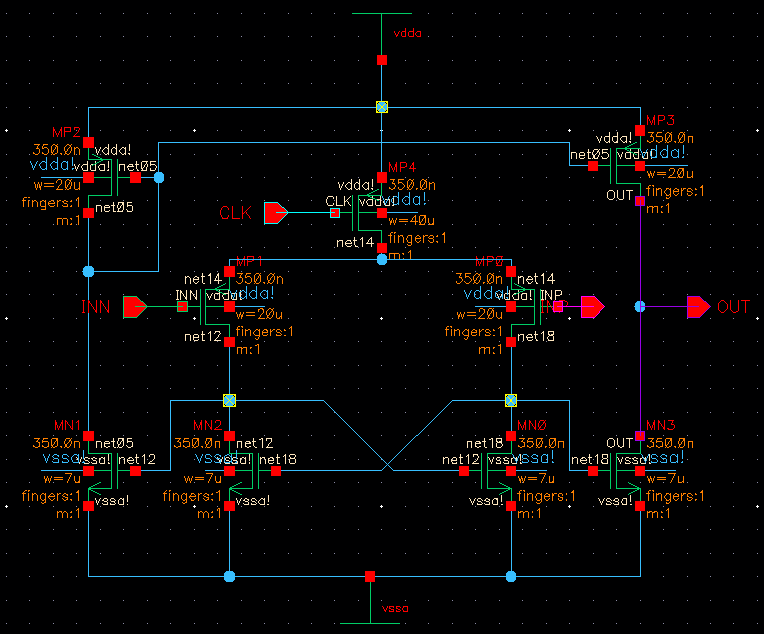

Компаратор имеет три входа (два для сигналов и тактовый) и один выход для результирующего сигнала. Компаратор работает следующим образом: по фронту тактового сигнала происходит сравнение входных сигналов, при наличии на инверсном входе -1 и на неинверсном +1, на выходе устанавливается 1, во всех остальных случаях устанавливается -1.

Схема SAR АЦП

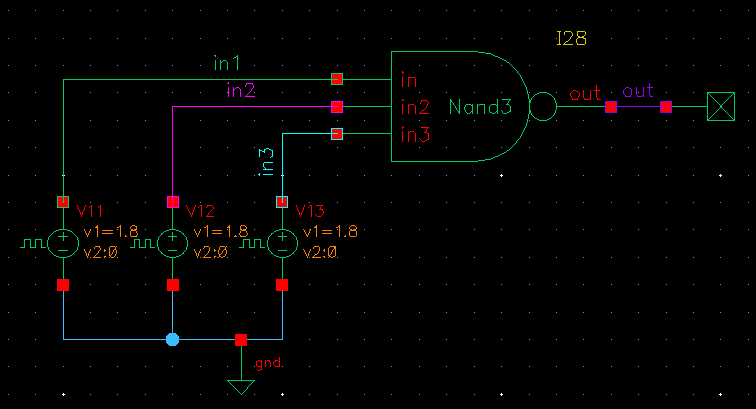

Рисунок 1 – 3И-НЕ, собранный на транзисторах

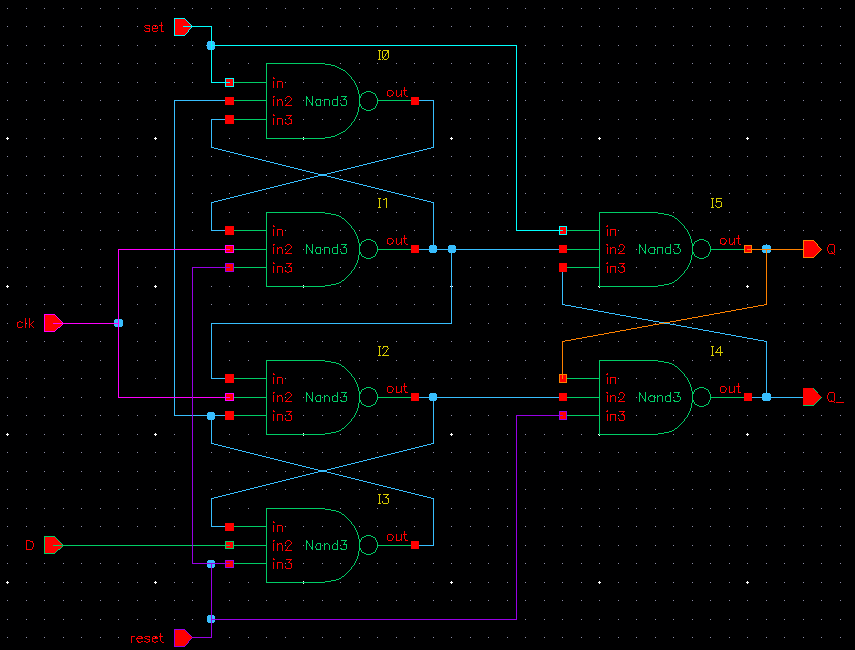

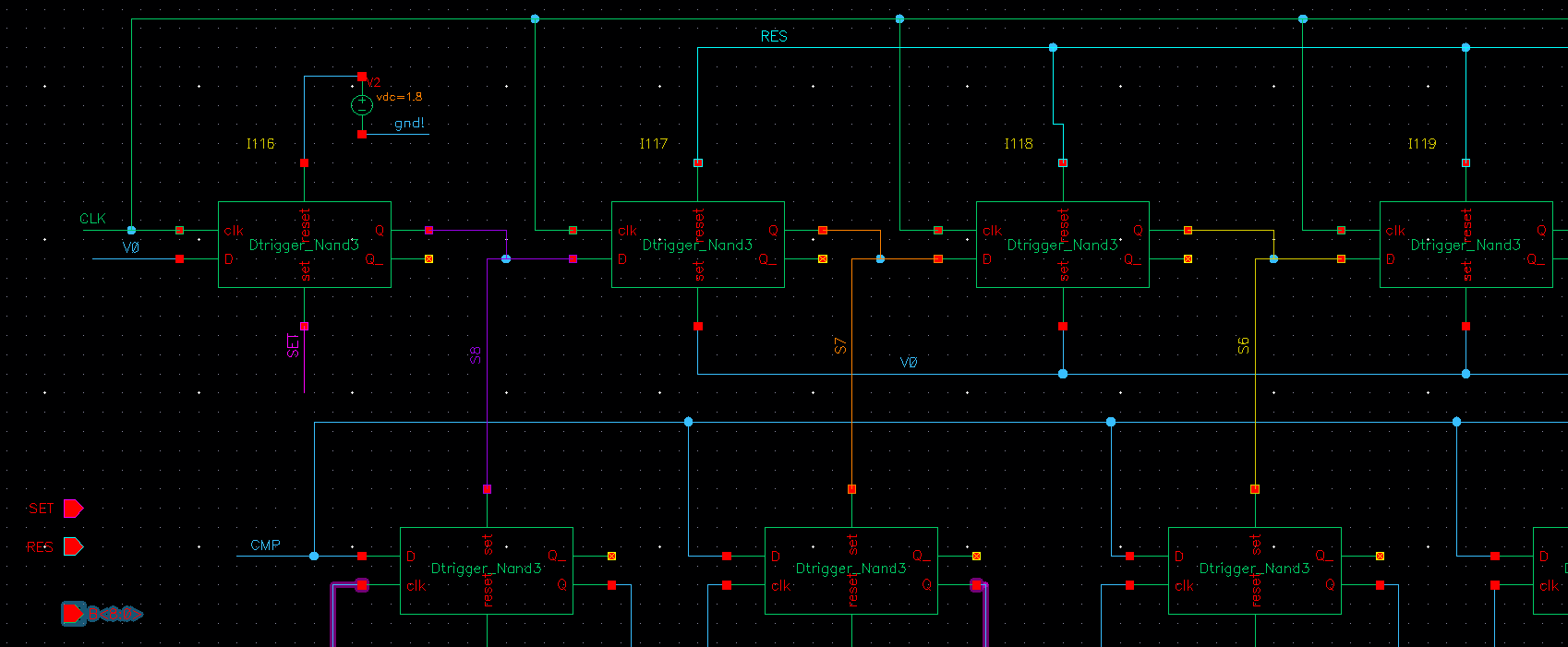

Рисунок 2 – Д-триггер, собранный из логических вентилей 3И-НЕ

Рисунок 3 – Тестирование 3И-НЕ вентиля

Рисунок 4 – результат тестирования 3И-НЕ вентиля

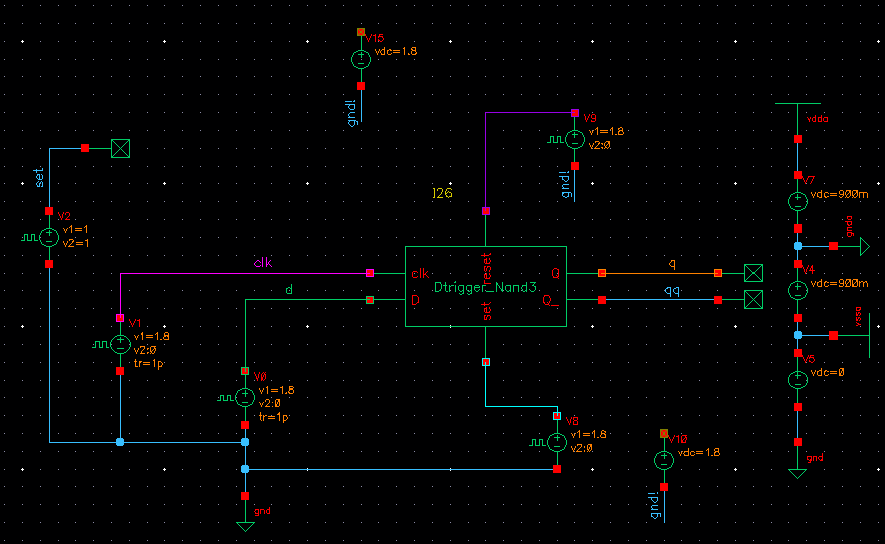

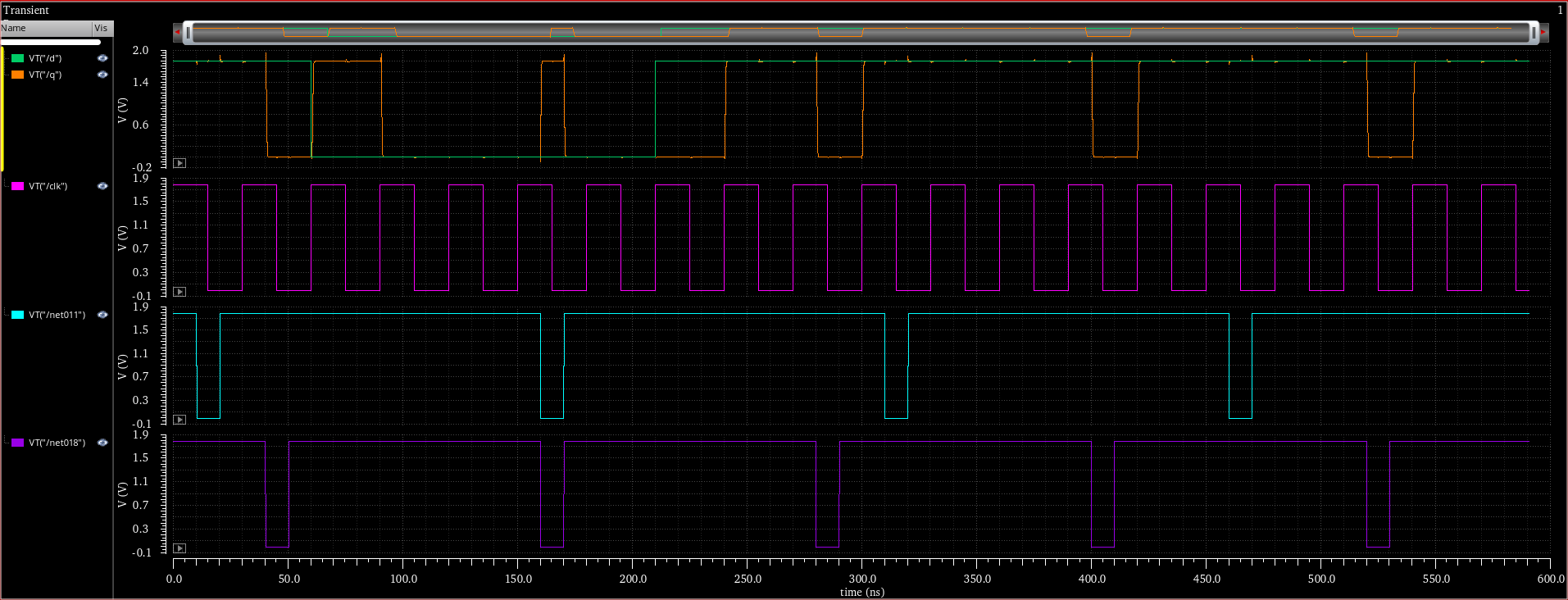

Рисунок 5 – Тестирование Д-триггера

Рисунок 6 – Графики, полученные в результате тестирования Д-триггера

Set (бирюзовый, третий) и Reset (фиолетовый, четвёртый) работают по спаду. Clk работает по фронту.

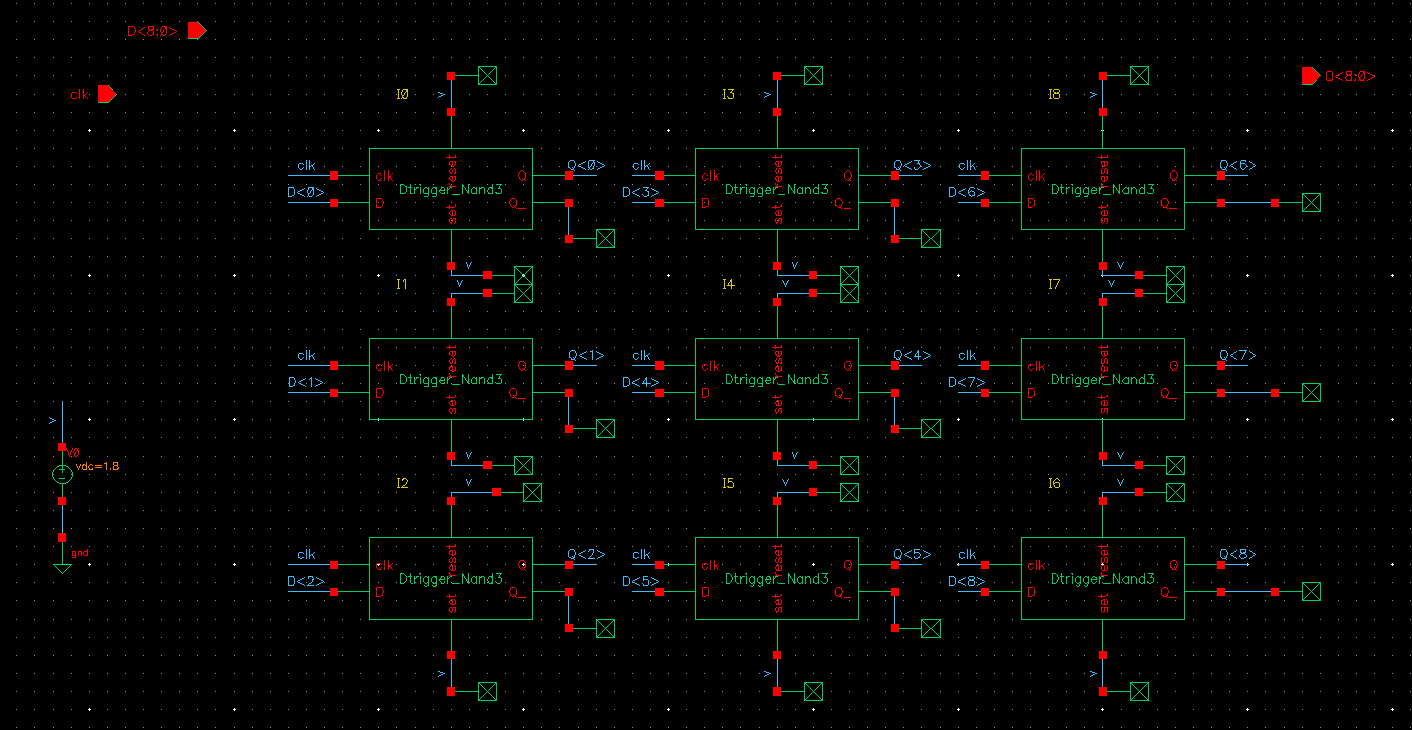

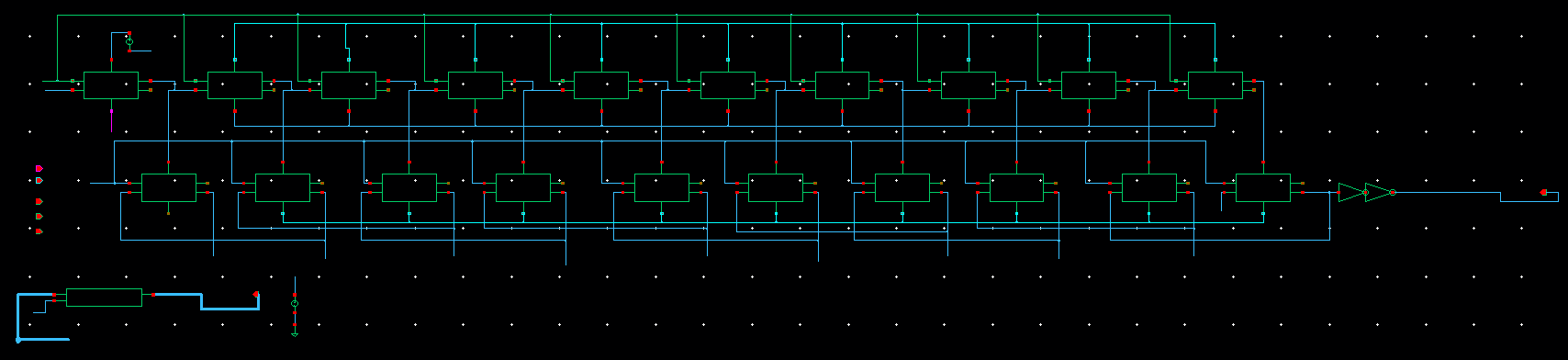

Массив из 9 д-триггеров

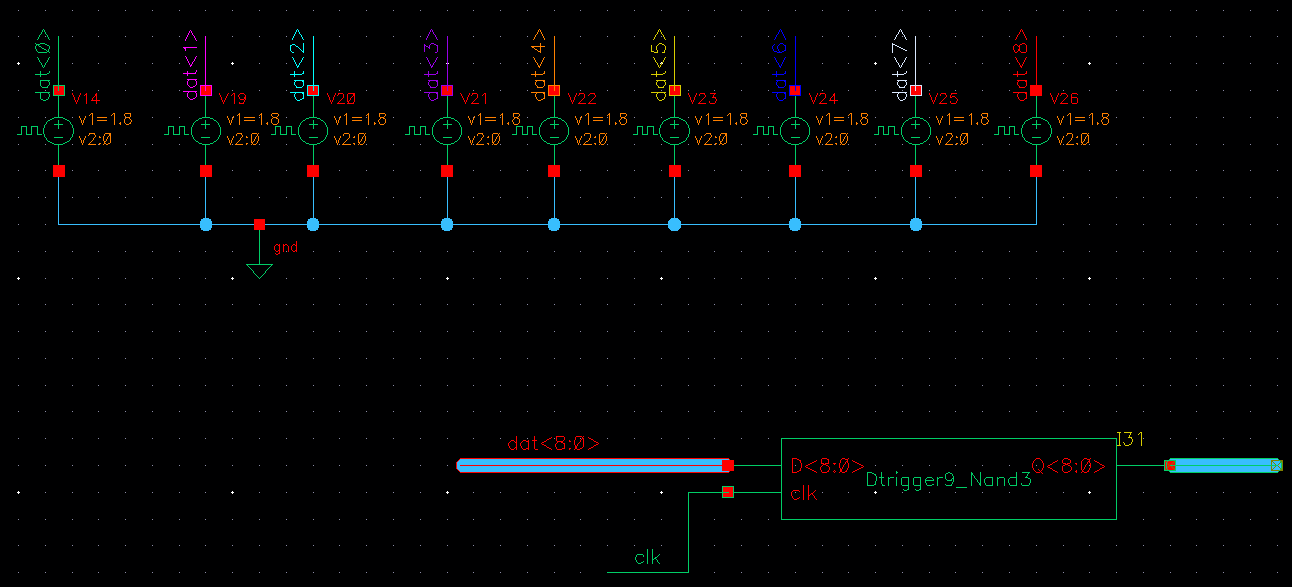

Тестирование массива

График тестирования массива

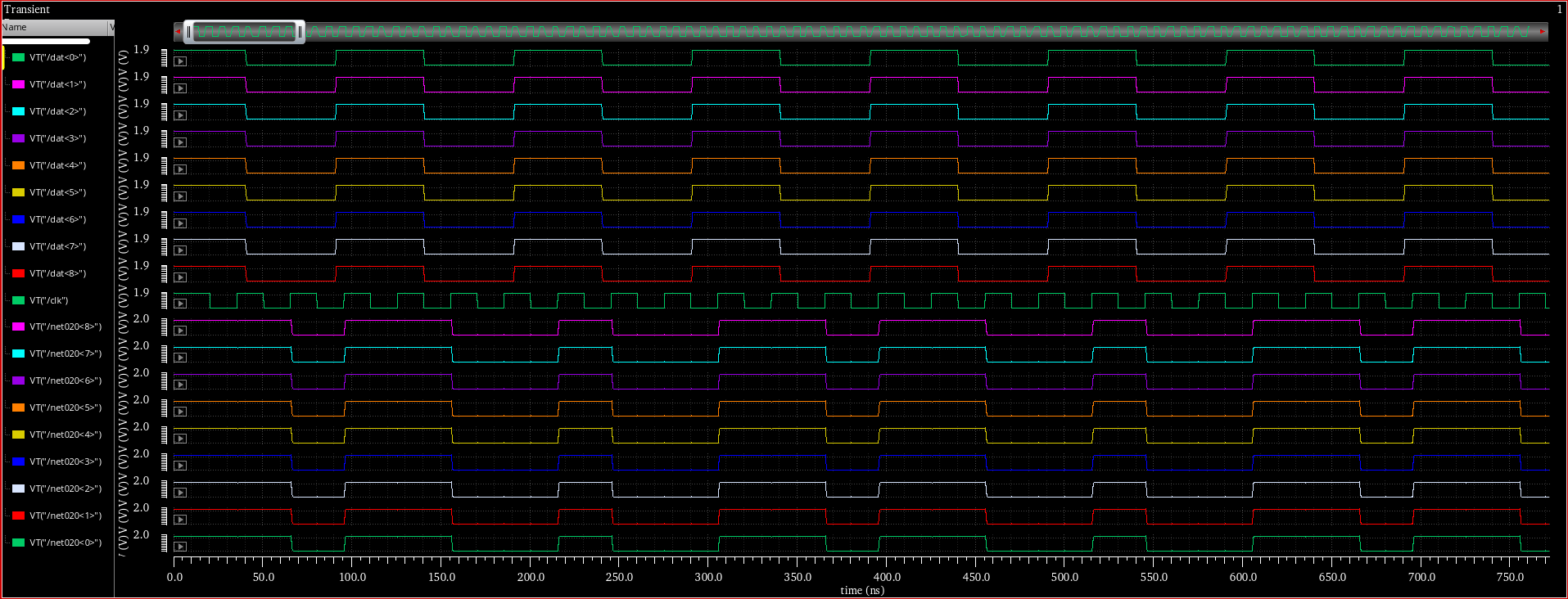

SAR-логика

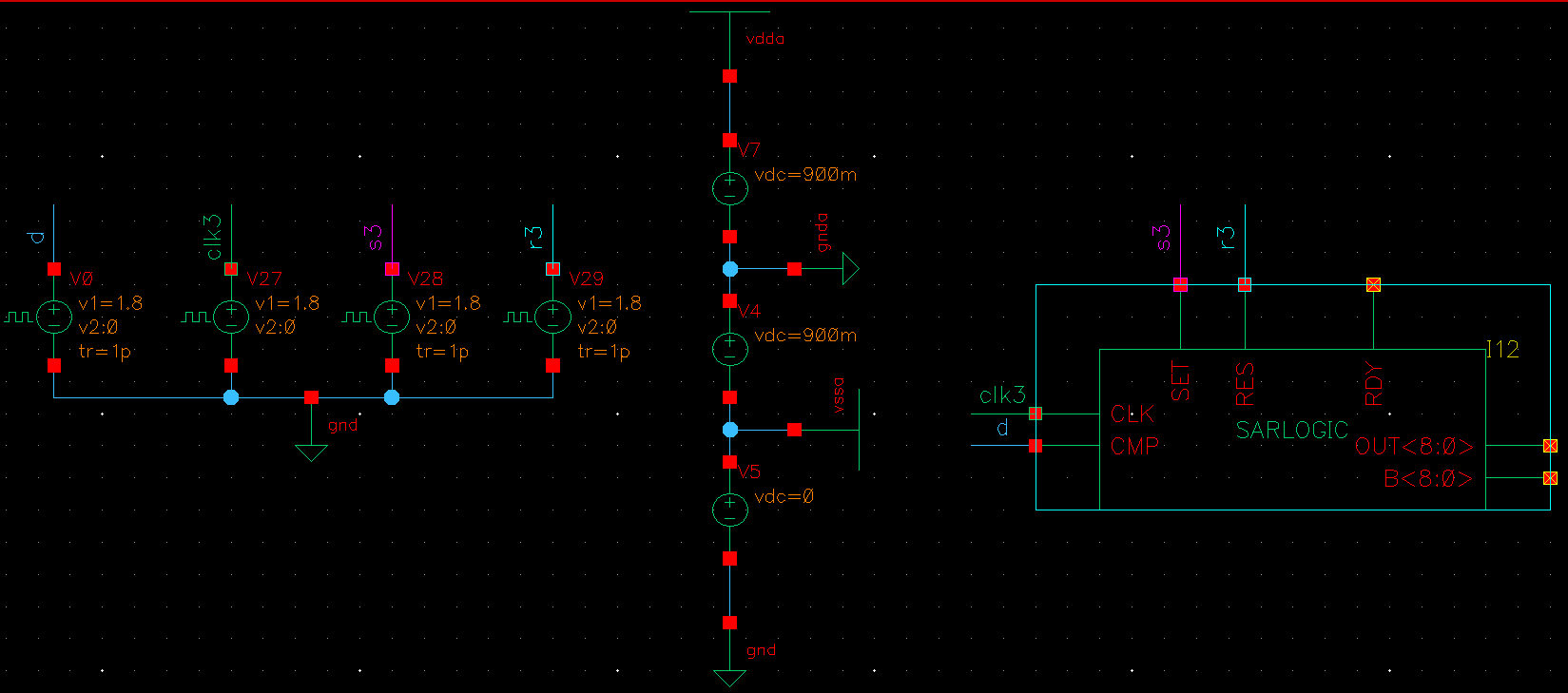

Тестирование SAR-логики

Тестирование SAR-логики часть 2

Результаты тестирования SAR-логики

Компаратор с гистерезисом

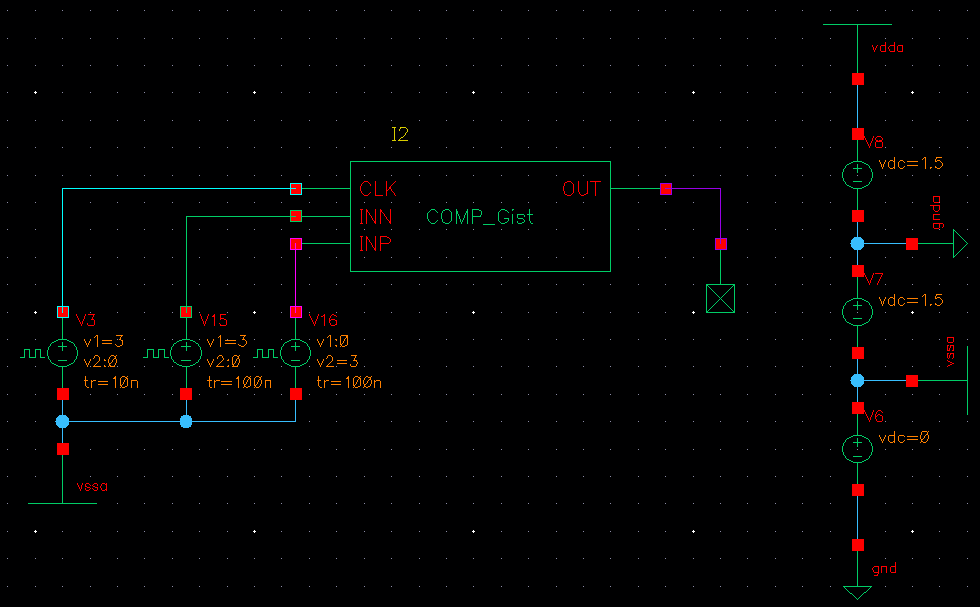

Тестирование компаратора с гистерезисом

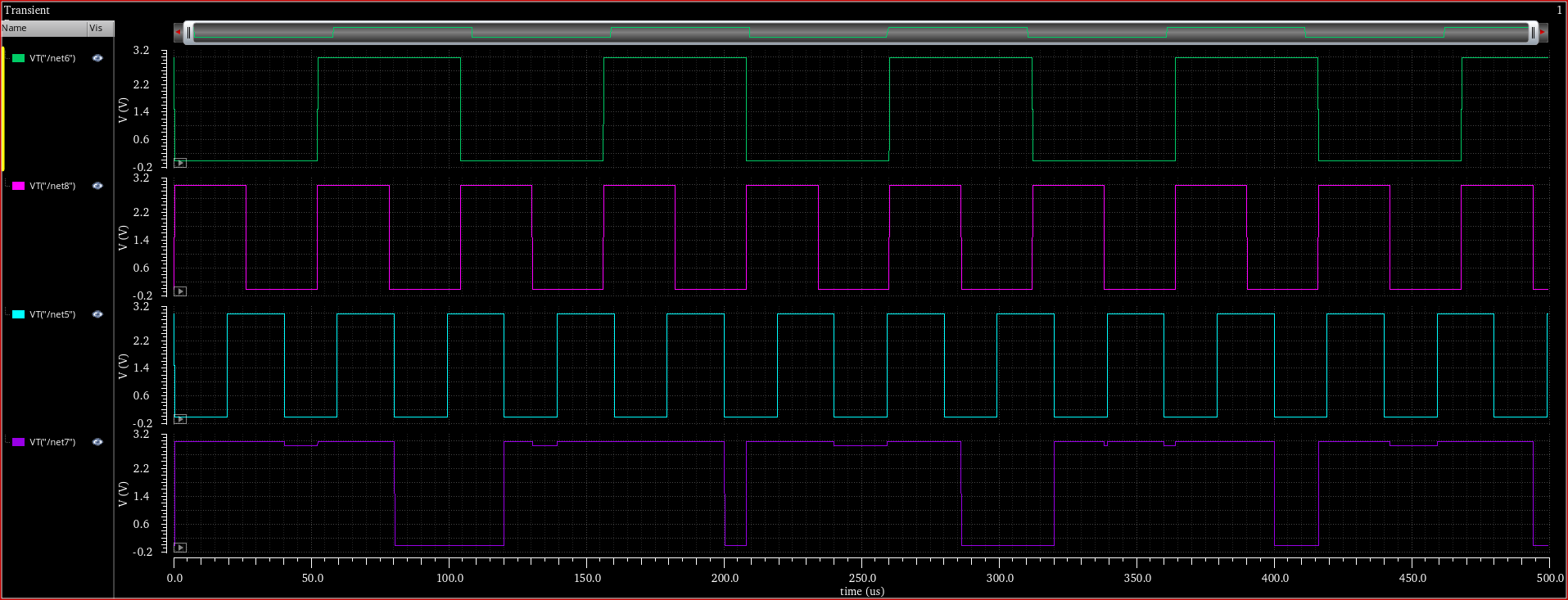

Результаты тестирования компаратора с гистерезисом

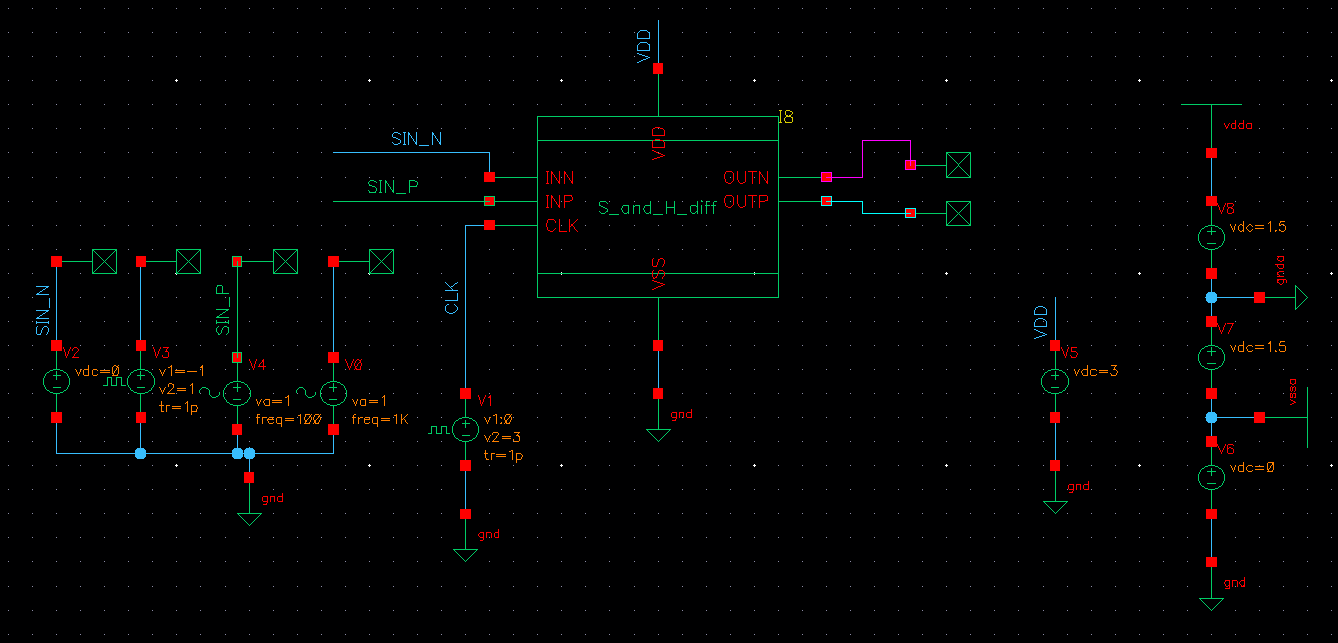

Тестирование устройства выборки и хранения

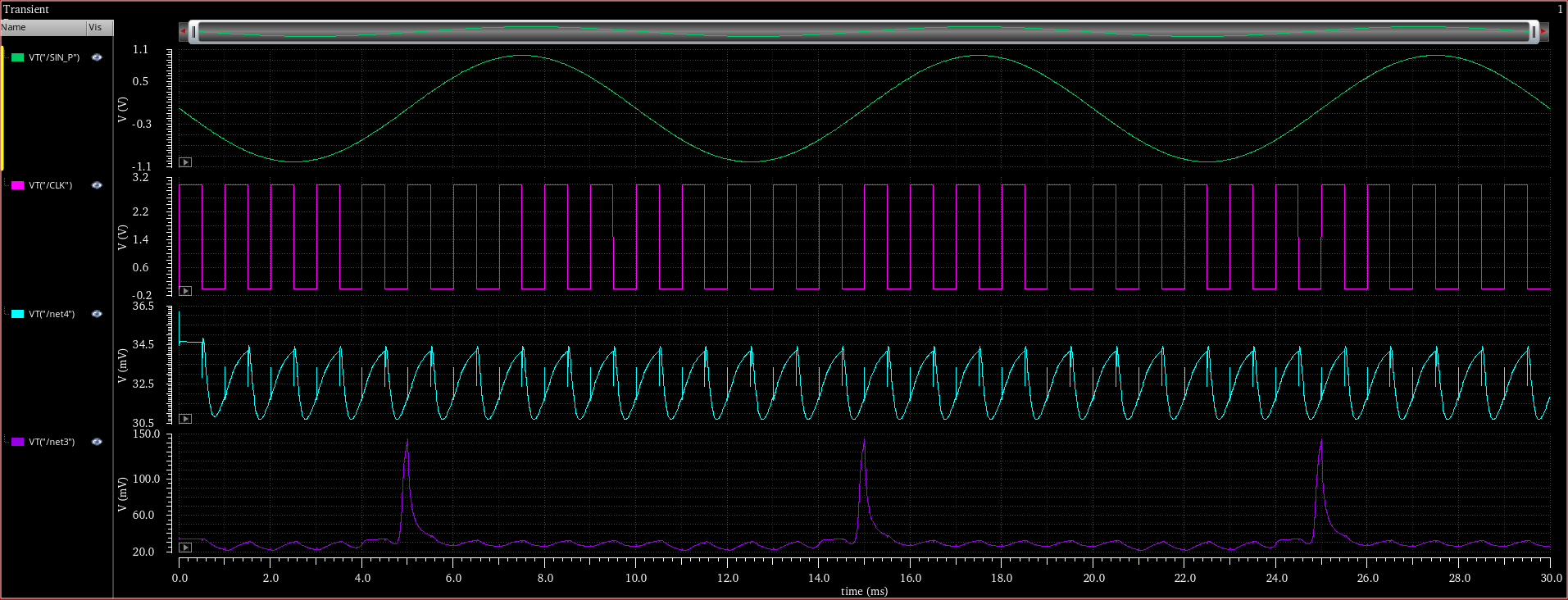

Результаты тестирования устройства выборки и хранения

Как можно заметить, устройство выборки и хранения не работает. Мы пришли к выводу, что причина этому – ключи в его схеме.

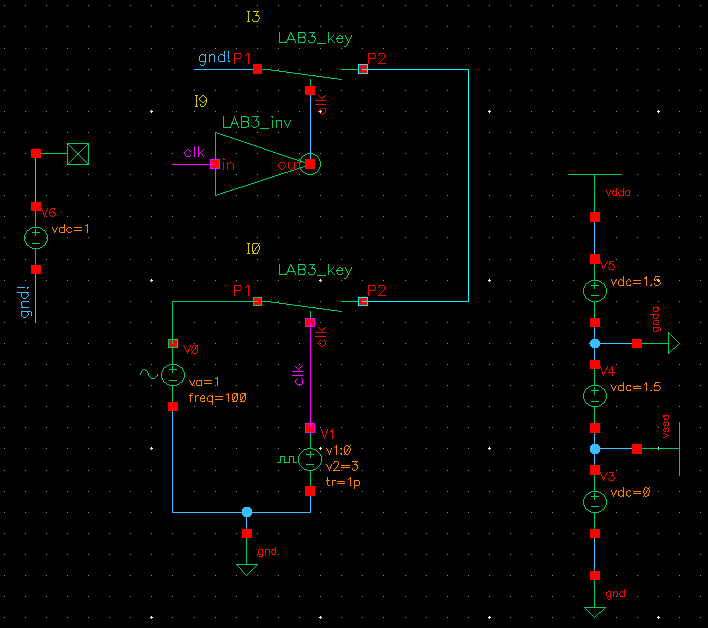

Схема тестирования ключа

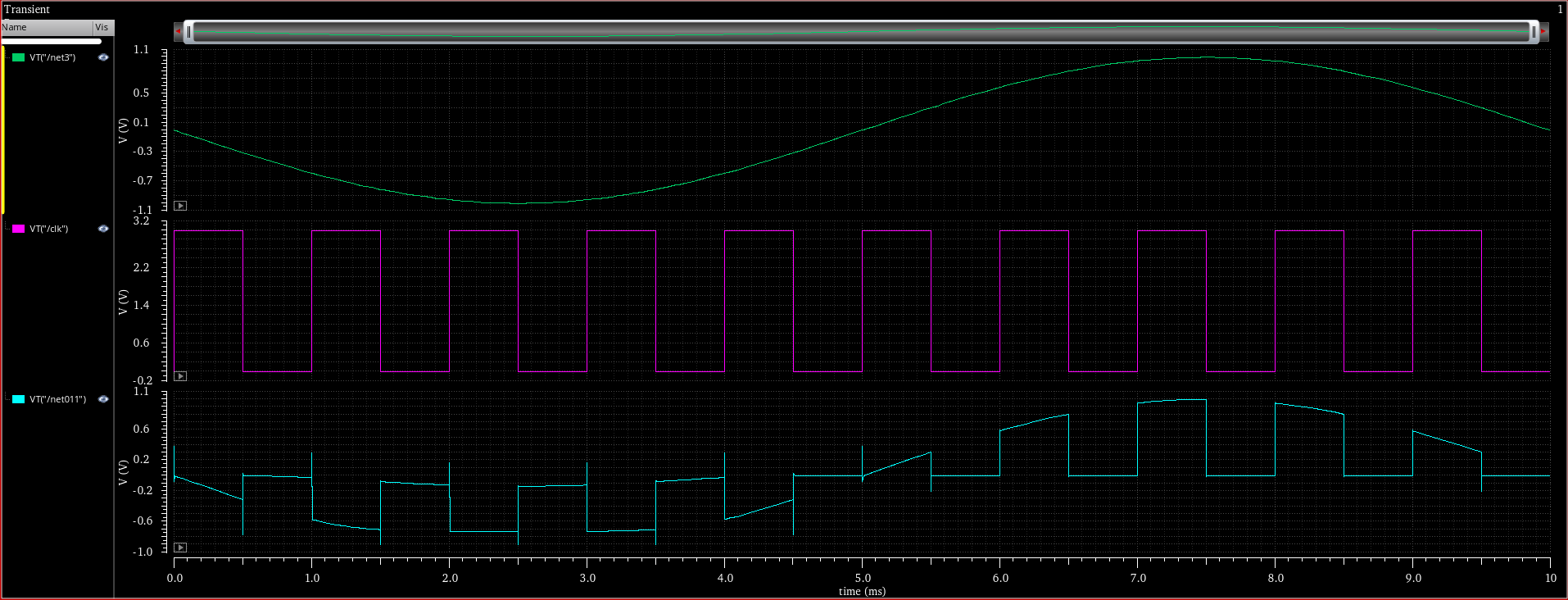

Результаты тестирования ключа

Вывод

В ходе выполнения второго этапа задания на семестр нами была создана модель АЦП последовательного приближения на транзисторах. Были созданы блоки схемы выборки и хранения, компаратора. SAR-логика была собрана из д-триггеров со входами Set и Reset по схеме из статьи T.O. Андерсона «Optimum Control Logic for Successive Approximation Analog-to-Digital Converter». Д-триггеры в свою очередь собраны из логических вентилей NAND3, собранные на КМДП транзисторах. По результатам работы можно сделать вывод, что собранная схема работает не совсем корректно, однако, отдельные блоки работают корректно.