экз

.pdf

Олкли 13

(Задания::

1.Опишите маршрут проектирования устройств на основе ПЛИС.

2.Опишите на Verilog HDL 8-разрядный буфер с третьим состоянием, расскажите о его назначении. Проиллюстрируйте его работу с помощью временных диаграмм.)

(Вся вторая лекция презентации и пятая текстовая лекция из ОРИОКСа)

№1-

Маршрут проектирования – последовательность действий и процессов, приводящих к получению устройства, соответствующего заданным

требованиям

(ПОЯСНЕНИЯ К ПУНКТАМ):

1)Получение и/или анализ технического задания: на этом этапе определяются требования к устройству, его функциональность, производительность, интерфейсы и другие параметры. Также анализируются возможные ограничения, такие как бюджет, время разработки, доступность компонентов и т.д.

2)Создание нового проекта: на этом этапе выбирается семейство ПЛИС и тип устройства, которые наилучшим образом соответствуют требованиям технического задания. Также выбираются средства синтеза, которые будут использоваться для создания описания устройства на языке Verilog HDL или другом языке описания аппаратуры.

3)Подготовка описания проектируемого устройства в графической и/или текстовой форме: на этом этапе создается описание проектируемого устройства, включающее в себя блок-схемы, диаграммы и другие графические элементы, а также текстовое описание его функциональности и характеристик.

4)Функциональное моделирование: на этом этапе создается модель устройства, которая позволяет проверить его функциональность и корректность работы. Моделирование проводится с помощью специальных программных средств, которые позволяют проверить работу устройства в различных условиях.

5)Синтез: на этом этапе создается файл описания устройства на языке Verilog HDL или другом языке описания аппаратуры. Этот файл содержит описание логической структуры устройства и его функциональности.

6)Верификация: на этом этапе проводятся тесты и симуляции для проверки корректности работы устройства. Верификация позволяет выявить ошибки и недочеты в работе устройства на ранних этапах разработки.

7)Размещение и трассировка проекта в кристалле: на этом этапе происходит размещение компонентов на ПЛИС и проведение маршрутизации сигналов между ними. Это позволяет оптимизировать расположение компонентов и сигнальных линий для достижения максимальной производительности устройства.

8)Верификация: на этом этапе проводятся тесты для проверки корректности работы устройства после размещения и маршрутизации. Верификация на этом этапе позволяет выявить ошибки, связанные с размещением и маршрутизацией компонентов.

9)Программирование ПЛИС: на этом этапе создается файл конфигурации ПЛИС, который содержит информацию о расположении компонентов и сигнальных линий. Этот файл загружается в ПЛИС для конфигурации устройства.

10)Отладка на аппаратном уровне: на этом этапе проводятся тесты и проверки на аппаратном уровне для проверки корректности работы устройства. Отладка может включать в себя измерение времени отклика, потребляемой мощности, работы интерфейсов и других параметров.

11)Получение проекта, соответствующего заданной спецификации: на этом этапе происходит окончательная проверка устройства и его соответствия

требованиям технического задания. Если устройство соответствует спецификации, то оно готово к производству и выпуску на рынок.

№2

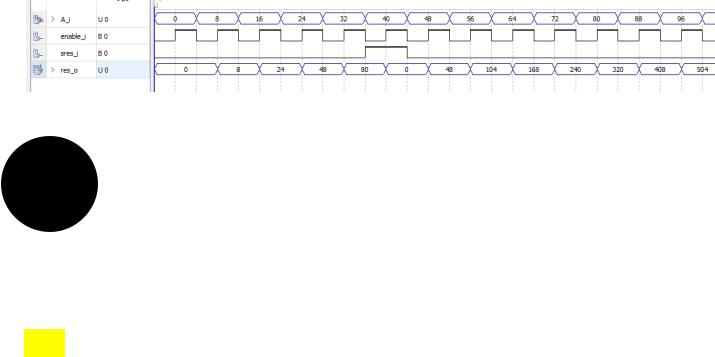

Модуль 8-разрядного буфера с третьим состоянием на Verilog HDL может быть описан следующим образом:

verilog

module tri_state_buffer(input [7:0] data_in, // входные данные input enable, // сигнал разрешения

output reg [7:0] data_out); // выходные данные

// объявляем сигнал состояния reg tri_state;

always @(*) begin |

|

if (enable) begin |

|

tri_state = 1'b0; |

// если разрешение активно, то устанавливаем сигнал |

состояния в 0 |

|

data_out = data_in; // и передаем входные данные на выход |

|

end else begin |

|

tri_state = 1'b1; |

// если разрешение неактивно, то устанавливаем сигнал |

состояния в 1 |

|

data_out = 8'bz; |

// и передаем третье состояние на выход |

end |

|

end |

|

// объявляем триггер на изменение сигнала состояния always @(posedge tri_state) begin

data_out <= 8'bz; // при изменении состояния устанавливаем третье состояние на

выходе end

endmodule

Назначение данного модуля заключается в том, чтобы создать буфер данных, который

может быть выключен (отключен) по команде.

Если сигнал разрешения enable активен, то входные данные data_in будут

передаваться на выход data_out.

Если же сигнал разрешения неактивен, то на выходе data_out будет установлено

третье состояние (8'bz), что означает отключение выхода.

Это позволяет избежать конфликтов на шине данных, когда несколько устройств

пытаются передавать данные одновременно.

Таким образом, 8-разрядный буфер с третьим состоянием является важным элементом в системах, где нужно обеспечить правильную передачу данных между устройствами.

Карпухин 14

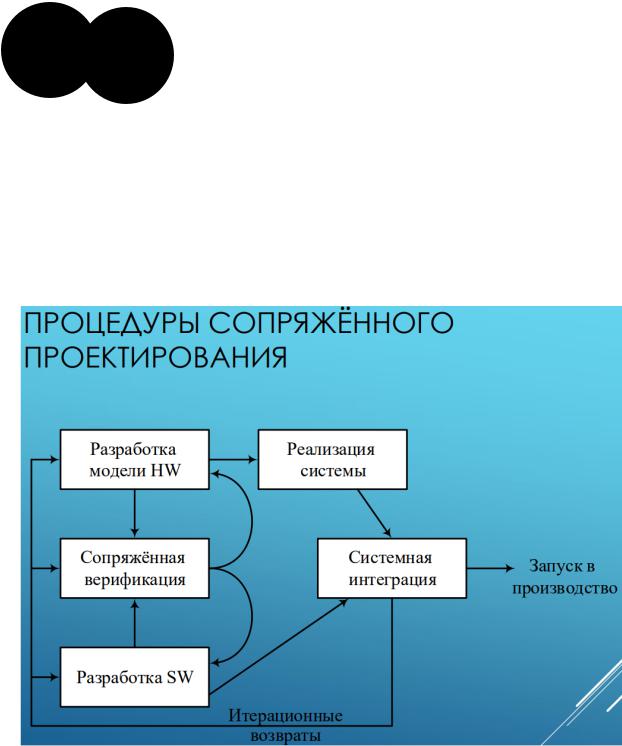

Опишите проблемы сопряженного проектирования систем на основе ПЛИС Идея сопряженного проектирования состоит в том, чтобы попытаться совместить

проектирование аппаратной и программной частей проекта, обеспечив проверку совместного функционирования на ранних этапах проектирования с помощью моделей

в одной системе проектирования.

Сопряженное проектирование - процесс параллельного проектирования аппаратных и программных средств, при котором осуществляется оценка целесообразности выбора аппаратной или программной реализации определенного фрагмента проекта. Этот процесс также дает разработчикам возможность увидеть (на абстрактном уровне - модель), как система могла бы работать с данным разделением аппаратных средств и программного обеспечения.

SW - software HW - hardware

Проблемы:

1.Создание новых средств и методологии проектирования.

Требуется ввести средства описания проекта, которые сглаживают различия между HW и SW реализациями

2.Требуется обеспечить систематическое повторное использование базовых элементов проектов.

Нужно наращивать количества и качества проверенных блоков. Улучшать документации разработанных блоков. Снабжать IP блоки средствами тестирования и отладки

3.Использовать передовые САПР.

Требуется изменить подход к проектированию с помощью САПР: графические интерфейсы, позволяющие наглядно распределять задачи между HW и SW, но при этом позволяющие проводить тонкую настройку каждой из частей и одновременно оценивать влияние каждой из частей на свойства (быстродействие, энергопотребление, аппаратные затраты) системы в целом

4.Введение новых и модернизация существующих стандартов с целью повышения их эффективности Будущие стандарты должны обеспечить сопряжение разнородных устройств на

различных уровнях разработки: системном, логическом и физическом

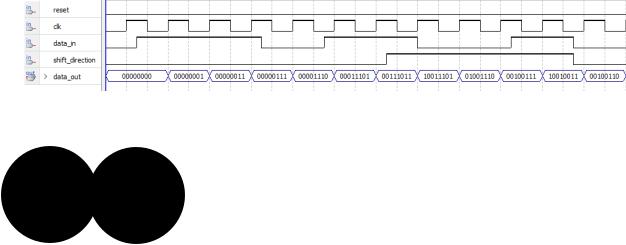

Задача: Опишите на Verilog HDL 8-разрядный сдвиговый регистр при помощи

процедурного присваивания и оператора объединения, реализовав возможность

выбора направления сдвига. Проиллюстрируйте его работу с помощью временных

диаграмм.

module shiftreg ( |

|

input wire clk, |

// входной тактовый сигнал |

input wire reset, |

// сигнал сброса |

input wire shift_direction,// направление сдвига (0 - влево, 1 - вправо)

input wire data_in, |

// |

входные данные для сдвига |

output reg [7:0] data_out |

// выходные данные |

|

); |

|

|

reg [7:0] shift_reg; |

// 8-разрядный сдвиговый регистр |

|

always @(posedge clk or posedge reset) begin |

||

if (reset) |

|

|

shift_reg <= 8'b0; |

// сброс регистра при активном сигнале reset |

|

else begin |

|

|

// Процедурное присваивание с учетом направления сдвига |

||

if (shift_direction) |

|

|

shift_reg <= {data_in, shift_reg[7:1]}; |

// сдвиг вправо |

|

else |

|

|

shift_reg <= {shift_reg[6:0], data_in}; |

// сдвиг влево |

|

end |

|

|

data_out <= shift_reg; // обновление выходных данных end

endmodule

(Времянку можно сократить если лень рисовать, главное показать, что когда приходит сигнал shift_deriction в регистр data_out, значения начинают вдвигаться с другой стороны)

Васильев 15

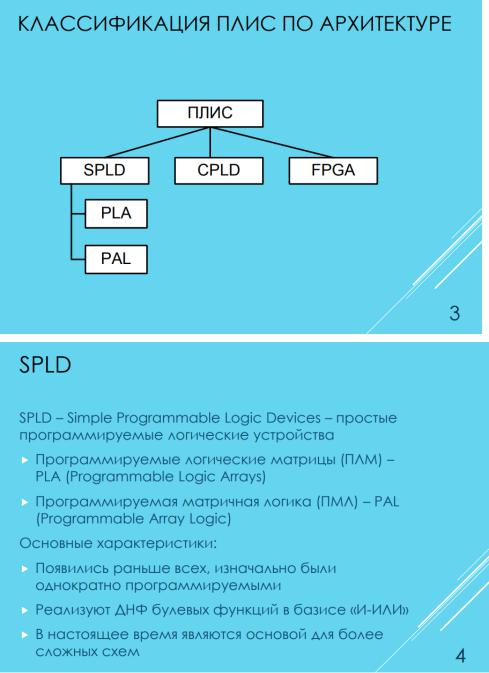

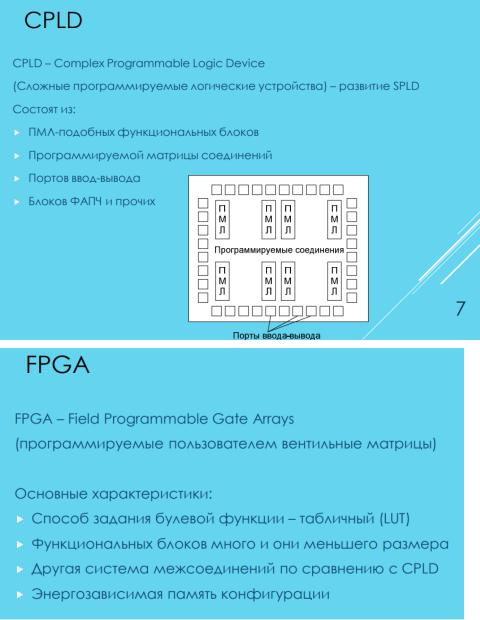

Теория:Приведите классификацию ПЛИС по архитектурным признакам. Опишите каждый из приведенных классов

PLA - Появились первыми в 1970 году, были однократно программируемыми, затем

стали многократно программируемыми

PAL - Появились как упрощение ПЛМ путём исключения программируемости матрицы «ИЛИ», первые выпущены в 1978 году

Задача: Опишите на Verilog HDL 8-разрядный сдвиговый регистр с синхронным сбросом и асинхронной параллельной загрузкой при помощи процедурного присваивания и оператора объединения. Проиллюстрируйте его работу с помощью временных диаграмм.

module ShiftRegister (

input clk, |

// входной тактовый сигнал |

input reset, |

// входной сигнал сброса |

input parallel_load,// входной сигнал асинхронной параллельной загрузки input [7:0] data_in,// входные данные для загрузки

output reg [7:0] q // выходные данные регистра

);

always @(posedge clk or posedge parallel_load) begin if (parallel_load) begin

q <= data_in; // асинхронная параллельная загрузка end else if (reset) begin

q <= 8'b0; // синхронный сброс, обнуляем регистр end else begin

q <= {q[6:0], q[7]}; // сдвигаем данные влево end

end endmodule

В этом коде используется блок always @(posedge clk or posedge reset), который реагирует на положительный фронт тактового сигнала clk или положительный фронт сигнала сброса reset. Если сигнал сброса reset активен, то регистр обнуляется. Если сигнал асинхронной параллельной загрузки parallel_load активен, данные data_in

загружаются в регистр. В противном случае данные в регистре сдвигаются влево на один разряд.

Муравьев 16

БИЛЕТ К ДИФФЕРЕНЦИАЛЬНОМУ ЗАЧЕТУ № 16 по курсу: «Программируемые логические интегральные схемы»

1. Опишите метод граничного сканирования при помощи интерфейса JTAG.