ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ ОБРАЗОВАТЕЛЬНОЕ

УЧРЕЖДЕНИЕ ВЫСШЕГО ОБРАЗОВАНИЯ

«САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ

ТЕЛЕКОММУНИКАЦИЙ ИМ. ПРОФ. М.А. БОНЧ-БРУЕВИЧА»

(СПбГУТ)

ФАКУЛЬТЕТ ИНФОКОММУНИКАЦИОННЫХ СЕТЕЙ И СИСТЕМ (ИКСС)

КАФЕДРА ПРОГРАММНОЙ ИНЖЕНЕРИИ И ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ (ПИ И ВТ)

ДИСЦИПЛИНА: «Архитектура вычислительных система»

Лабораторная работа №1.

Проектирование двухмодульного КЦУ в CycloneV

Выполнили:

Цыганков М.А.

Козлов Н.С.

Тюришев М.А.

Подпись____________

Принял:

Неелова Л.О.

Подпись____________

«_____»________2021

Санкт-Петербург

2021

Цель работы: изучение методов проектирования линейных схем в ПЛИС с использованием пакетов Modelsim и Quartus 15.

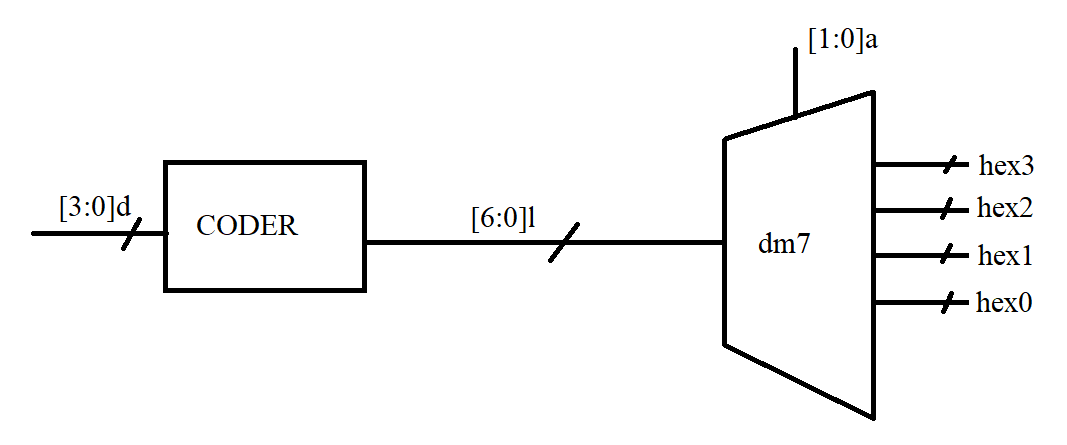

Задание: спроектировать устройство, преобразующее 4-разрядные данные, подоваемые с тумблеров макета DE1-SoC в код для семисегментного индикатора, с возможностью вывода числа на один из четырёх индикаторов макета, выбираемого по вводимому с тумбоеров адресу.

Файл

dms.v

Файл

dms.v

module dms7 (input wire [6:0] line, input wire [1:0] adr, output wire [6:0] data0, output wire [6:0] data1, output wire [6:0] data2, output wire [6:0] data3); assign data0 = (adr == 2'h0)? line: 7'h7f; assign data1 = (adr == 2'h1)? line: 7'h7f; assign data2 = (adr == 2'h2)? line: 7'h7f; assign data3 = (adr == 2'h3)? line: 7'h7f; endmodule |

Файл testbench_dms7.v

`timescale 1ns/10ps module dms_tb; reg [1:0] test_addres; reg [6:0] tb_line; wire [6:0] test_data0; wire [6:0] test_data1; wire [6:0] test_data2; wire [6:0] test_data3; dms7 test(.data0(test_data0),.data1(test_data1),.data2(test_data2),.data3(test_data3),.line(tb_line),.adr(test_addres)); initial begin test_addres = 2'h0; tb_line=7'h0; #100; tb_line=7'hf; #100; test_addres = 2'h1; tb_line=7'h0; #100; tb_line=7'hf; #100; test_addres = 2'h2; tb_line=7'h0; #100; tb_line=7'hf; #100; test_addres = 2'h3; tb_line=7'h0; #100; tb_line=7'hf; #100 $stop; end endmodule |

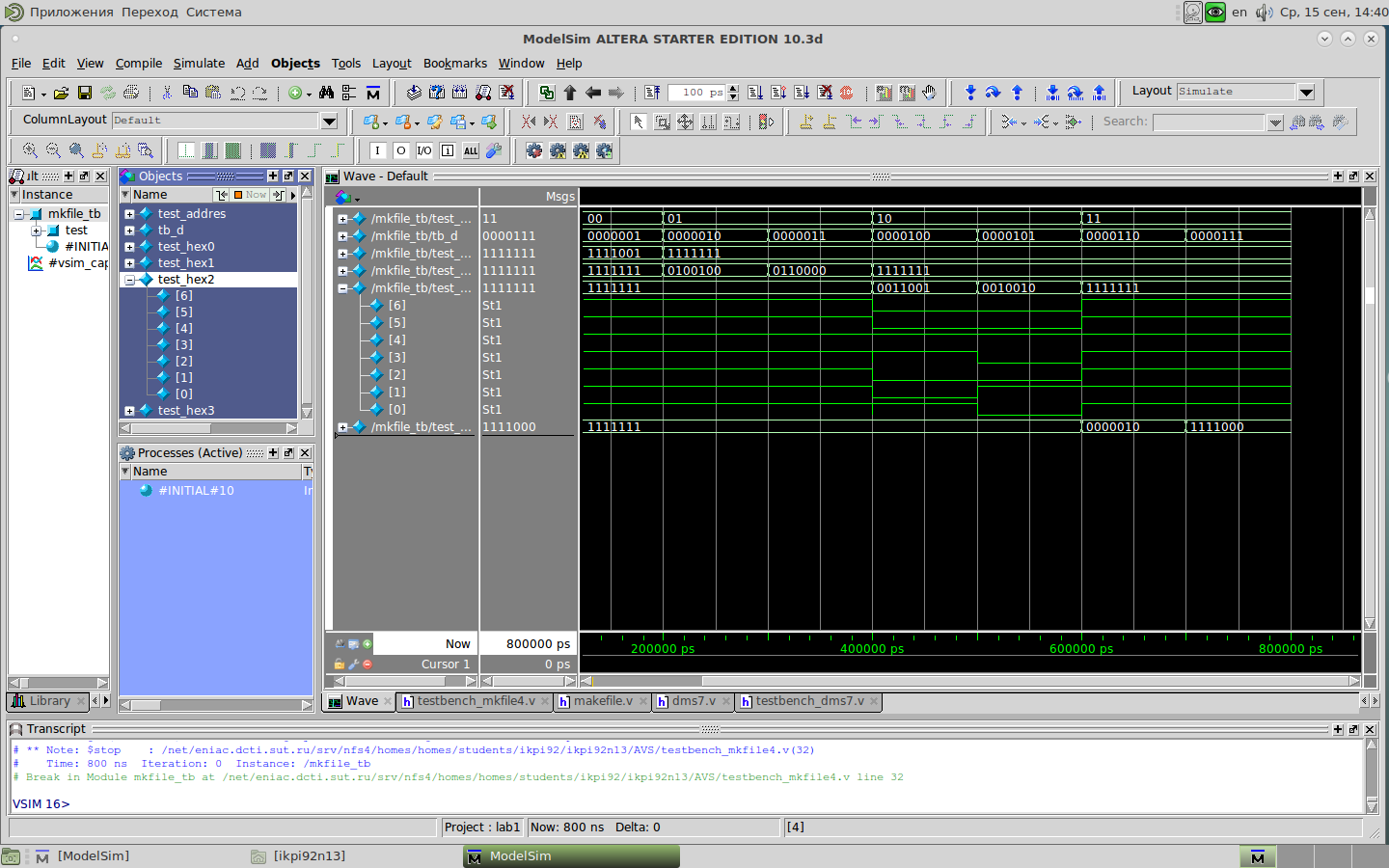

Результат работы в ModelSim

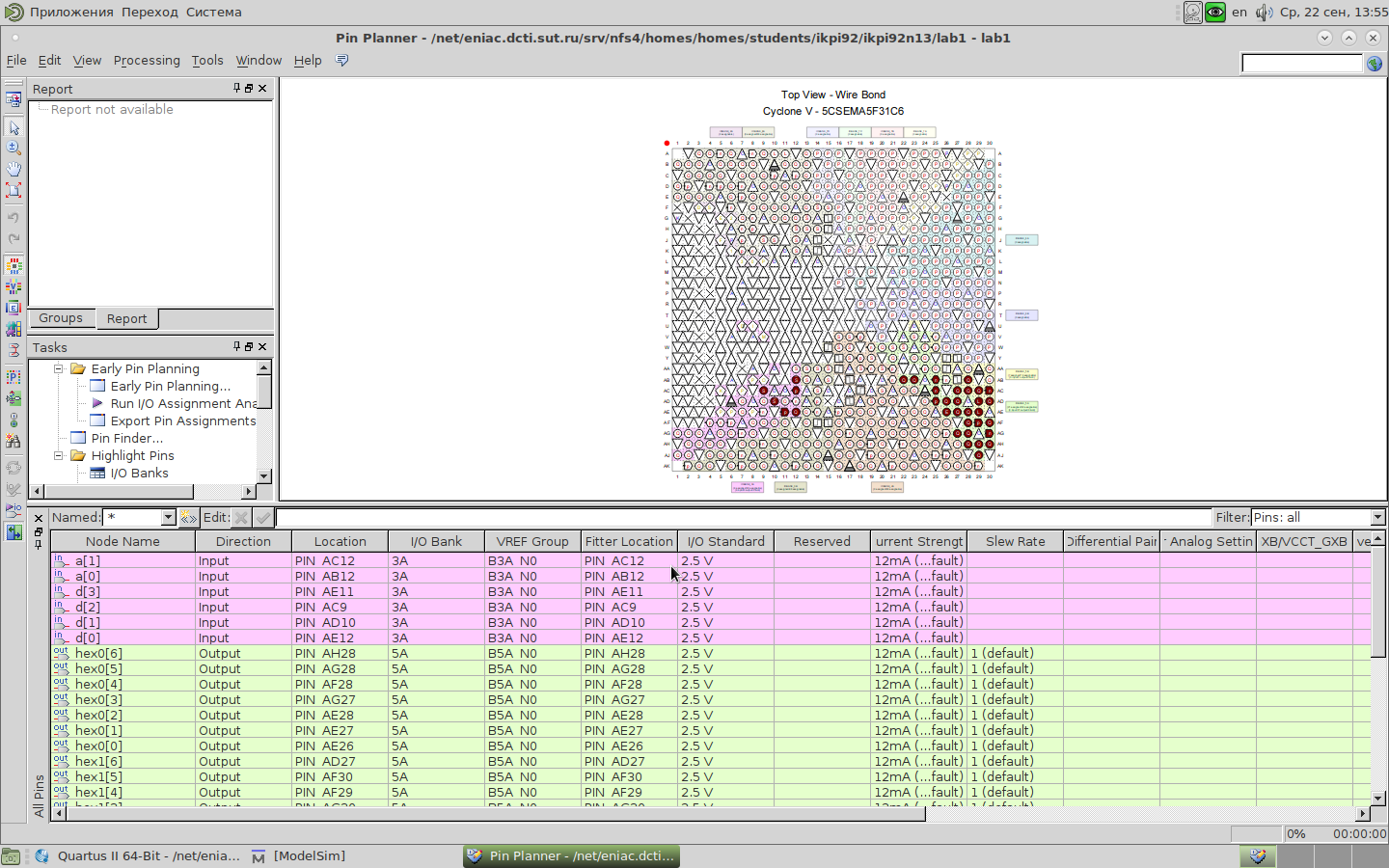

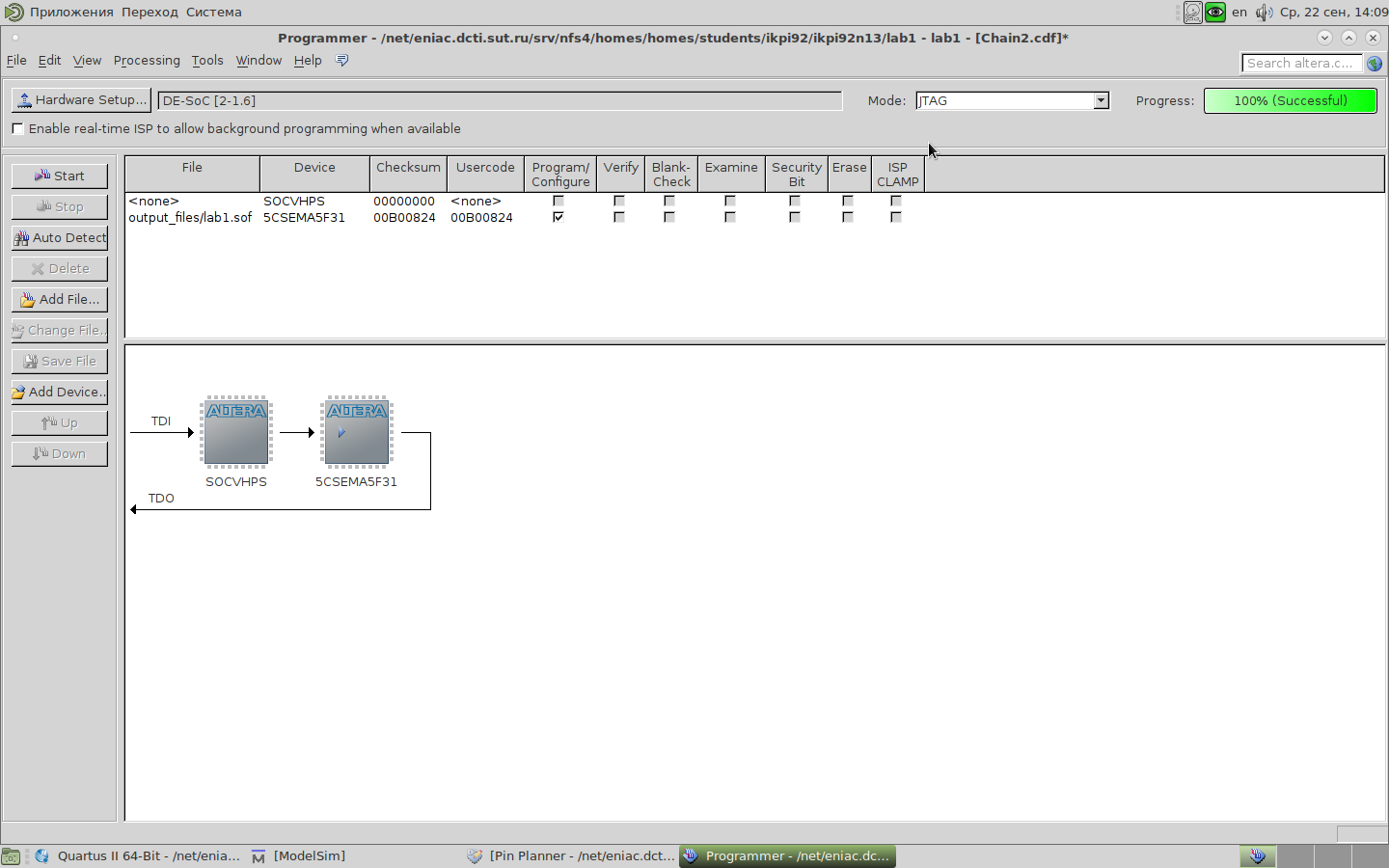

Модель в Quartus 15