- •Цель работы

- •Постановка задачи

- •1.Шифратор 4-2

- •1.1 Таблица истинности

- •2.1 Таблица истинности

- •2.2 Формула

- •2.3 Функциональная схема

- •2.4 Моделирование функциональной схемы

- •2.6 Схема из rtl Viewer для кода hdl

- •2.7 Моделирование устройства, описанного кодом hdl.

- •2.8 Таблица истинности масштабируемого устройства

- •3.1 Таблица истинности

- •3.2 Формула

- •3.3 Функциональная схема

- •3.4 Моделирование функциональной схемы

- •3.6 Схема из rtl Viewer для кода hdl

- •3.7 Моделирование устройства, описанного кодом hdl

2.7 Моделирование устройства, описанного кодом hdl.

На рисунке 2.7 представлен результат временного моделирования дешифратора 3-8, описанного на SystemVerilog.

Рисунок 2.7 – Результат временного моделирования дешифратора 3-8, описанного на SystemVerilog

Результаты совпадают с таблицей истинности, что говорит о том, что все выполнено также верно.

2.8 Таблица истинности масштабируемого устройства

Таблица истинности масштабируемого устройства представлена в таблице 2.8.

Таблица 2.8 – Масштабируемое устройство

DC 4x16 |

||||||||||||||||||||

Входы |

Выходы |

|||||||||||||||||||

E |

x3 |

x2 |

x1 |

x0 |

y15 |

y14 |

y13 |

y12 |

y11 |

y10 |

y9 |

y8 |

y7 |

y6 |

y5 |

y4 |

y3 |

y2 |

y1 |

y0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

x |

x |

x |

x |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

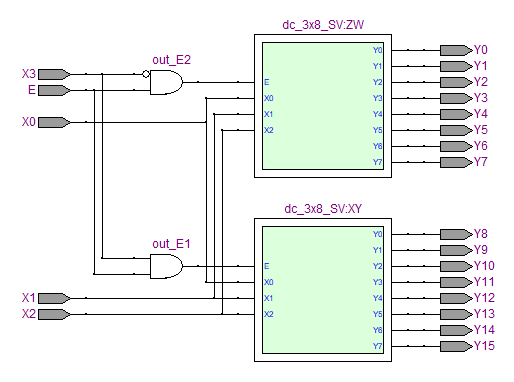

2.9 Функциональная схема масштабируемого устройства

Функциональная схема масштабируемого устройства приведена на рисунке 2.9.

Рисунок 2.9 – Функциональная схема масштабируемого устройства

2.10 Моделирование масштабируемого устройства

На рисунке 2.10 представлен результат временного моделирования дешифратора 4-16.

Рисунок 2.10 – Результат временного моделирования дешифратора 4-16

Результаты совпадают с таблицей истинности, что говорит о том, что все выполнено также верно.

2.11 Код на HDL масштабируемого устройств

На рисунке 2.11 представлен код описания дешифратора 4-16 на SystemVerilog.

Рисунок 2.11 – Код описания дешифратора 4-16 на SystemVerilog

2.12 Схема из RTL Viewer для кода HDL масштабируемого устройства

На рисунке 2.12 представлена схема из RTL Viewer для кода, написанном на SystemVerilog, дешифратора 4-16.

Рисунок 2.12 – Схема из RTL Viewer для кода дешифратора 4-16

2.13 Моделирование масштабируемого устройства, описанного кодом HDL

На рисунке 2.13 представлен результат временного моделирования дешифратора 4-16, описанного на SystemVerilog.

Рисунок 2.7 – Результат временного моделирования дешифратора 4-16, описанного на SystemVerilog

Результаты совпадают с таблицей истинности, что говорит о том, что все выполнено также верно.

3 Приоритетный шифратор 10-4