4 Семестр / Доп лаба 4 / ЭИС2 доп4лаб

.pdf

Продолжение таблицы 2.1

26 |

0 |

1 |

1 |

0 |

1 |

0 |

26 |

27 |

0 |

1 |

1 |

0 |

1 |

1 |

27 |

28 |

0 |

1 |

1 |

1 |

0 |

0 |

28 |

29 |

0 |

1 |

1 |

1 |

0 |

1 |

29 |

30 |

0 |

1 |

1 |

1 |

1 |

0 |

30 |

31 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

32 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

33 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

34 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

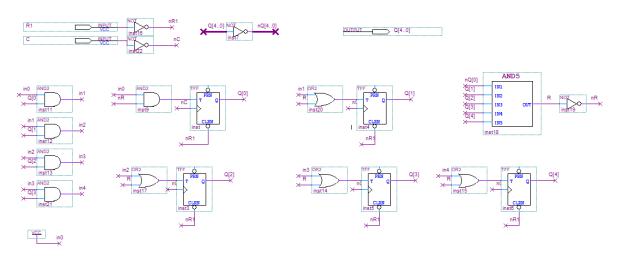

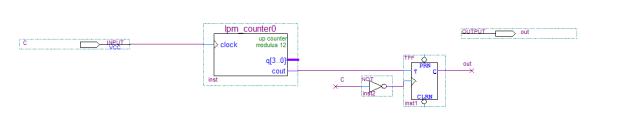

2.2 Функциональная схема

Функциональная схема согласно варианту №9, а именно для синхронного суммирующего счетчика с асинхронным сбросом, с модулем счета 31, управляемого передним фронтом, представлена на рисунке 2.1.

Рисунок 2.1 – Функциональная схема суммирующего счетчика

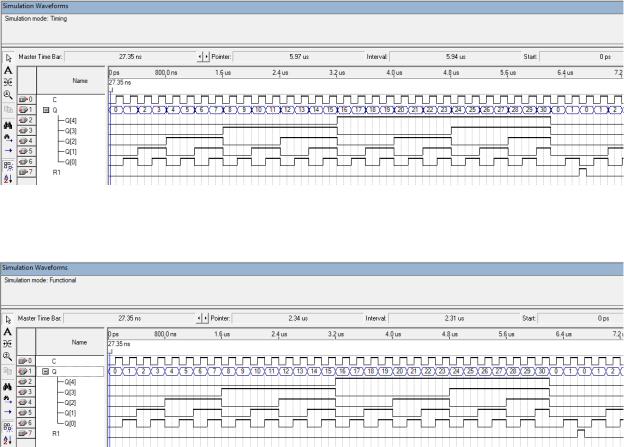

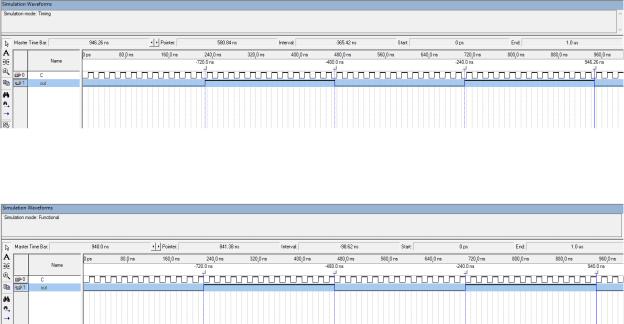

2.3 Моделирование функциональной схемы

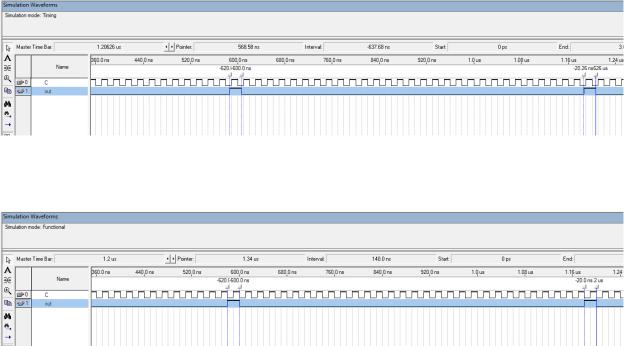

Далее было проведено моделирование построенной схемы в режимах «Timing» и «Functional», представленное на рисунках 2.2 – 2.3 соответственно.

11

Рисунок 2.2 – Моделирование функциональной схемы в режиме «Timing»

Рисунок 2.3 – Моделирование функциональной схемы в режиме «Functional»

Так как моделирование в режиме «Timing» приближено к реальности и отображает задержки переключения, результат немного искажается от идеального в режиме «Functional».

Значения моделирования совпали со значениями из таблицы истинности.

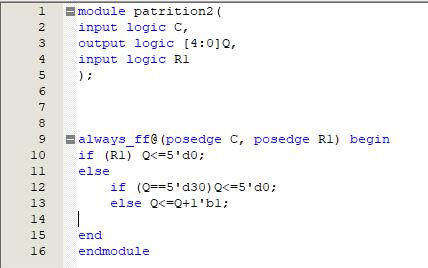

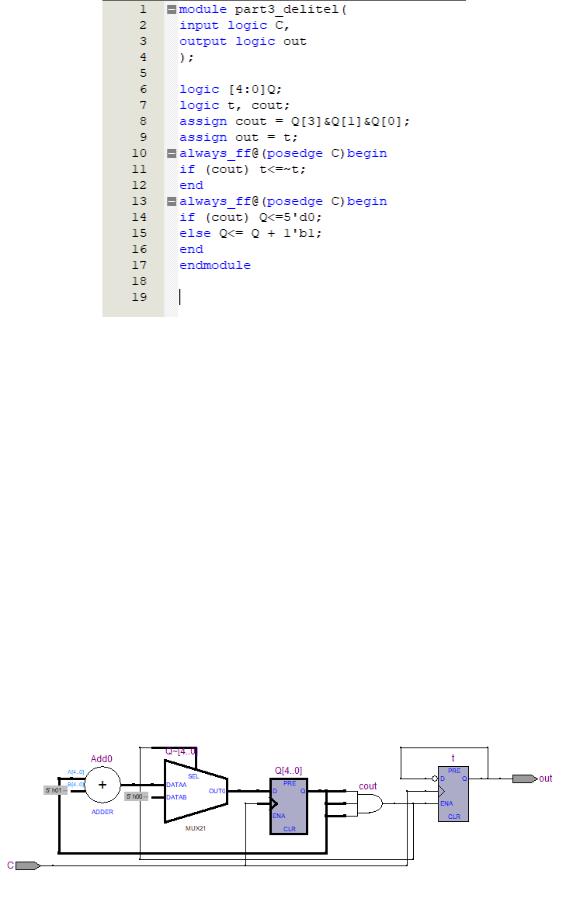

2.4 Описание функциональной схемы на HDL

Далее был составлен код описания схемы на HDL согласно варианту №9, а именно на языке описания аппаратуры System Verilog, представленный на рисунке 2.4.

12

Рисунок 2.4 – Описание функциональной схемы на языке описания аппаратуры System Verilog

Входы и выходы описаны в строчках 2 – 4. В строчках 9 – 15

описывается триггер, выполняющий функцию суммирующего счетчика с модулем счета 31 с проверкой на сигнал сброса.

2.5 Схема из RTL Viewer для кода HDL

Для составленного кода была сформирована схема при помощи RTL Viewer, представленная на рисунке 2.5.

13

Рисунок 2.5 – Сформированная схема при помощи RTL Viewer

2.6 Моделирование устройства, описанного кодом HDL

Было произведено моделирование устройства, описанного при помощи

System Verilog в режиме «Timing», представленное на рисунке 2.6.

Рисунок 2.6 – Моделирование устройства, описанного при помощи System Verilog в режиме «Timing»

Результат совпал с предыдущим моделированием, а также с таблицей истинности.

14

3 ДЕЛИТЕЛЬ ЧАСТОТЫ

3.1 Расчеты для построения схемы

По условию период входного сигнала Tвх = 20 нс. Согласно варианту №9 частота на выходе Fвых = 208333 Гц. Период единицы и нуля на выходе Tвых

рассчитывается по формуле 3.1. Модуль счета M рассчитывается по формуле 3.2. Длительность нуля T0 и длительность единицы T1 рассчитываются по формуле 3.3.

Tвых = |

1 |

, |

(3.1) |

|

Fвых |

||||

|

|

|

где Fвых – частота сигнала на выходе.

|

M = |

Tвых |

, |

|

(3.2) |

|

|

|

|

||||

|

|

Tвх |

|

|||

где Tвх – период входного сигнала. |

|

|||||

T0 |

= T1 = |

Tвых |

. |

(3.3) |

||

|

||||||

|

2 |

|

|

|||

Из формул 3.1 – 3.3 получаем, что период единицы и нуля на выходе Tвых

= 480, модуль счета M = 24, длительность нуля T0 и длительность единицы T1= 240 нс.

3.2 Функциональная схема

Функциональная схема для делителя частоты, представлена на рисунке

3.1.

Рисунок 3.1 – Функциональная делителя частоты

15

3.3 Моделирование функциональной схемы

Далее было проведено моделирование построенной схемы в режимах «Timing» и «Functional», представленное на рисунках 3.2 – 3.3 соответственно.

Рисунок 3.2 – Моделирование функциональной схемы в режиме «Timing»

Рисунок 3.3 – Моделирование функциональной схемы в режиме «Functional»

Так как моделирование в режиме «Timing» приближено к реальности и отображает задержки переключения, результат немного искажается от идеального в режиме «Functional».

Значения моделирования совпали с расчётами.

3.4 Описание функциональной схемы на HDL

Далее был составлен код описания схемы на HDL согласно варианту №9, а именно на языке описания аппаратуры System Verilog, представленный на рисунке 3.4.

16

Рисунок 3.4 – Описание функциональной схемы на языке описания аппаратуры System Verilog

Входы и выходы описаны в строчках 2 – 3. В строчках 6 – 7 описываются используемые сигналы. В строчке 8 описывается рассчитанный модуль счета.

В строчках 10 - 16 описывается триггер, выполняющий функцию делителя частоты.

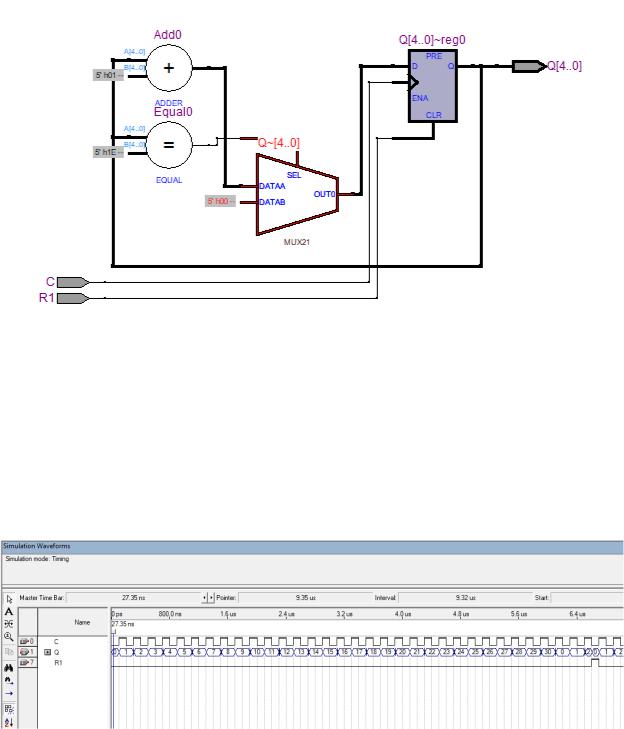

3.5 Схема из RTL Viewer для кода HDL

Для составленного кода была сформирована схема при помощи RTL Viewer, представленная на рисунке 3.5.

Рисунок 3.5 – Сформированная схема при помощи RTL Viewer 17

3.6 Моделирование устройства, описанного кодом HDL

Было произведено моделирование устройства, описанного при помощи

System Verilog в режиме «Timing», представленное на рисунке 3.6.

Рисунок 3.6 – Моделирование устройства, описанного при помощи System Verilog в режиме «Timing»

Результат совпал с предыдущим моделированием, а также с расчётами.

18

4 ФОРМИРОВАНИЕ ЗАДЕРЖКИ

4.1 Расчеты для построения схемы

По условию частота синхросигнала F = 50 МГц. Согласно варианту №9 длительность времени между импульсами Fвх = 58 мкс. Период входного сигнала Tвх рассчитывается по формуле 4.1. Модуль счета M рассчитывается по формуле 4.2.

Tвх = |

1 |

, |

|

(4.1) |

||

Fвх |

||||||

|

|

|

|

|

||

где Fвх – частота синхросигнала. |

|

|

|

|

||

M = |

Tзад+Tвх |

. |

(4.2) |

|||

|

||||||

|

|

Tвх |

|

|

|

|

Из формул 4.1 – 4.2 получаем, что период входного сигнала Tвх = 20 нс,

а модуль счета M = 30.

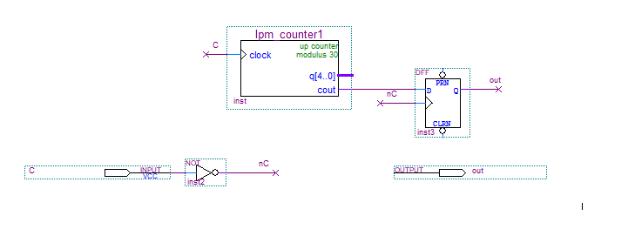

4.2 Функциональная схема

Функциональная схема для делителя частоты, представлена на рисунке

4.1.

Рисунок 4.1 – Функциональная схема для формирования задержки

19

4.3 Моделирование функциональной схемы

Далее было проведено моделирование построенной схемы в режимах «Timing» и «Functional», представленное на рисунках 4.2 – 4.3 соответственно.

Рисунок 4.2 – Моделирование функциональной схемы в режиме «Timing»

Рисунок 4.3 – Моделирование функциональной схемы в режиме «Functional»

Так как моделирование в режиме «Timing» приближено к реальности и отображает задержки переключения, результат немного искажается от идеального в режиме «Functional».

Значения моделирования совпали с расчётами.

4.4 Описание функциональной схемы на HDL

Далее был составлен код описания схемы на HDL согласно варианту №9, а именно на языке описания аппаратуры System Verilog, представленный на рисунке 4.4.

20