Лабы / Lb5_Arefyev_Sergeev_Zaytsev (1)

.pdf

МИНИСТЕРСТВО НАУКИ И ВЫСШЕГО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

Федеральноегосударственноеавтономноеобразовательноеучреждениевысшего образования

«НАЦИОНАЛЬНЫЙИССЛЕДОВАТЕЛЬСКИЙТОМСКИЙ ПОЛИТЕХНИЧЕСКИЙУНИВЕРСИТЕТ»

Школа: ИШЭ Направление: 13.03.02. Электроэнергетика и электротехника

«ИССЛЕДОВАНИЕ ТРИГГЕРОВ»

ЛАБОРАТОРНАЯ РАБОТА № 5

Вариант 4

по дисциплине:

ЭЛЕКТРОНИКА 2.1

Исполнитель: |

|

|

студент группы |

5А06 |

Арефьев А.В. |

|

|

Сергеев А.С. |

|

|

Зайцев С.А. |

Руководитель: |

|

|

К. т. н. |

|

Боловин Е.В. |

Томск - 2023

Цель работы: экспериментальное исследование работы триггеров,

выполненных на интегральных микросхемах, и закрепление знаний по последовательной цифровой логике.

Ход работы

1. RS-триггеры на элементах ИЛИ-НЕ

Рисунок 1 – RS-триггер на элементах ИЛИ-НЕ

Таблица 1. Состояния RS-триггера на элементах ИЛИ-НЕ

Режим |

S |

R |

Q |

|

|

|

|

Q |

|||||||

работы |

|||||||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

Запрещенное |

1 |

1 |

0 |

0 |

|

||

состояние |

|

||||||

|

|

|

|

|

|

||

|

|

|

|

|

|

||

Установка 1 |

1 |

0 |

1 |

0 |

|

||

|

|

|

|

|

|

||

Хранение |

0 |

0 |

1 |

0 |

|

||

|

|

|

|

|

|

||

Установка 0 |

0 |

1 |

0 |

1 |

|

||

|

|

|

|

|

|

||

Хранение |

0 |

0 |

0 |

1 |

|

||

|

|

|

|

|

|

|

|

Рисунок 2 - Временная диаграмма RS-триггера на элементах ИЛИ-НЕ

2. RS-триггеры на элементах И-НЕ

Рисунок 3 – RS-триггер на элементах И-НЕ

Таблица 2. Состояния RS-триггера на элементах И-НЕ

Режим |

|

̅ |

̅ |

Q |

|

|

|

|

Q |

||||||||

|

||||||||

работы |

|

|

|

|||||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

Запрещенное |

0 |

|

0 |

1 |

1 |

|

||

состояние |

|

|

||||||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

||

Установка 1 |

0 |

|

1 |

1 |

0 |

|

||

|

|

|

|

|

|

|

||

Хранение |

1 |

|

1 |

1 |

0 |

|

||

|

|

|

|

|

|

|

||

Установка 0 |

1 |

|

0 |

0 |

1 |

|

||

|

|

|

|

|

|

|

||

Хранение |

1 |

|

1 |

0 |

1 |

|

||

|

|

|

|

|

|

|

|

|

Рисунок 4 – Временная диаграмма RS-триггера на элементах И-НЕ

3. JK-триггеры

Рисунок 5 – Структурная схема JK-триггера

Таблица 3. Состояния JK-триггера

JK-триггер

|

|

|

|

|

|

J |

K |

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

0 |

0 |

0 |

|

|

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

1 |

0 |

0 |

|

|

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

1 |

0 |

1 |

|

|

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

1 |

1 |

0 |

|

|

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

1 |

1 |

1 |

|

|

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

0 |

0 |

0 |

|

|

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

0 |

0 |

1 |

|

|

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

0 |

1 |

0 |

|

|

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

0 |

1 |

1 |

|

|

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

1 |

0 |

0 |

|

|

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

0 |

|

|

|

|

1 |

1 |

1 |

0 |

|

|

|

|

1 |

1 |

0 |

0 |

|

|

|

|

1 |

1 |

0 |

1 |

|

|

|

|

1 |

1 |

0 |

1 |

|

|

|

|

1 |

1 |

0 |

0 |

|

|

|

|

1 |

1 |

1 |

1 |

|

|

|

|

1 |

1 |

1 |

1 |

|

|

|

|

1 |

1 |

1 |

1 |

|

|

|

|

1 |

1 |

1 |

1 |

|

|

|

|

1 |

0 |

|

|

1 |

0 |

|

|

1 |

0 |

|

|

0 |

1 |

|

|

0 |

1 |

|

|

0 |

1 |

|

|

1 |

0 |

|

|

0 |

1 |

|

|

1 |

0 |

|

|

0 |

1 |

|

|

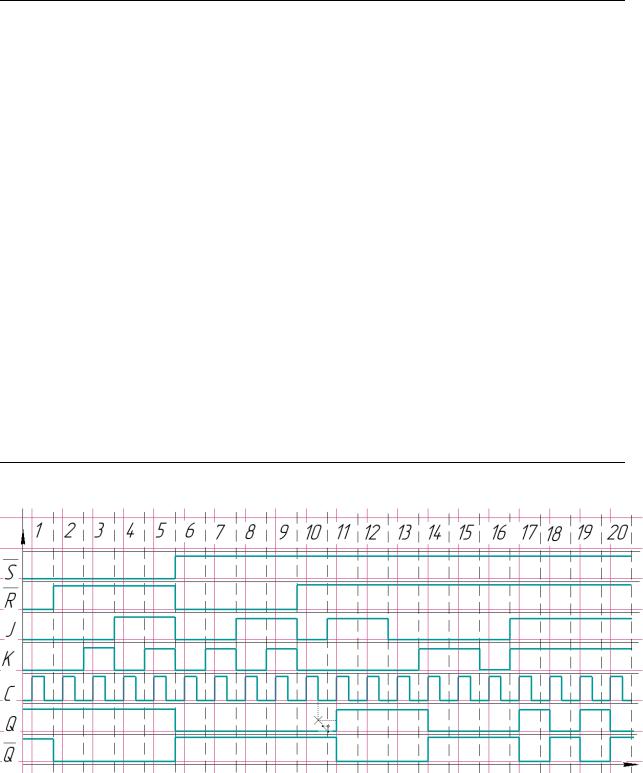

Рисунок 6 – Временная диаграмма JK-триггера

4. D-триггеры

Рисунок 7 – D-триггер на элементах И-НЕ

Таблица 4. Состояния D-триггера

D-триггер

|

|

|

|

|

|

D |

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

0 |

0 |

|

|

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

1 |

1 |

|

|

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

1 |

0 |

|

|

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

0 |

1 |

|

|

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

0 |

0 |

|

|

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

1 |

1 |

|

|

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

1 |

1 |

|

|

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

1 |

0 |

|

|

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

1 |

0 |

|

|

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

|

1 |

0 |

|

|

|

|

|

|

1 |

1 |

0 |

|

0 |

1 |

|

|

|

|

|

|

1 |

1 |

1 |

|

1 |

0 |

|

|

|

|

|

|

1 |

1 |

0 |

|

0 |

1 |

|

|

|

|

|

|

Рисунок 8 – Временная диаграмма D-триггера

Рисунок 9 – Схема Т-триггера

Таблица 5. Состояния Т-триггера

T-триггер

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|||

|

0 |

|

0 |

|

1 |

|

1 |

|||

|

|

|

|

|

|

|

|

|||

|

0 |

|

1 |

|

1 |

|

0 |

|||

|

|

|

|

|

|

|

|

|||

|

0 |

|

1 |

|

1 |

|

0 |

|||

|

|

|

|

|

|

|

|

|||

|

1 |

|

0 |

|

0 |

|

1 |

|||

|

|

|

|

|

|

|

|

|||

|

1 |

|

0 |

|

0 |

|

1 |

|||

|

|

|

|

|

|

|

|

|||

|

1 |

|

1 |

|

1 |

|

0 |

|||

|

|

|

|

|

|

|

|

|||

|

1 |

|

1 |

|

0 |

|

1 |

|||

|

|

|

|

|

|

|

|

|||

|

1 |

|

1 |

|

1 |

|

0 |

|||

|

|

|

|

|

|

|

|

|||

|

1 |

|

1 |

|

0 |

|

1 |

|||

|

|

|

|

|

|

|

|

|

|

|

Рисунок 10 – Временная диаграмма Т-триггера

Вывод:

В ходе выполнения лабораторной работы были исследованы триггеры,

выполненные на интегральных микросхемах, закреплены знания по последовательной цифровой логике.

Экспериментальные данные совпадают с теоретическими.

Следует заметить, что состояние JK-триггера зависит не только от сигналов на входах J и K, но и от логически связанных с ними сигналов с выходов Q и Q ̅Наличие цепей обратной связи наряду с информационными входами J и K присуще всем JK-триггерам.

Как следует из графического изображения триггера и временных диаграмм его работы, входы S и R с активным низким уровнем. Когда на один из этих входов подан сигнал низкого уровня информация со входов C, J и K

восприниматься не будет, т. е. входы S и R имеют приоритет над остальными входами. Информация со входов J и K записывается в триггер в два приема фронтом и срезом положительного тактового импульса по входу С. Входы S и R являют приоритетными. Нулевой сигнал на входе S устанавливает выход Q

в единичное состояние в независимости от уровней сигналов на J, K и С входах. При S=R=1 разрешается синхронное управление по J и K – входам.

Вход J устанавливает на выходе Q сигнал, равный 1, а вход К равный нулю.