ЛБ3_АСВТ

.docxМИНОБРНАУКИ РОССИИ

Федеральное государственное образовательное учреждение высшего образования

“Юго–Западный государственный университет”

Кафедра информационной безопасности

Лабораторная работа №3

По дисциплине “Аппаратные средства вычислительной техники”

По теме “ДВОИЧНЫЕ ТРИГГЕРЫ”

Выполнил: студент группы ИБ-11б

Гребенникова А.И.

Проверил Шевелев С.С.

Курск 2023г.

Цель работы: освоение основных этапов изучение и функционирование схемных разновидностей двоичных триггеров, анализа простейших цифровых схем с применением двоичных триггеров, синтеза цифровых автоматов в указанных базисах, комбинационных схем типовых узлов вычислительной техники с использованием механизма имитационного моделирования программы Multisim.

Теоретическая часть.

Триггер представляет собой устройство с двумя устойчивыми состояниями (рис. 2.1), одно из которых называют единичным (Q=1, Q =0), а другое - нулевым (Q=0, Q =1). Классификация триггеров может быть произведена по принципам логического функционирования и способу восприятия управляющей информации с информационных входов.

По способу синхронизации или по виду активных частей синхросигнала, во время которых происходит воздействие входных информационных сигналов и изменение его состояния, различают:

триггеры, управляемые (тактируемые) импульсом синхронизации. В свою очередь они подразделяется на одноступенчатые и двухступенчатые типа MS;

триггеры, управляемые фронтами (положительными или отрицательными), или триггеры с динамическим управлением записью информации, когда восприятие входных сигналов и переключение в новое состояние происходит во время фронта (среза) синхросигнала.

По виду логического функционирования различают триггеры типов RS, D, T, JK и др.

Все асинхронные триггеры можно отнести к разряду примитивных триггерных устройств, так как они являются прозрачными для входных информационных сигналов в любой момент времени и, следовательно, в максимальной степени подвержены действию помех. Положение усугубляется тем фактом, что выходы асинхронных триггеров одновременно является его входами, что ухудшает их помехозащищенность. Кроме того, существуют огрехи и в логическом функционировании. Так, например, D- триггер не имеет режима хранения, а в Т- и JKтриггерах практически невозможно реализовать счетный режим. Из всех типов асинхронных триггеров на практике нашел применение RS- триггер. Причем не столько в качестве автономной триггерной схемы, а как обязательная составная часть всех синхронных триггеров.

При описании работы триггерных схем (здесь и далее) принято дополнять обозначения входных сигналов и состояний триггера Q указанием времени t, при этом значение времени t+1 относится к новому состоянию триггера после его переключения. Таким образом, временные отметки t и t+1 как бы соответствуют отсчётам дискретного времени с интервалом, определенным переходом триггера в другое состояние.

RS-триггер. Основным назначением RS-триггеров является запись и хранение полученной информации. RS-триггер может легко оперировать данными и использовать их для периодического изменения общего состояния принципиальной схемы. Например, элемент может использоваться для включения определенных функций в электронной схеме.

Простой RS-триггер использует особый принцип работы, основанный на получении входных сигналов, которые в зависимости от поставленной задачи изменяют состояние выходов устройства. При входе сигнала на основной блок, на выходах происходит скачкообразное изменение напряжения, вследствие чего осуществляется управление поставленной задачей.

Синхронные триггеры относятся к сложным логическим устройствам. Синхронные RS-элементы отличаются от своих простых аналогов наличием синхронизирующего входного контакта «С», необходимого для улучшения логической работы.

Синхронный RS-триггер намного сложнее, так как схема принимает сигнал на контакт «С» в виде высокого напряжения. Сигнал синхронизируется, считывается входами «R»/«S» и только после этого создается переключение к выходам «Q». Принципиальная схема с входом «С» синхронного RS-триггера может дополняться обозначением «Clock», что означает «такт». Иными словами, синхронный элемент — это тактируемый точный RS триггер.

Асинхронный RS-элемент можно отнести к самым простым логическим устройствам. Их главное отличие заключается в отсутствии сигнала синхронизации. Как работает асинхронный RS-триггер, можно понять по его схеме. Принцип работы следующий:

Сигнал поступает к входу «S» (установить), устанавливается на нем и передается к выходу «Q». При этом на входе и выходе установлено высокое напряжение.

В этот момент на выходе «Q¯» устанавливается логически низкое напряжение в виде 0.

На момент установки сигнала схема будет находиться во включенном состоянии, например, будет запущен электродвигатель.

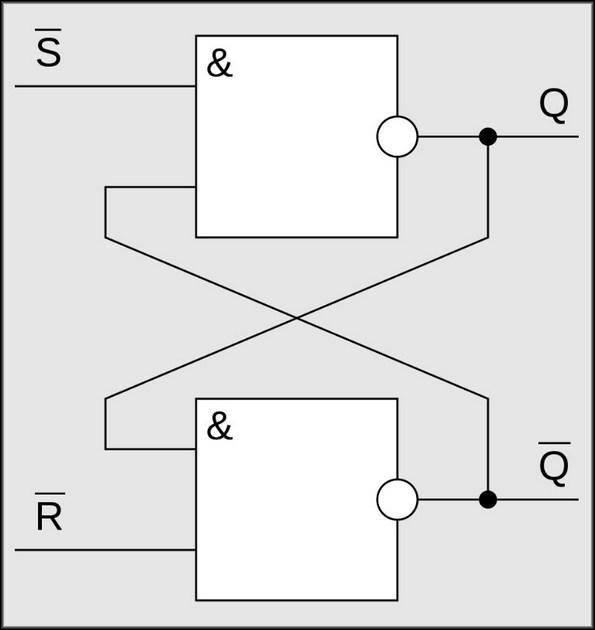

Рисунок 1 - Асинхронный RS-триггер

В схеме RS-триггера на логических элементах «И-НЕ» осуществляется работа за счет перехода 1 с входа к выходу (R 1 прямой на Q) или наоборот (S 0 инверсный к Q¯). Весь принцип управления этой цепи осуществляется за счет положительного входа и высокого напряжения.

Рисунок 2 - Схема RS-триггера на логических элементах И-НЕ

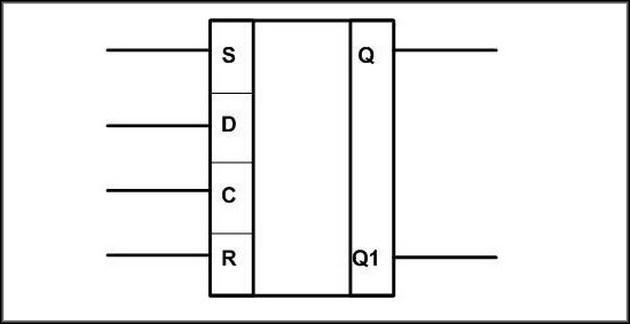

D-триггер. Синхронные и асинхронные элементы относятся к типу статических устройств. D-триггер — это динамическое устройство. Динамический элемент более простой. Отличается от ранее описанных отсутствием входных контактов «S» и «R». Вместо них присутствует вход «D».

Принцип работы зависит от фронта сигнала. Фронт осуществляет переход от логического числа 1 к числу 0 и наоборот. Переход 0-1 называется передним, 1-0 задним фронтом. Динамические триггеры часто оснащаются дополнительным входом «V» (подтверждение). Он необходим для задерживания сигнала, поступающего на D вход. Может быть реализован в качестве таймера. Для более стабильной работы D-триггера, часто устанавливается первичное устройство с входом «V», которое помогает сгладить время возникшей метастабильности, а так же защищает цепь от возникновения ошибки при переходе.

Рисунок 3 - D-триггер

Динамические устройства используются в вычислительной технике и простой автоматике в качестве дополнения к синхронным триггерам (дополнительная ячейка).

JK-триггер. Это универсальный простой триггер. Этот элемент имеет рабочие входы «J» и «K». По принципу работы и построению схож с асинхронной моделью. Отличается только логической цепью работы. Логическая 1 на выходе поступает с входа «J». При этом логический 0 на выходе «K» осуществляется за счет появления на входе высокого напряжения, а значит логической 1. Иными словами, на обоих входных контактах может одновременно быть высокое напряжение в виде логической 1.

Рисунок 4 - JK-триггер

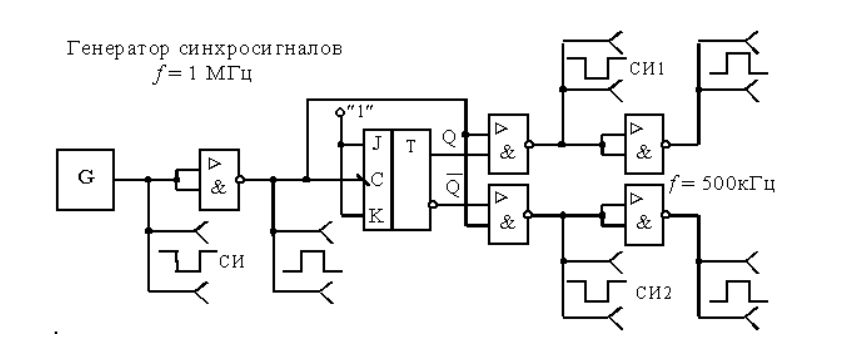

Работа цифровых устройств, содержащих двоичные элементы памяти на триггерах, сопровождается передачей данных по тракту их обработки от предшествующего блока к последующему. Такая передача данных строго регламентируется во времени синхросигналами, разрешающими прием и передачу данных для каждого блока. Простейшая схема двухфазной последовательности синхросигналов изображена на рис. 2.12. в которой распределение синхросигналов основной последовательности СИ (f = 1 МГц) осуществляется по двум фазам синхронизации СИ1 () и СИ2 (), Обратите внимание, что конъюнкция синхросигналов СИ1 и СИ2 в любой момент времени равна "0",- важный принцип двухфазной синхронизации.

Триггер — очень нужный элемент в схеме автоматического управления. Такие логические устройства способны управлять функциональностью сложного электронного оборудования. Обладая маленькой памятью, они могут контролировать рабочее состояние аппаратуры, моменты включения и выключения, перераспределять логические задачи в приборах, работающих с высокочастотными сигналами, применяться в составе цифровых фильтров.

Практическая часть.

Рисунок 5 - Схема №2.12 формирования двухфазной синхропоследовательности

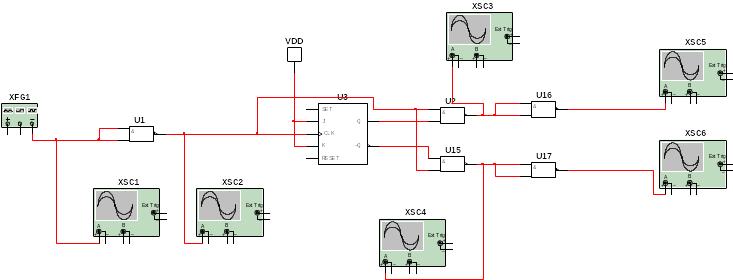

Рисунок 6 - Схема №2.12 формирования двухфазной синхропоследовательности в Multisim

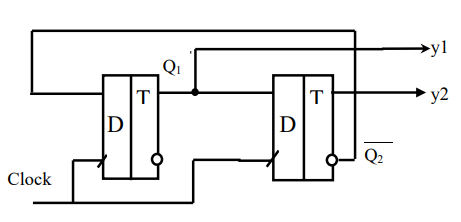

Рисунок 7 - Схема №2.13 формирования двух последовательностей импульсов со сдвигом на четверть периода относительно друг друга

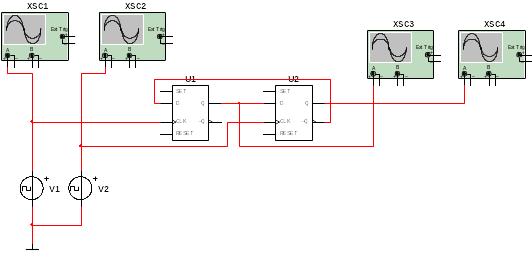

Рисунок 8 - Схема №2.13 формирования двух последовательностей импульсов со сдвигом на четверть периода относительно друг друга в Multisim

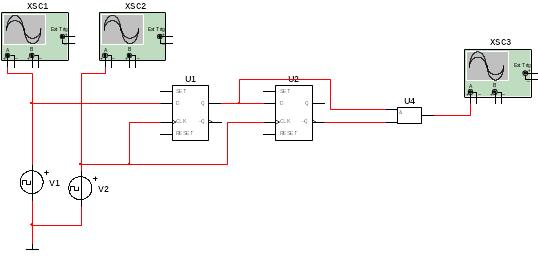

Рисунок 9 - Схема №2.14 формирования импульса, равного периоду синхросигнала.

Рисунок 10 - Схема №2.14 формирования импульса, равного периоду синхросигнала в Multisim

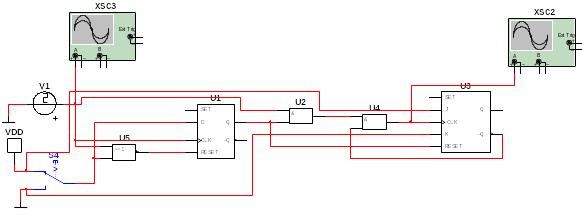

Рисунок 11 - Схема №2.15 формирователь одиночного синхроимпульса одновременно с пачкой синхросигналов.

Рисунок 12 - Схема №2.15 формирователь одиночного синхроимпульса одновременно с пачкой синхросигналов в Multisim