lab1_otchet

.docxВыполнили:

Отчёт по лабораторной работе №1.

ОСНОВЫ РАЗРАБОТКИ ПРОЕКТА В СРЕДЕ VIVADO

Цель работы

Изучение среды разработки цифровых устройств на ПЛИС Xilinx Vivado 2016.4. Написание модулей на языке Verilog и тестирующих окружений. Проверка работоспособности разработанного устройства на временной симуляции в XSim.

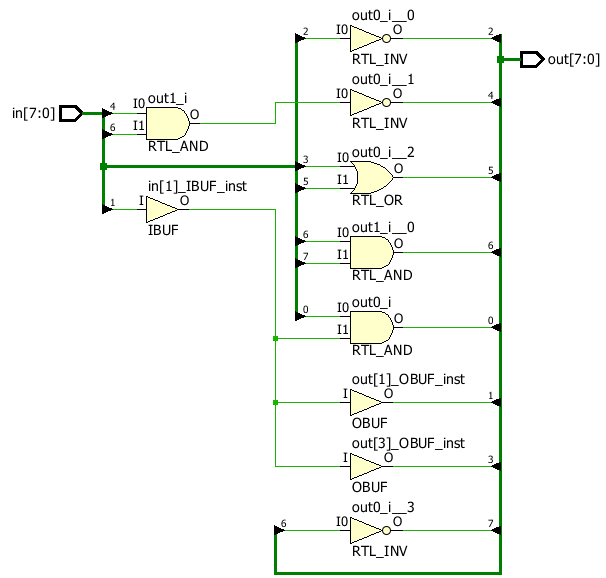

1. module < name_of_module > (

< объявление входов и выходов >

);

< оператор >;

< оператор >;

…

< оператор >;

endmodule

2. Объект wire нужен для объявления промежуточных переменных.

3. module sw_led(

input wire [7:0] in,

output wire [7:0] out

);

assign out[0] = in[0] & in[1];

assign out[1] = in[1];

assign out[2] = ~in[2];

assign out[3] = in[1];

assign out[4] = ~(in[4] & in[6]);

assign out[5] = in[3] | in[5];

assign out[6] = in[6] & in[7];

assign out[7] = ~(in[6] & in[7]);

endmodule

4. Ключевое слово assign - это оператор непрерывного назначения. Он предназначен для объявления переменных. Выполняется параллельно, независимо от места в коде.

5. `timescale 1ns / 1ps

module sw_led_tb_1(

);

reg [7:0] in_tb;

wire [7:0] out_tb;

integer i;

sw_led DUT(

.in (in_tb),

.out (out_tb)

);

initial

begin

for (i = 0; i < 256; i = i + 1)

begin

#10;

in_tb = i;

end

end

endmodule

6.

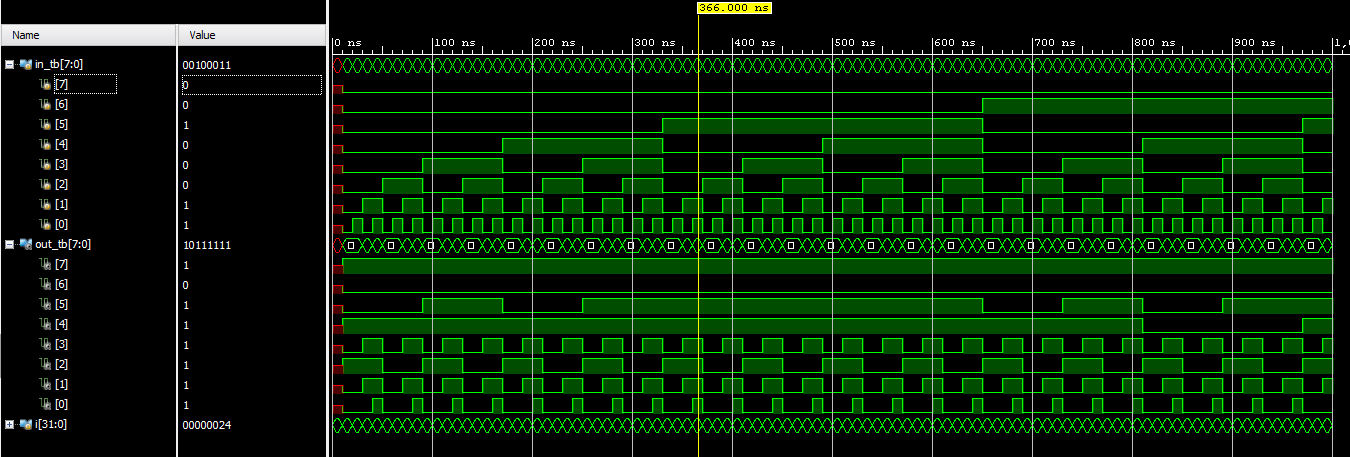

7. 7. Входные и выходные значения из диаграммы

|

in |

out |

in |

out |

in |

out |

in |

out |

in |

out |

||||

t, ns |

366.000 |

460.356 |

510.203 |

622.605 |

956.906 |

|||||||||

№ |

||||||||||||||

[7] |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

||||

[6] |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

||||

[5] |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

||||

[4] |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

||||

[3] |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

||||

[2] |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

||||

[1] |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

||||

[0] |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

||||

Вывод

Программа работает корректно. Все вычисления выполнены верно.