lab5_otchet

.docxВыполнили:

Лабораторная работа 6

РАЗРАБОТКА МОДУЛЯ ДЛЯ УПРАВЛЕНИЯ СЕМИСЕГМЕНТНЫМ ИНДИКАТОРОМ СПОМОЩЬЮ ПОВОРОТНОГО ЭНКОДЕРА

Цель работы

Управление семигементным индикатором с помощью поворотного энкодера. Написание тестового модуля. Проверка работоспособности на отладочной плате zedboard.

1. Принцип подключения семисегментного индикатора.

Индикатор подключается соответственно распиновке. Вольтаж выставляется в файле .xdc

2. Листинг модулей из индивидуального задания, c поясняющими комментариями каждой строки.

module top

(

input global_clk,

input enc_a, enc_b,

output [7:0] seven_segm_disp

);

reg [3:0] enc_byte = 0;

wire enc_a_rise;

wire enc_b_db;

always @(posedge global_clk)

begin

if (enc_a)

begin

if (!enc_b)

begin

enc_byte <= enc_byte - 1;

end

else

begin

enc_byte <= enc_byte + 1;

end

end

end

wire[7:0] connect;

assign connect = seven_segm_disp;

ssd_driver driver( .clk( global_clk ), .swt( enc_byte ), .ssd( seven_segm_disp ) );

debounce debounce_a( .switch_in( enc_a ), .switch_out( enc_a_rise ), .clk( global_clk ) );

debounce debounce_b( .switch_in( enc_b ), .switch_out( enc_b_db ), .clk( global_clk ) );

endmodule

module ssd

(

input clk,

input [3:0] swt,

output reg [7:0] ssd

);

always @(posedge clk)

begin

case ( swt[3:0] )

4'b0000: ssd <= 8'b11111110;

4'b0001: ssd <= 8'b10110000;

4'b0010: ssd <= 8'b11101101;

4'b0011: ssd <= 8'b11111001;

4'b0100: ssd <= 8'b10110011;

4'b0101: ssd <= 8'b11011011;

4'b0110: ssd <= 8'b11011111;

4'b0111: ssd <= 8'b11110000;

4'b1000: ssd <= 8'b11111111;

4'b1001: ssd <= 8'b11110011;

4'b1010: ssd <= 8'b11110111;

4'b1011: ssd <= 8'b10011111;

4'b1100: ssd <= 8'b11001110;

4'b1101: ssd <= 8'b10111101;

4'b1110: ssd <= 8'b11001111;

4'b1111: ssd <= 8'b11000111;

endcase

end

endmodule

module debounce #( parameter bounce_limit = 1024 )

(

input clk,

input switch_in,

output reg switch_out,

output reg switch_rise,

output reg switch_fall

);

reg [$clog2(bounce_limit)-1:0] bounce_count = 0;

reg [1:0] switch_shift;

always @(posedge clk)

switch_shift <= {switch_shift,switch_in};

always @(posedge clk)

begin

if (bounce_count == 0)

begin

switch_rise <= switch_shift == 2'b01;

switch_fall <= switch_shift == 2'b10;

switch_out <= switch_shift[0];

if (switch_shift[1] != switch_shift[0])

bounce_count <= bounce_limit-1;

end

else

begin

switch_rise <= 0;

switch_fall <= 0;

bounce_count <= bounce_count-1;

end

end

endmodule

3. Листинг тестового модуля.

`timescale 1ns / 1ps

module top_tb();

reg clk = 0;

reg [1:0] enc = 0;

wire [7:0] ssd_tb;

top encoder( .global_clk( clk ), .enc_a( enc[0] ), .enc_b( enc[1] ), .seven_segm_disp( ssd_tb ) );

integer i;

initial

begin

for( i = 0; i < 16; i = i + 1 )

#10 enc = enc + 1;

end

always #5 clk = ~clk;

endmodule

4. Содержимое xdc файла и комментарий каждой строки.

set_property PACKAGE_PIN AA9 [get_ports {seven_segm_disp[7]}]

set_property PACKAGE_PIN AA11 [get_ports {seven_segm_disp[6]}]

set_property PACKAGE_PIN Y11 [get_ports {seven_segm_disp[5]}]

set_property PACKAGE_PIN Y10 [get_ports {seven_segm_disp[4]}]

set_property PACKAGE_PIN W11 [get_ports {seven_segm_disp[3]}]

set_property PACKAGE_PIN W12 [get_ports {seven_segm_disp[2]}]

set_property PACKAGE_PIN V10 [get_ports {seven_segm_disp[1]}]

set_property PACKAGE_PIN W8 [get_ports {seven_segm_disp[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segm_disp[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segm_disp[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segm_disp[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segm_disp[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segm_disp[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segm_disp[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segm_disp[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seven_segm_disp[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports enc_a]

set_property IOSTANDARD LVCMOS33 [get_ports enc_b]

set_property IOSTANDARD LVCMOS33 [get_ports global_clk]

set_property PACKAGE_PIN Y9 [get_ports global_clk]

set_property PACKAGE_PIN AA4 [get_ports enc_a]

set_property PACKAGE_PIN Y4 [get_ports enc_b]

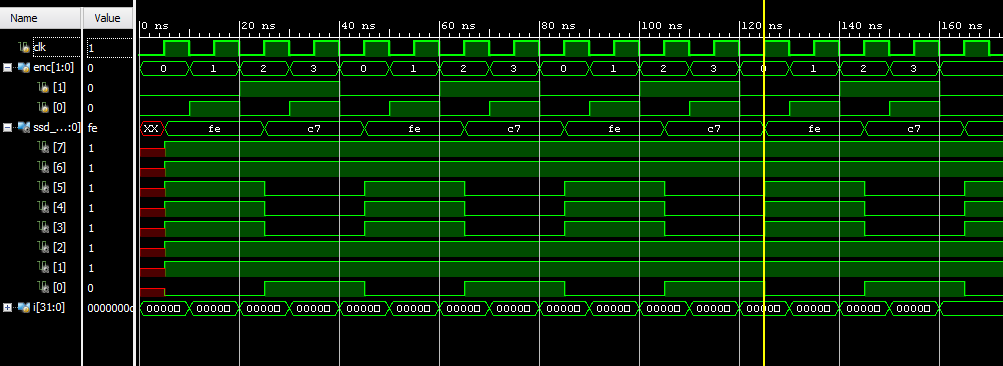

5. Временные диаграммы и сохраненные фрагменты экрана с графическим пояснением.

6. Выводы о правильности работы.

Работа программы корректна, все вычисления верны.