lab3_otchet

.docxВыполнили:

Лабораторная работа 3

РАЗРАБОТКА МОДУЛЯ ПАМЯТИ ROM

Цель работы

Разработка модуля для реализации блочной памяти средствами ПЛИС. Исследование возможности инициализации памяти. Проверка на временной диаграмме. Проверка на железе.

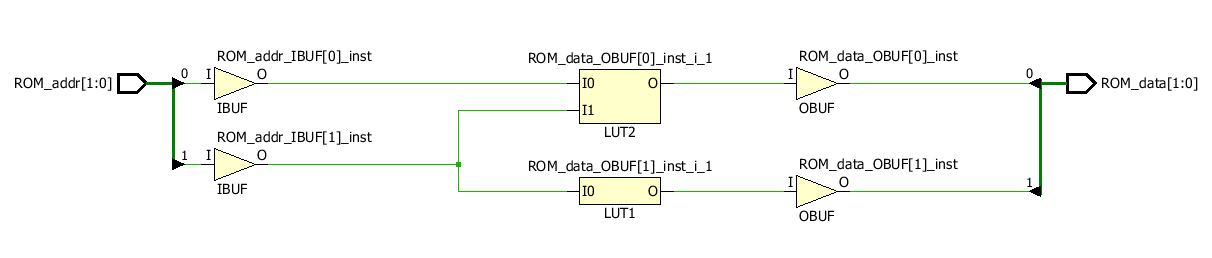

RTL

Matlab – скрипт

clc

clear all

x = [ 0 : 2*pi/256 : 2*pi-2*pi/256 ]; % задаём интервал по x с шагом 2*pi/256

y = sin( 9 * x ) + 1; % задаём ф-ию с периодом равным 9 на данном промежутке

y2 = y./max(y); % нормируем каждый отсчёт

y3 = ceil(y2.*(2^8-1)); % приводим отсчёты к целому виду

fid = fopen('C:\\Users\\User\\Desktop\\sin_val.dat', 'wb'); % открываем в файл

% для записи бинарного кода

if fid == -1 % проверяем на

% корректность открытия

error('File is not opened');

end

for i = 1:256 % цикл для записи

% каждого отсчёта

fprintf(fid, '%s\n', dec2bin(y3(i), 8));

end

Принцип работы ROM

Проект считывает из файла ( 256 строк по 8 бит ) и записывает в соответствующий массив.

Листинги файлов

`timescale 1ns / 1ps

module ROM_4x2 (

output [7:0] ROM_data,

input [7:0] ROM_addr

);

reg [7:0] ROM [255:0];

assign ROM_data = ROM[ROM_addr];

initial

begin

$readmemb ( "C:\\Users\\User\\Desktop\\sin_val.dat", ROM, 0, 255 );

end

endmodule

`timescale 1ns / 1ps

module ROM_4x2_tb();

reg [7:0] swt;

wire [7:0] led;

ROM_4x2 DUT

(

.ROM_addr (swt),

.ROM_data (led)

);

integer i;

initial

begin

for( i = 0; i < 256; i = i + 1 )

#10 swt = i;

end

endmodule

xdc файлы

set_property PACKAGE_PIN M15 [get_ports {ROM_addr[7]}]

set_property PACKAGE_PIN H17 [get_ports {ROM_addr[6]}]

set_property PACKAGE_PIN H18 [get_ports {ROM_addr[5]}]

set_property PACKAGE_PIN H19 [get_ports {ROM_addr[4]}]

set_property PACKAGE_PIN F21 [get_ports {ROM_addr[3]}]

set_property PACKAGE_PIN H22 [get_ports {ROM_addr[2]}]

set_property PACKAGE_PIN F22 [get_ports {ROM_addr[1]}]

set_property PACKAGE_PIN G22 [get_ports {ROM_addr[0]}]

set_property PACKAGE_PIN U14 [get_ports {ROM_data[7]}]

set_property PACKAGE_PIN U19 [get_ports {ROM_data[6]}]

set_property PACKAGE_PIN W22 [get_ports {ROM_data[5]}]

set_property PACKAGE_PIN V22 [get_ports {ROM_data[4]}]

set_property PACKAGE_PIN U21 [get_ports {ROM_data[3]}]

set_property PACKAGE_PIN U22 [get_ports {ROM_data[2]}]

set_property PACKAGE_PIN T21 [get_ports {ROM_data[1]}]

set_property PACKAGE_PIN T22 [get_ports {ROM_data[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {ROM_addr[7]}]

set_property IOSTANDARD LVCMOS18 [get_ports {ROM_addr[6]}]

set_property IOSTANDARD LVCMOS18 [get_ports {ROM_addr[5]}]

set_property IOSTANDARD LVCMOS18 [get_ports {ROM_addr[4]}]

set_property IOSTANDARD LVCMOS18 [get_ports {ROM_addr[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports {ROM_addr[2]}]

set_property IOSTANDARD LVCMOS18 [get_ports {ROM_addr[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {ROM_addr[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ROM_data[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ROM_data[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ROM_data[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ROM_data[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ROM_data[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ROM_data[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ROM_data[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ROM_data[0]}]

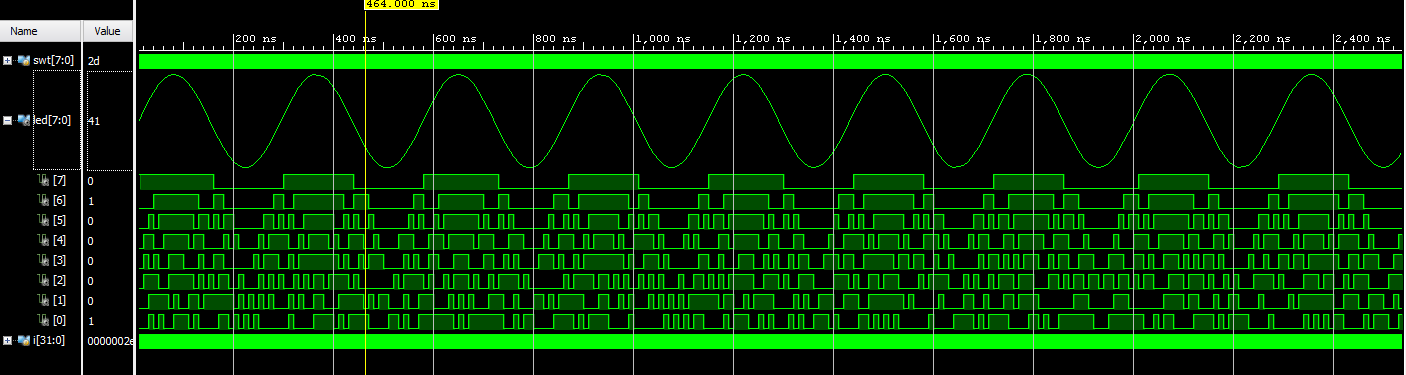

Временные диаграммы

Вывод

Работа программы корректна, все вычисления верны.