lab2_otchet

.docxВыполнили:

Лабораторная работа 2

РАЗРАБОТКА МОДУЛЯ ВЕРХНЕГО УРОВНЯ, ЗАПУСК ПРОЕКТА

НА ПЛАТЕ

Цель работы

Разработка модуля верхнего уровня. Изучения возможности соединения нескольких модулей в проекте. Анализ задержек. Проверка готового модуля на плате.

1. Соединение модулей происходит с помощью указания названия подмодуля в главном модуле и присвоения элементов главного модуля элементам подмодуля для дальнейшего выполнения алгоритма подмодуля.

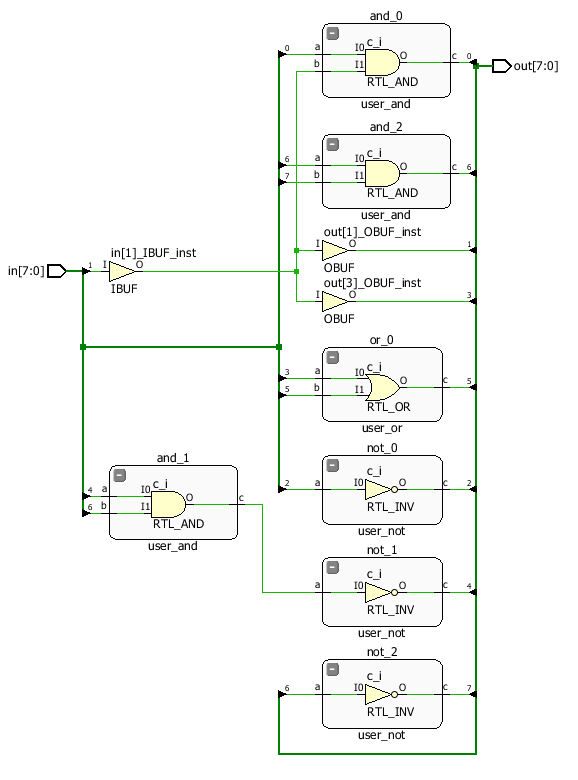

2. Блочная схема

3. Модули

module top( //модуль обозначения вх. и вых.

input [7:0] in,

output [7:0] out

);

user_and and_0( //этот и последующие модули user_and

.a( in[0] ), //нужны для произведения лог. операции

.b( in[1] ), //AND

.c( out[0] )

);

assign out[1] = in[1]; //выходу out[1] присваиваем значение

//входа через оператор непрерывного //назначения assign

user_not not_0( //этот и последующие модули user_not

.a( in[2] ), //нужны для произведения лог. операции

.c( out[2] ) //NOT

);

assign out[3] = in[1]; //присваиваем выходу значение входа

wire temp_1; //переменная temp нужна для

//промежуточных операций

user_and and_1(

.a( in[4] ),

.b( in[6] ),

.c( temp_1 )

);

user_not not_1(

.a( temp_1 ),

.c( out[4] )

);

user_or or_0( //этот и последующие модули user_or

.a( in[3] ), //нужны для произведения лог. операции

.b( in[5] ), //OR

.c( out[5] )

);

wire temp_2;

user_and and_2(

.a( in[6] ),

.b( in[7] ),

.c( temp_2 )

);

assign out[6] = temp_2;

user_not not_2(

.a( temp_2 ),

.c( out[7] )

);

endmodule

4. Листинг xdc файла:

set_property PACKAGE_PIN F22 [get_ports {in[0]}]

set_property PACKAGE_PIN G22 [get_ports {in[1]}]

set_property PACKAGE_PIN H22 [get_ports {in[2]}]

set_property PACKAGE_PIN F21 [get_ports {in[3]}]

set_property PACKAGE_PIN H19 [get_ports {in[4]}]

set_property PACKAGE_PIN H18 [get_ports {in[5]}]

set_property PACKAGE_PIN H17 [get_ports {in[6]}]

set_property PACKAGE_PIN M15 [get_ports {in[7]}]

set_property PACKAGE_PIN T22 [get_ports {out[0]}]

set_property PACKAGE_PIN T21 [get_ports {out[1]}]

set_property PACKAGE_PIN U22 [get_ports {out[2]}]

set_property PACKAGE_PIN U21 [get_ports {out[3]}]

set_property PACKAGE_PIN V22 [get_ports {out[4]}]

set_property PACKAGE_PIN W22 [get_ports {out[5]}]

set_property PACKAGE_PIN U19 [get_ports {out[6]}]

set_property PACKAGE_PIN U14 [get_ports {out[7]}]

Данный файл нужен для обозначения и хранения информации о пинах, присвоенных входам и выходам.

5. Testbench

`timescale 1ns / 1ps

module top_tb(

);

reg [7:0] in_tb;

wire [7:0] out_tb;

integer i;

top DUT(

.in (in_tb),

.out (out_tb)

);

initial

begin

for ( i = 0; i < 256; i = i + 1 )

begin

#10;

in_tb = i;

end

end

endmodule

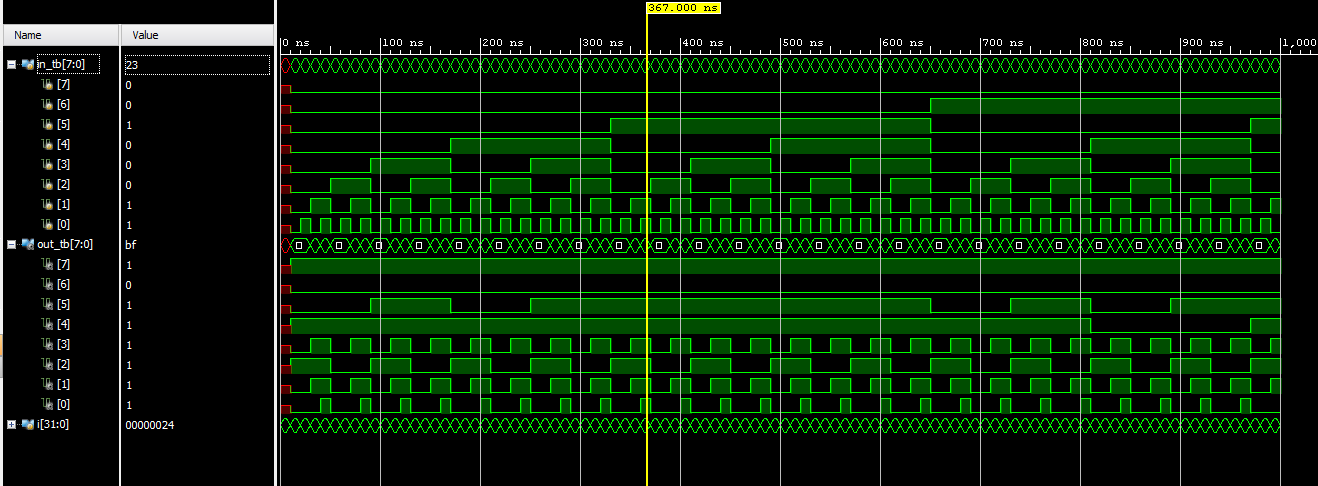

6. Скрин со 2 лабы

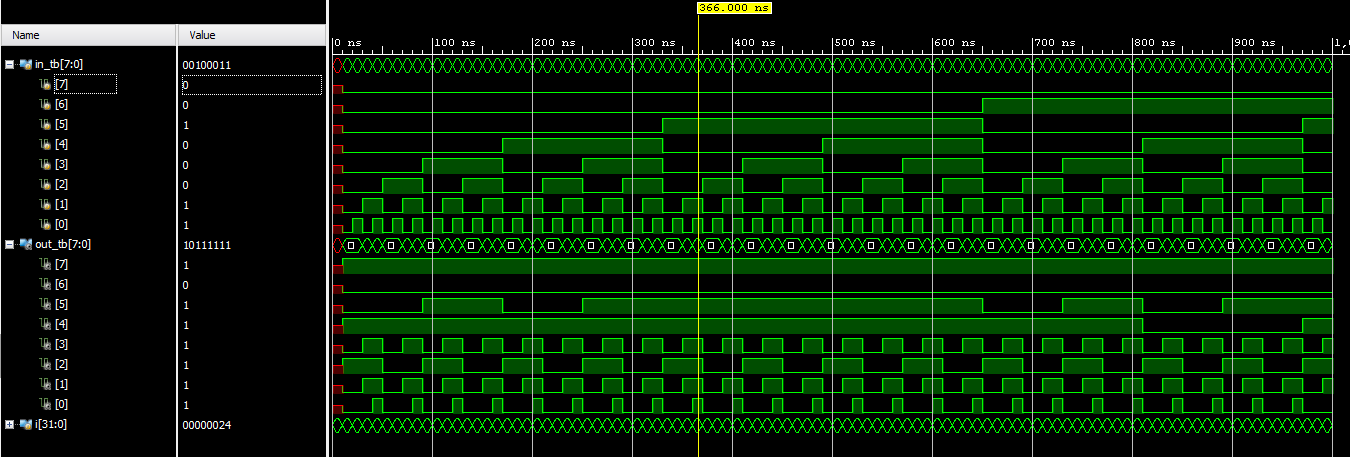

Скрин с 1 лабы

7. Входные и выходные значения из диаграммы

|

in |

out |

in |

out |

in |

out |

in |

out |

in |

out |

||||

t, ns |

367.000 |

460.230 |

510.000 |

623.860 |

955.860 |

|||||||||

№ |

||||||||||||||

[7] |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

||||

[6] |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

||||

[5] |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

||||

[4] |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

||||

[3] |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

||||

[2] |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

||||

[1] |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

||||

[0] |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

||||

Вывод

Работа программы корректна, все вычисления верны.