ЛБ2_АСВТ

.docxМИНОБРНАУКИ РОССИИ

Федеральное государственное образовательное учреждение высшего образования

“Юго–Западный государственный университет”

Кафедра информационной безопасности

Лабораторная работа №2

По дисциплине “Аппаратные средства вычислительной техники”

По теме “ Логические элементы и функции. Методы минимизации булевых функций. Синтез комбинационных схем”

Выполнил: студент группы ИБ-11б

Гребенникова А.И.

Проверил Шевелев С.С.

Курск 2023г.

Цель работы: освоение основных этапов синтеза функциональных блоков, типовых узлов, комбинационных схем вычислительной техники с использованием механизма имитационного моделирования программы.

Теоретическая часть

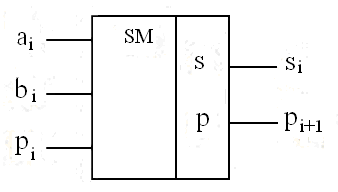

Сумматорами

называют логические устройства,

выполняющие арифметические суммирование

кодов двоичного числа. Символическое

изображение одноразрядного двоичного

сумматора показано на рис.10.29. Сумматор

имеет три входа, где ![]()

![]()

![]() -

слагаемые одинакового разряда,

-

слагаемые одинакового разряда, ![]() –

слагаемое переноса; на выходе формируется

–

слагаемое переноса; на выходе формируется ![]() –

сумма cлагаемых и

–

сумма cлагаемых и ![]() –

слагаемое переноса в старший разряд.

–

слагаемое переноса в старший разряд.

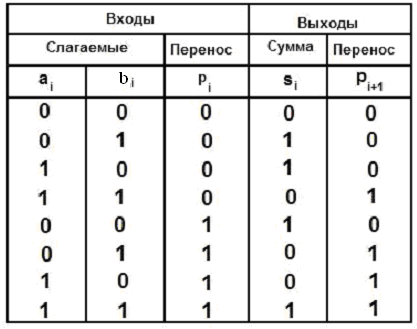

Функционирование

однозарядного сумматора показано в

таблице, приведённой на рис.10.30. В этом

случае при сложении слагаемых ![]() используется

перевод десятичных чисел в двоичные

числа.

используется

перевод десятичных чисел в двоичные

числа.

Pиc.10.29. Символическое изображение одноразрядного двоичного сумматора

Рассмотрим пример:

При

сложении слагаемых 0+1+0 получается

десятичное число 1.

Такому числу соответствует двоичное

число 01,

при этом ![]() Аналогично, 1+1+0

= 2,

которому соответствует двоичное

число 10, при

этом

Аналогично, 1+1+0

= 2,

которому соответствует двоичное

число 10, при

этом ![]() . При

сложении чисел 1+1+1 =

3, которому соответствует двоичное

число 11, при

этом

. При

сложении чисел 1+1+1 =

3, которому соответствует двоичное

число 11, при

этом ![]() и

так далее.

и

так далее.

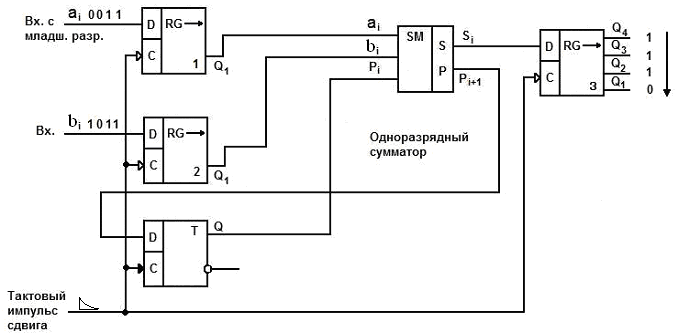

Сумматоры могут быть последовательного и параллельного действия. В сумматорах последовательного действия коды двоичных чисел вводятся в последовательной форме слагаемое за слагаемым, начиная с младшего разряда.

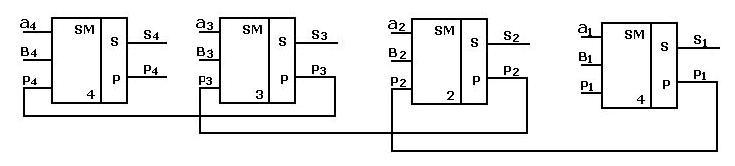

На рис.10.31 изображена схема сумматора последовательного действия, предназначенного для суммирования четырёхразрядных двоичных чисел. Сумматор построен на трёх регистрах сдвига, D-триггере и на одноразрядном сумматоре.

Рис.10.30. Таблица функционирования одноразрядного сумматора

Рис.10.31. Схема сумматора последовательного действия

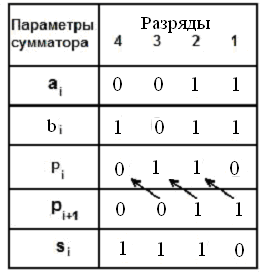

Функционирование сумматора приведено в таблице рис.10.32.

Рис.10.32. Таблица функционирования сумматора

Для ускорения операции сложения используются сумматоры параллельного действия, которые состоят из нескольких однозарядных сумматоров. В таких сумматорах слагаемые поступают одновременно на соответствующие входы однозарядных сумматоров, при этом каждый из однозарядных сумматоров формирует на своих выходах суммы соответствующих разрядов и слагаемые переноса, передаваемых на входы старших разрядов. Схема четырёхразрядного сумматора параллельного действия приведена на рис.10.33.

Рис.10.33. Схема четырёхразрядного сумматора параллельного действия

Мультиплексор - это устройство, которое осуществляет выборку одного из нескольких входов и подключает его к своему единственному выходу, в зависимости от состояния двоичного кода. Другими словами, мультиплексор - переключатель сигналов, управляемый двоичным кодом и имеющий несколько входов и один выход. К выходу подключается тот вход, чей номер соответствует управляющему двоичному коду.

Ну и частное определение: мультиплексор - это устройство, преобразующее параллельный код в последовательный.

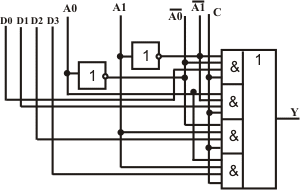

Структуру мультиплексора можно представить различными схемами, например, вот этой:

Рис. 1 – Пример схемы конкретного мультиплексора

Самый большой элемент здесь это элемент И-ИЛИ на четыре входа. Квадратики с единичками - инверторы.

Разберем выводы. Те, что слева, а именно D0-D3, называются информационными входами. На них подают информацию, которую предстоит выбрать. Входы А0-А1 называются адресными входами. Сюда и подается двоичный код, от которого зависит, какой из входов D0-D3 будет подключен к выходу, на этой схеме обозначенному как Y. Вход С – синхронизация, разрешение работы.

На схеме еще есть входы адреса с инверсией. Это чтобы сделать устройство более универсальным.

На рисунке показан, как еще его называют, 4Х1 мультиплексор. Как мы знаем, что число разных двоичных чисел, которые может задавать код, определяется числом разрядов кода как 2n, где n – число разрядов. Задавать нужно 4 состояния мультиплексора, а, значит, разрядов в коде адреса должно быть 2 (22 = 4).

Для пояснения принципа работы этой схемы посмотрим на её таблицу истинности:

A1 |

A0 |

Y |

0 |

0 |

D0 |

0 |

1 |

D1 |

1 |

0 |

D2 |

1 |

1 |

D3 |

Так двоичный код выбирает нужный вход. Например, имеем четыре объекта, и они подают сигналы, а устройство отображения у нас одно. Берем мультиплексор. В зависимости от двоичного кода к устройству отображения подключается сигнал от нужного объекта.

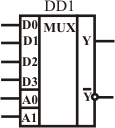

Микросхемой мультиплексор обозначается так:

Рис. 2 – Мультиплексор как МКС

Ход работы:

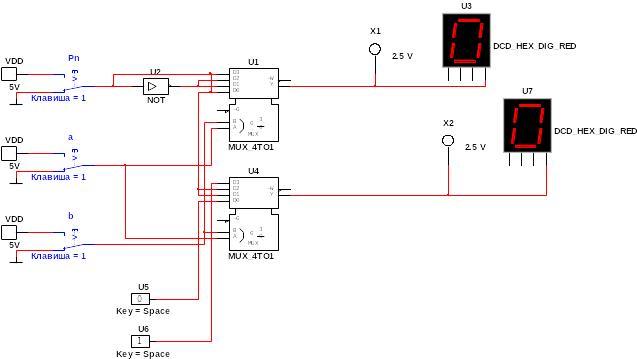

Задание 2.3. Построение одноразрядного сумматора на сдвоенном мультиплексоре 41

Таблица 1 – Таблица истинности полного сумматора

Pn |

An |

Bn |

Sn |

Pn+1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

Составим

карты Карно для нахождения Sn

и

Pn-1

Составим

карты Карно для нахождения Sn

и

Pn-1

Pn anbn |

00 |

01 |

11 |

10 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

Pn anbn |

00 |

01 |

11 |

10 |

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

1 |

Формула мультиплексора:

Рисунок 2 – схема одноразрядного сумматора на базе мультиплексора

1

1 1

1