П1. Работа с пакетом Quartus15.

Активируйте значок запуска или произведите поиск по пути: приложения - программирование – quartus15. При первом входе вы должны выбрать лицензию, которая была выдана вместе с пакетом. В открывшемся окне Start Designing выберите New Project Wizard. (Если Вы собираетесь открывать уже имеющийся проект, то Open Project).

Откроется окно Introduction, нажмите Next.

Откроется окно Directory, Name, Top-Level Entity. В первой строке найдите Вашу папку пользователя, где будут находиться проекты. Во второй строке запишите имя проекта. В третьей строке появится имя файла верхнего уровня, совпадающее с именем проекта. Нажмите Next. (При повторных входах Вам объявят, что в данной папке уже есть проекты, и предложат поменять папку. Этого делать не следует. Ответьте No).

Следующее окно Project Type.Оставьте Empty project. Нажмите Next.

Следующее окно Add Files. Если это первый вход в пакет, у Вас еще нет файлов, которые можно добавить в проект. Если Вы уже работали, то в строке File name найдите, активируя […], нужный файл и добавьте его в проект, нажав Add. Нажмите Next.

Последнее окно позволяет Вам выбрать тип микросхемы. Family & Device Setting. Family CycloneV(…). Device CycloneVSE Mainstream. Name 5CSEMA5F31C6. Нажмите Finish.

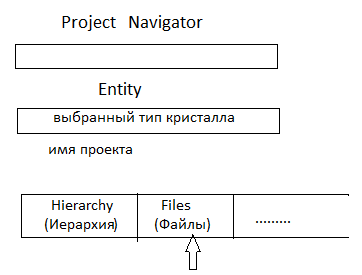

Открылось окно проекта. Во второй строке верхнего меню должно присутствовать название проекта, справа от названия должна быть активна кнопка навигатора проекта

Пользуясь первой строкой верхнего меню, выберите File – New – VerilogHDL File. В открывшееся поле запишите текст программы. Слева от поля текста программы должно быть окно навигатора. Активируйте кнопку «Файлы».

После набора текста нажмите File – Save as и сохраните файл под тем именем, которое дано ему в программе в блоке entity. Вы увидите это название в окне навигатора. Выделите его правой клавишей мыши и, в открывшемся окне выберите Set as top-level entity.

Запустите файл на компиляцию: Processing – Start Compilation или значок – сиреневый треугольник на второй строке верхнего меню. Внимательно следите за этапами компиляции. Они просматриваются слева, ниже окна навигатора. Ошибки выделяются красным цветом. Если сообщения об ошибках появились в нижнем окне сообщений, найдите первое и постарайтесь его прочитать. Откройте файл программы через его название в навигаторе и дважды кликните строку ошибки. В программе будет выделена строка с ошибочной записью. Постарайтесь исправить ошибки самостоятельно, снова сохранить текст файла и поставить его на компиляцию.

П2. Работа с симулятором.

Симуляция в Quartus15 поддерживается пакетом ModelSim. Поэтому, перед тем как начать работу с этим разделом пакета, необходимо прописать путь к пакету ModelSim. Для этого открываем: Tools – Options – EDA Tool Options. В окне ModelSim – А… выделите путь к пакету и скопируйте эту запись. Вставьте этот путь в окно ModelSim. Обе эти записи должны совпадать.

Откройте файл симулятора: File – New – University Program VWF. На экране появится окно Simulation Waveform Editor.

В левой части окна, под записью Name двойным кликом мышью откройте окно вставки Insert Node or Bus. Выберите Node Finder – List ->> - Ok – OK. В окне симулятора появятся оси для входных и выходных значений функции.

Выделите кликом мышью линию входа, и, пользуясь второй строкой верхнего меню, поставьте на входах значения сигнала, требуемые для выполнения лабораторной работы. Для этого можно пользоваться опцией C (Count Value), выставляя начальный уровень сигнала в строке Start value _____ и интервал изменения в строке Count every_____ . Для произвольных временных интервалов изменений входных значений, возможно отметить такой интервал на линии оси и задать на нем необходимое значение. Возможна установка уровней «1», «0», (а также «Z» и «X», но их нежелательно использовать в качестве входных значений).

Сохранить файл File – Save as и произвести симуляцию Simulation – Run Functional Simulation. Если путь к ModelSim прописан верно, Вы увидите файл результата симуляции, т.е. диаграммы работы устройства. По ним можно проверить, соответствует ли описание в программе поставленной задаче. Если такого соответствия нет, надо вернуться к тексту файла и внести коррективы с последующим сохранением и компиляцией. Если Вами получено требуемое устройство, то, при необходимости моделирования, переходите к работе с планировщиком.