Лабораторная работа №5

.docxМинистерство цифрового развития, связи и массовых коммуникаций

Российской Федерации Ордена Трудового Красного Знамени

федеральное государственное бюджетное образовательное

учреждение высшего образования

Московский технический университет связи и информатики

Кафедра Информатики

Лабораторная работа №5

по дисциплине «Структурные схемы микропроцессорных устройств»

Тема: «Минимизация логических выражений»

Вариант №4

Москва 2021

Содержание

Задание 1 3

Задание 2 5

Список использованных источников 7

Задание 1

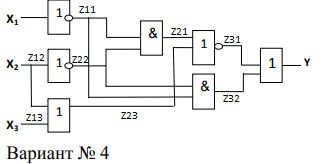

Получить таблицу соответствия/истинности по заданной структурной схеме микропроцессорного устройства.

Исходная принципиальная схема микропроцессорного устройства представлена на рисунке выше. Требуется сформировать таблицу истинности, описывающую процесс его функционирования.

Решение:

1.

Анализ состава и структуры входных,

выходных и промежуточных сигналов.

Схема на рисунке ниже содержит логические

элементы «НЕ» ( ),

логические элементы «И»

),

логические элементы «И» ,

логические элементы «ИЛИ»

,

логические элементы «ИЛИ» ,

выходные сигналы которых поступают на

вход логического элемента «ИЛИ-НЕ»

,

выходные сигналы которых поступают на

вход логического элемента «ИЛИ-НЕ»

, результатом работы (функционирования)

которых является выходной сигнал Y,

и на вход логического элемента «ИЛИ»

, результатом работы (функционирования)

которых является выходной сигнал Y,

и на вход логического элемента «ИЛИ»

,

результатом работы (функционирования)

которых является выходной сигнал Y.

,

результатом работы (функционирования)

которых является выходной сигнал Y.

2.

Построение логической зависимости

3. Построение пустой традиционной таблицы истинности, размерность которой определяется количеством выделенных входных и выходных сигналов, а затем - пустой расширенной таблицы, размерность которой определяется количеством сечений и промежуточных переменных в них.

4. Заполнение указанной расширенной таблицы истинности по сечениям путем последовательного анализа результатов воздействия входных сигналов на рассматриваемое логическое устройство с последующим получением значений выходной величины для всех комбинаций входных (табл. 1).

Таблица 1 – Расширенная таблица истинности по сечениям

№ |

Входы |

Промежуточные сигналы по сечениям z |

Выход |

||||||||||||

|

|

|

Сечение 1 |

Сечение 2 |

Сечение 3 |

|

|||||||||

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

Y |

|||||||

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|||

2 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

|||

3 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|||

4 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

|||

5 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

|||

6 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

|||

7 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|||

8 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

|||

5. По результатам заполнения расширенной таблицы истинности путем исключения из нее столбцов, соответствующих промежуточным сигналам, и ячеек, содержащих знаки логических операций, получаем итоговую таблицу истинности, описывающую процесс функционирования МП устройства, представленного в виде таблицы 2.

Таблица 2 – Итоговая таблица истинности

№ комбинации входов |

Входы |

Выход |

||

|

|

|

Y |

|

1 |

0 |

0 |

0 |

1 |

2 |

0 |

0 |

1 |

1 |

3 |

0 |

1 |

0 |

0 |

4 |

0 |

1 |

1 |

0 |

5 |

1 |

0 |

0 |

1 |

6 |

1 |

0 |

1 |

0 |

7 |

1 |

1 |

0 |

0 |

8 |

1 |

1 |

1 |

0 |

Задание 2

Получить таблицу соответствия/истинности и структурную схему микропроцессорного устройства по заданной математической модели.

Решение:

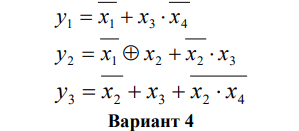

Математическая многомерная логическая модель, которую необходимо реализовать с помощью микропроцессорного устройства, имеет вид:

Структура этой системы уравнений позволяет говорить о том, что в ней имеются 4 входа: х1, х2, х3, x4 и 3 выхода: Y1, Y2, Y3. На этом основании, а также по результатам анализа модели формируется таблица соответствия вида:

Сигналы |

Входы |

Выходы |

|||||

№ комбинации |

X1 |

X2 |

X3 |

X4 |

Y1 |

Y2 |

Y3 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

2 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

3 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

4 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

5 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

6 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

7 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

8 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

9 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

10 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

11 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

12 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

13 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

14 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

15 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

16 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

Далее на основании полученной таблицы соответствия синтезируем структурную схему микропроцессорного устройства, реализующего алгоритм, формализуемый с помощью заданной математической модели:

Список использованных источников

ГОСТ 7.32-2017 Система стандартов по информации, библиотечному и издательскому делу. Отчет о научно-исследовательской работе. Структура и правила оформления. - URL: https://files.stroyinf.ru/Index/655/65555.htm

Н. Г. Захаров, Р. А. Сайфутдинов. Вычислительная техника. Ульяновск: УлГТУ, 2007.