Примеры решения лабораторных работ / Программирование 8535 на СИ

.pdf-два 16-разрядных регистра сравнения OCR1A, OCR1B;

-два 8-разрядных регистра управления TCCR1A, TCCR1B.

Каждый |

из 16-разрядных регистров физически размещается в двух |

регистрах |

||||

ввода/вывода, |

названия |

которых получаются |

добавлением к |

названию |

регистра |

|

буквы «Н» |

(старший байт) и «L» (младший |

байт). Счетный регистр |

таймера |

|||

счетчика TCNT1, например, размещается в регистрах TCNT1H:TCNT1L. |

|

|||||

Счетный регистр TCNT1 и регистры сравнения OCR1A и OCR1B |

|

|

||||

Как только таймер |

Т1 запускается, то |

при |

поступлении |

очередного |

импульса |

|

с источника (им является выход предделителя, на вход которого |

подается сигнал с |

||

тактового генератора или импульсы со входа |

T1) содержимое |

счетного |

регистра |

TCNT1 увеличивается на единицу. Так будет |

происходить непрерывно до |

тех пор, |

|

пока не наступит переполнение счетчика или принудительное его обнуление. При переполнении регистра TCNT1 возможна генерация прерывания TIMER0_OVF по переполнению таймера Т1.

Врегистры сравнения OCR1A и OCR1B записываются необходимые

пользовательские значения. При совпадении регистров OCR1A или OCR1B напряжения изменяются. Этот момент можно использовать совпадению TIMER1_СОМРA и TIMER1_СОМРA.

значений счетного |

регистра |

и |

|

на |

выходах OC1A |

или OC1B |

|

для |

генерирования прерываний |

по |

|

Регистры управления TCCR1A и TCCR1B

Для управления таймером/счетчиком используются два регистра управления:

TCCR1A, TCCR1B. |

Форматы этих регистров и назначение отдельных битов - |

приведены в табл. 1.3. |

|

Табл. 1. Разряды регистра TCCR1A

Бит |

Название |

|

|

Описание |

|

|

||

|

|

|

|

|

|

|

||

7,6 |

COM1A1:COM1A0 |

Режим работы |

блоков сравнения |

A и |

В. |

Эти разряды определяют |

||

поведение выводов ОС1А |

и |

ОС1В |

при наступлении события |

|||||

|

|

|||||||

5,4 |

COM1B1:COM1B0 |

«Совпадение». Влияние содержимого этих разрядов на состояние |

||||||

|

|

вывода зависит от режима работы таймера/счетчика |

||||||

3,2 |

FOC1A:FOC1B |

Принудительное |

изменение |

состояния |

выводов соответственно |

|||

OC1A и OC1B |

|

|

|

|

|

|||

|

|

|

|

|

|

|

||

|

|

|

||||||

|

|

Режим работы таймера/счетчика. Совместно с разрядами |

||||||

1,0 |

WGM11:WGM10 |

WGM13:WGM12 регистра TCCR1B определяют режим работы |

||||||

|

|

таймера/счетчика Т1 |

|

|

|

|

||

Табл. 2. Формат регистра TCCR1B

Бит |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

Обозначение |

ICNC1 |

ICES1 |

- |

WGM13 |

WGM12 |

CS12 |

CS11 |

CS10 |

|

|

|

|

|

|

|

|

|

Примечание: биты WGM13...WGM10 используются в основном |

для работы |

таймера в режимах ШИМ. Содержимое битов COM1n1:COM1n0 тоже |

должно быть |

«0» при отсутствии связи таймера 1 с выводами OC1x. |

|

Значения разрядов CS12...CS10 определяют коэффициент деления тактовой частоты и источник тактовых импульсов для таймера Т1. Их возможные значения представлены в табл. 3.

Табл. 3. Выбор коэффициента предделителя таймера Т1

Биты TCCR1B |

Коэффициент предделителя таймера Т1 |

|||

|

|

|

||

CS12 |

CS11 |

CS10 |

||

|

||||

0 |

0 |

0 |

Таймер/счетчик остановлен |

|

0 |

0 |

1 |

clkI/o |

|

0 |

1 |

0 |

clkI/o/8 |

|

0 |

1 |

1 |

с1кю/64 |

|

1 |

0 |

0 |

clkI/o/256 |

|

1 |

0 |

1 |

clkI/o/1024 |

|

1 |

1 |

0 |

Вывод T1, счет осуществляется по спадающему фронту импульсов |

|

1 |

1 |

1 |

Вывод Т1, счет осуществляется по нарастающему фронту импульсов |

|

Регистр захвата ICR1

Регистр захвата ICR1 входит в состав блока захвата, назначение которого -

сохранение в |

определенный |

момент |

времени состояния |

таймера/счетчика в |

регистре захвата |

ICR1. Это |

действие |

может производиться |

либо по активному |

фронту сигнала на выводе ГСР микроконтроллера, либо по сигналу от аналогового

компаратора. |

Одновременно |

с |

записью в |

регистр |

захвата |

устанавливается |

флаг |

||||||||||

ICF1 регистра TIFR и генерируется запрос на прерывание. Разрешение прерывания |

|||||||||||||||||

осуществляется |

установкой |

разряда |

TICIE1 |

регистра |

TIMSK. |

Для |

управления |

||||||||||

схемой захвата используются два разряда |

регистра |

TCCR1B |

- |

ICNC1 |

(бит 7) и |

||||||||||||

ICES1 (бит 6). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Разряд |

ICNC1 |

управляет |

схемой |

подавления помех. Если этот разряд |

|||||||||||||

сброшен в «0», схема подавления помех |

выключена |

и |

захват |

производится |

по |

||||||||||||

первому же активному фронту. Если же |

этот |

разряд |

установлен в «1», |

то |

при |

||||||||||||

появлении |

активного |

фронта |

производится |

4 выборки с частотой, равной тактовой |

|||||||||||||

частоте микроконтроллера. Захват будет выполнен только в том случае, если |

все |

||||||||||||||||

выборки |

имеют |

уровень, соответствующий |

активному |

фронту |

сигнала |

(логическая |

|||||||||||

«1» для нарастающего и логический 0 для спадающего). |

|

|

|

|

|

|

|

|

|||||||||

Активный фронт сигнала, т. е. |

фронт, по которому будет выполнено |

||||||||||||||||

сохранение содержимого счетного регистра в регистре |

|

захвата, |

определяется |

||||||||||||||

состоянием разряда ICES1. Если этот разряд сброшен в «0», то активным является |

|||||||||||||||||

спадающий |

фронт. |

Если |

разряд |

установлен |

в |

«1», |

то |

активным |

является |

||||||||

нарастающий фронт. Для захвата по сигналу с вывода ГСР, этот вывод должен быть

сконфигурирован |

как |

входной |

(разряд |

регистра |

DDRx, |

соответствующий выводу |

||||

ICP, должен быть сброшен в «0»). |

Если |

же |

он будет |

сконфигурирован как |

||||||

выходной, |

захват |

можно |

будет |

осуществлять |

программно, |

управляя |

||||

соответствующим |

разрядом порта. Следует |

понимать, |

что |

между |

изменением |

|||||

состояния входа |

блока захвата и копированием счетного регистра в регистр захвата |

||||||

таймера/счетчика |

проходит |

некоторое |

время. |

Эту |

задержку |

вносит |

каскад, |

состоящий из синхронизатора и детектора фронта. Величина задержки составляет |

|

||||||

2,5..3,5 машинных циклов. При включении схемы подавления помех задержка увеличивается еще на 4 машинных цикла.

Регистры разрешения и обработки прерываний TIMSK и TIFR |

|

|

|

|

||||||||

Для |

разрешения/запрета прерываний от таймеров/счетчиков |

предназначен |

||||||||||

регистр TIMSK |

(Timer/Counter |

Interrupt MaSK Register |

- |

регистр |

маски |

|||||||

прерываний |

от |

таймеров/счетчиков). |

Для |

таймера |

Т1 |

в |

этом |

регистре |

||||

задействованы следующие биты: |

|

|

|

|

|

|

|

|

|

|||

- |

ТГСШ1 |

(бит |

5) - флаг |

разрешения |

прерывания |

по |

событию |

«Захват» |

||||

таймера Т1; |

|

|

|

|

|

|

|

|

|

|

|

|

- |

ОСГЕ1А (бит 4) - флаг |

разрешения |

прерывания |

по |

событию |

«Совпадение |

||||||

А» таймера Т1; |

|

|

|

|

|

|

|

|

|

|

|

|

- |

OCTE1B (бит 3) - флаг разрешения прерывания по |

событию |

«Совпадение |

|||||||||

B» таймера Т1; |

|

|

|

|

|

|

|

|

|

|

|

|

- |

T0IE1 (бит 2)- флаг разрешения прерывания по переполнению таймера Т1. |

|||||||||||

Для индикации наступления прерываний от таймеров предназначен регистр |

|

|||||||||||

TIFR (Timer/Counter Interrupt Flag Register |

- |

регистр |

флагов |

прерываний от |

||||||||

таймеров/счетчиков). |

Для |

таймера |

Т1 |

в этом |

|

регистре |

задействованы |

следующие |

||||

биты: |

|

|

|

|

|

|

|

|

|

|

|

|

-ICF1 (бит 5) - флаг прерывания по событию Захват» таймера Т1;

-0CF1A (бит 4)- флаг прерывания по событию «Совпадение А» таймера Т1;

-0CF1B (бит 3)- флаг прерывания по событию «Совпадение B» таймера Т1;

-T0V1 (бит 2) - флаг прерывания по переполнению таймера Т1.

При наступлении какого-либо |

события соответствующий |

флаг |

регистра |

TIFR устанавливается в «1». При запуске подпрограммы обработки прерывания он |

|||

аппаратно сбрасывается в «0». Любой |

флаг может быть сброшен |

в «0» |

вручную |

путем записи в него логической «1». |

|

|

|

Примеры

Пример 1. В качестве примера, рассмотрим программу, которая выводит в

двоичном коде на |

P0RTC число |

секунд между двумя передними фронтами сигнала |

на ICP(PD6). Т. е. |

используется |

прерывание по захвату таймера Т1. Максимальное |

возможное значение выводимого времени равно Т=1024-65535/(8-106)=8,38 с. При

большей продолжительности паузы таймер переполнится и начнёт считать сначала.

// ---------------------------------------------------------------

//Счёт времени с помощью 16-ти разрядного таймера //Входы: ICP(PD6) - подключаем к кнопке

//Выходы: Порт С - на светодиоды

#include <iom8535v.h> #include <macros.h>

unsigned int v;

void port_init(void) |

|

{ |

|

PORTC = 0x00; |

|

DDRC = 0xFF; |

// порт С работает на выход |

}

void timer1_init(void) // инициализация таймера Т1

{ |

|

|

|

|

TCCR1B |

= 0x00; |

// |

Остановка таймера |

|

TCNT1H |

= 0x00; |

// |

Установка начального |

|

TCNT1L |

= 0x01; |

// |

значения счётного регистра |

|

TCCR1A |

= 0x00; |

// |

Запуск таймера в режиме |

Normal, |

|

|

|

|

// предделитель 1024, захват происходит |

TCCR1B |

= 0xC5; |

|

// по нарастающему фронту сигнала на ICP, |

|

|

|

|

|

// при этом включена защита от помех |

} |

|

|

|

|

//Подпрограмма обработки прерывания по захвату Т1 |

||||

#pragma |

interrupt_handler timer1_capt_isr:6 |

|||

void timer1_capt_isr(void) |

|

|||

CLI (); |

|

|

|

|

TCCR1B |

= 0; |

|

// |

Остановка таймера |

v=ICR1L; |

|

// |

Считывание значения регистра захвата |

|

v|=(int)ICR1H << 8; |

|

|

||

PORTC=v/7812; |

// |

Из единиц таймера переводим это значение в |

||

|

|

|

// секунды и выводим в порт С |

|

TCNT1H |

= |

0x00; |

// |

Установка начального |

TCNT1L |

= |

0x01; |

// |

значения счётного регистра |

TCCR1B |

= |

0xC5; |

// |

Запуск таймера |

SEI(); |

|

|

|

|

} |

|

|

|

|

void init_devices(void)

{

CLI (); |

|

|

port_init(); |

|

|

timer1_init(); |

|

|

TIMSK = 0x20; |

//Разрешение прерывания |

позахвату таймера Т1 |

SEI(); |

|

|

} |

|

|

void main(void) |

|

|

{ |

|

|

init_devices(); |

|

|

for (;;); |

|

|

} |

|

|

Пример 2. Рассмотрим работу таймера Т1 в режиме |

широтно-импульсной |

уляции. Программа использует оба выхода OCR1A |

и OCR1B таймера Т1, |

чем скважности этих каналов набираются раздельно - на младшей и старшей

адах порта A.

// ---------------------------------------------------------------

//Использование таймера Т1 в режиме широтно-импульсной модуляции

//Входы: PA0-PA3 - задают скважность канала A |

|

|||

// |

PA4-PA7 - канала В. |

|

|

|

//В итоге |

получаем по |

16 скважностей для |

каждого |

канала |

//Выходы: |

OCR1A (PD5) |

- ШИМ-выход канала |

А |

|

// |

OCR1B (PD4) - ШИМ-выход канала B |

|

||

#include <iom8535v.h> #include <macros.h>

void port_init(void)

{

PORTA = 0x00; |

|

|

|

|

||

DDRA = 0x00; |

|

|

//Порт А настраиваем как вход |

|||

PORTD = 0x00; |

|

|

|

|

||

DDRD = 0x30; |

|

//Порт D - выход |

|

|||

} |

|

|

|

|

|

|

void timer1_init(void) |

|

|

//Инициализация таймера Т1 |

|||

{ |

|

|

|

|

|

|

TCCR1B = |

0x00; |

//Таймер пускаем в режиме 10-ти битного быстрого |

||||

TCCR1A = |

0xA3; |

//ШИМа, с предделителем 1, выводы OC1A и OC1B при |

||||

TCCR1B = |

0x09; |

//совпадении сбрасываются в «0» |

|

|||

} |

|

|

|

|

|

|

void init_devices(void) |

|

|

|

|

||

{ |

|

|

|

|

|

|

CLI(); |

|

|

|

|

|

|

port_init(); |

|

|

|

|

||

timer1_init() ; |

|

|

|

|

||

SEI(); |

|

|

|

|

|

|

} |

|

|

|

|

|

|

void main(void) |

|

|

|

|

||

{ |

|

|

|

|

|

|

init_devices() ; |

|

|

|

|

||

for (;;) |

|

|

|

|

|

|

{ |

|

|

|

|

|

|

OCR1AH=(PINA&0x0F) |

>> 2; |

// |

записываем в регистр сравнения А |

|||

OCR1AL=(PINA&0x0F) |

<< 6; |

// |

значение новой скважности с PA0-PA3 |

|||

OCR1BH=(PINA&0xF0) |

>> 6; |

// |

записываем в регистр сравнения B |

|||

OCR1BL=(PINA&0xF0) |

<< 2; |

// |

значение новой скважности с PA4-PA7 |

|||

} |

|

|

|

|

|

|

} |

|

|

|

|

|

|

// --------------------------------------------------------------- |

||||||

|

|

|

Задание на выполнение |

|

||

1. |

Напишите программу включения/выключения выхода PD0 с заданным |

|||||

периодом: |

|

|

|

|

|

|

а) 1 мс |

|

б) 5 мс |

|

|

в) 10 мс |

г) 20 мс |

д) 50 мс |

е) 100 мс |

|

ж) 500 мс |

з) 1 с |

||

и) 2 с |

|

к) 5 с |

|

|

|

|

2. |

Реализуйте программу светофор: |

|

||||

- |

в дневном режиме продолжительность включения сигналов красный, |

|||||

желтый, зеленый, желтый 5с/1с/3с/0,5с; |

|

|

|

|||

- |

в ночном режиме включается только желтый свет - 0,5с горит, 1 с - не |

|||||

горит. |

|

|

|

|

|

|

Режим включения задается входом PB0. |

|

|||||

3. |

Напишите программу расчета частоты генератора (на модуле вход |

|||||

генератора 50 Гц) с точностью до сотых долей герц. Результат вывести: |

||||||

- |

в двоичном коде; |

|

|

|

|

|

- |

на семисегментный индикатор. |

|

||||

4. Составьте программу, показывающую время между двумя нажатиями кнопки с точностью до 0,1 с. Считать до 999,9 с. Вывести это число на семисегментный индикатор.

5.Напишите программу, реализующую задержку переднего фронта сигнала с

тумблера. Задержку задавать в |

секундах в двоичном коде с помощью пяти |

|

оставшихся тумблеров. Если продолжительность |

сигнала на входе меньше |

|

продолжительности установленной |

задержки, то срабатывания сигнала на выходе |

|

не происходит. |

|

|

6.Используя программу «Пример 2» реализуйте 8-ми разрядный ШИМ с

выводом |

значения |

скважности |

на |

семисегментные |

индикаторы. |

Скважность |

задается двоичным кодом (тумблерами и кнопками). |

|

|

||||

7. |

Составьте |

программу, |

которая в течение 10 |

секунд плавно изменяет |

||

скважность от 0 до 1, и затем в течение 5 с - от 1 до 0 (использовать таймер Т1 в режиме ШИМ).

Работа №6. Использование аналого-цифрового преобразователя

Цель работы

Познакомиться с работой АЦП микроконтроллера ATmega8535. Составить и отладить программу работы с АЦП (прием кода и выдача его или напряжения на индикацию).

Пояснения к работе

Микроконтроллер ATMega8535 позволяет вводить и обрабатывать до 8 аналоговых сигналов. Для этого в состав контроллера входит 10-разрядный АЦП последовательного приближения. Основные параметры этого АЦП следующие:

-абсолютная погрешность: ±2 МЗР;

-интегральная нелинейность: ±0.5 МЗР;

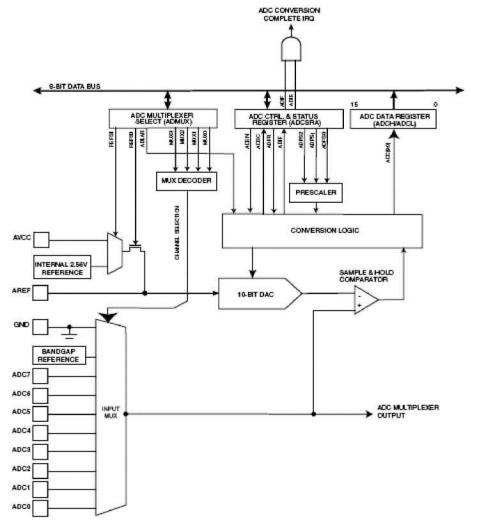

-время преобразования: 65.260 мкс. Структурная схема АЦП приведена на рис. 1.

Рис. 1. Структурная схема АЦП микроконтроллера

АЦП содержит:

- 8-ми канальный аналоговый мультиплексор с дешифратором каналов;

-внутренний источник опорного напряжения 2,56В со схемой выбора;

-АЦП последовательного приближения;

-предделитель для выбора времени преобразования сигнала.

Для ввода аналоговых сигналов ADC0...ADC7 в контроллере используются |

||||||||||

альтернативные |

функции |

порта |

А, |

соответственно |

выводы |

PA0...PA7 |

||||

(приложение 1). Следует обратить |

внимание, что биты портов, используемые как |

|||||||||

входы |

АЦП, |

должны |

быть |

запрограммированы |

как |

входы, |

при |

этом |

||

подтягивающие |

резисторы |

должны |

быть |

выключены, |

иначе это |

приведет |

к |

|||

искажению входного напряжения. |

|

|

|

|

|

|

|

|||

Как видно из рис. 1, на вход АЦП может подаваться |

сигнал |

с одного |

из |

|||||||

входов |

ADC0...7, фиксированное |

напряжение 1,22 В |

(Bandgap Reference) |

|

или |

|||||

напряжение 0 В. В качестве источника опорного напряжения для АЦП может

использоваться как |

напряжение питания микроконтроллера, |

так и |

внутренний |

(2,56 В) либо внешний источник опорного напряжения. АЦП |

может |

формировать |

|

сигнал прерывания |

при окончании цикла преобразования |

(ADC |

Conversion |

Complete IRQ). |

|

|

|

Регистры АЦП

Управление работой АЦП выполняется с помощью 4 регистров:

-регистр выбора канала АЦП и источника опорного напряжения ADMUX;

-регистр управления и статуса АЦП ADCSRA;

-два регистра данных ADCH, ADCL (так как выходной код АЦП 10разрядный, то используются эти 2 регистра).

Регистр выбора канала ADMUX

Номер входного канала АЦП и источник опорного напряжения задаются в регистре ADMUX (табл. 1).

Табл. 1. Разряды регистра ADMUX

Разряд |

Название |

Описание |

7,6 |

REFS1:REFS0 |

Выбор источника опорного напряжения |

5 |

ADLAR |

Выравнивание результата преобразования |

4...0 |

MUX4...MUX0 |

Выбор входного канала |

Два старших разряда этого регистра определяют тип источника опорного

напряжения ИОН (табл. 2). Опорное напряжение определяет |

напряжение, при |

котором выходной код максимален (для 10-разрядного АЦП - это |

1023). Младшие |

4 разряды регистра позволяют выбрать номер канала АЦП (табл. 3). Результат

преобразования |

аналогового |

сигнала |

размещается |

в |

двух |

8-ми |

разрядных |

||||

регистрах. |

Для |

управления |

|

выравниванием |

результата |

преобразования |

(10-ти |

||||

битного |

кода) |

служит разряд |

ADLAR регистра |

ADMUX. |

Если |

этот |

разряд |

||||

установлен в «1», результат преобразования выравнивается по левой границе 16разрядного слова, размещенного в регистрах ADCH:ADCL, если сброшен в «0» - по правой границе.

Табл. 2. Выбор источника опорного напряжения

6,7 биты ADMUX |

Источник опорного напряжения |

|

|

||

REFS1 |

REFS0 |

|

|

|

|

0 |

0 |

Внешний ИОН, подключенный к выводу AREF; внутренний ИОН отключен |

0 |

1 |

Напряжение питания AVCC |

|

|

|

1 |

1 |

Внутренний ИОН 2,56В, подключенный к выводу AREF |

Табл. 3. Управление входным мультиплексором

4...0 биты ADMUX |

Номер канала АЦП |

|

|

||

MUX4...MUX0 |

||

|

||

|

|

|

00000 |

ADC0 |

|

00001 |

ADC1 |

|

|

||

00010 |

ADC2 |

|

|

||

00011 |

ADC3 |

|

00100 |

ADC4 |

|

|

||

00101 |

ADC5 |

|

00110 |

ADC6 |

|

00111 |

ADC7 |

|

|

||

|

|

|

10000 |

ADC0ADC1 |

|

|

||

|

|

|

11110 |

1.22 В |

|

11111 |

0B (GND) |

Регистр управления и статуса ADCSRA

Регистр ADCSRA позволяет запустить и остановить работу АЦП, выбрать режим работы (одиночный или непрерывный), разрешить работу прерывания по окончании преобразования АЦП, а также задать длительность преобразования аналогового сигнала в цифровой код. Назначение битов регистра приведено в табл. 4.

Табл. 4. Биты регистра ADCSRA _____________________________________________________

Разряд |

Название |

Описание |

7 |

ADEN |

Разрешение АЦП (1 - включено, 0 - выключено) |

6 |

ADSC |

Запуск преобразования (1 - начать преобразование) |

5 |

ADFR |

Выбор режима работы АЦП |

4 |

ADIF |

Флаг прерывания АЦП |

3 |

ADIE |

Разрешение прерывания АЦП |

2...0 |

ADPS2:ADPS0 |

Выбор частоты преобразования |

|

|

Разрешить работу АЦП можно установкой бита ADEN регистра ADCSRA в состояние логической «1».

Для запуска АЦП необходимо установить в «1» бит ADSC регистра

ADCSRA.

Существует два режима работы АЦП:

- режим одиночного преобразования, когда запуск каждого преобразования инициируется пользователем;

- |

режим |

непрерывного |

преобразования, |

когда |

запуск |

преобразований |

||||||

выполняется непрерывно через определенные интервалы времени. |

|

|

|

|

|

|

||||||

Режим работы АЦП определяется состоянием разряда |

ADFR. |

Если |

он |

|||||||||

установлен в «1», АЦП работает в режиме непрерывного |

преобразования. |

В |

этом |

|||||||||

режиме |

запуск |

|

каждого |

следующего |

|

преобразования |

|

осуществляется |

||||

автоматически после окончания текущего. Если же разряд |

ADFR |

|

сброшен |

в |

«0», |

|||||||

АЦП |

работает |

в |

режиме |

одиночного |

преобразования |

и |

|

запуск |

|

каждого |

||

преобразования осуществляется |

по команде |

пользователя. |

Количество |

внутренних |

||||||||

циклов АЦП для преобразования входного сигнала в режиме однократного запуска

составляет 25 циклов для |

первого преобразования, 14 |

- для всех последующих, и |

14 - для работы в режиме непрерывного преобразования. |

|

|

Тактирование работы |

внутреннего цикла АЦП |

осуществляется от тактового |

генератора микроконтроллера через предделитель. Частота работы АЦП задается

коэффициентом |

деления |

предделителя |

и |

определяется |

состоянием |

разрядов |

|

ADPS2..ADPS0 регистра ADCSRA. Варианты задания коэффициента предделителя |

|||||||

приведены в табл. 5. |

|

|

|

|

|

|

|

Табл. 5. Задание коэффициента деления предделителя АЦП |

|

|

|||||

|

|

|

|

|

|

|

|

ADPS2 |

ADPS1 |

|

ADPS0 |

|

Коэффициент деления |

|

|

|

|

|

|

|

|

|

|

0 |

0 |

|

0 |

|

|

2 |

|

0 |

0 |

|

1 |

|

|

2 |

|

0 |

1 |

|

0 |

|

|

4 |

|

0 |

1 |

|

1 |

|

|

8 |

|

1 |

0 |

|

0 |

|

|

16 |

|

1 |

0 |

|

1 |

|

|

32 |

|

1 |

1 |

|

0 |

|

|

64 |

|

1 |

1 |

|

1 |

|

|

128 |

|

Следует отметить, что от скорости преобразования АЦП зависит и точность

преобразования. |

|

Наибольшая точность |

преобразования достигается, если тактовая |

|||||||

частота |

модуля |

АЦП |

находится в диапазоне 50...200 кГц. Соответственно |

|||||||

коэффициент |

деления |

предделителя |

рекомендуется |

выбирать |

таким, |

чтобы |

||||

тактовая |

частота |

модуля |

АЦП |

находилась в |

указанном диапазоне. Если же |

|||||

точности |

преобразования |

меньше |

10 |

разрядов |

достаточно, можно использовать |

|||||

более высокую частоту, увеличивая тем самым частоту выборки. Для этой же цели

предназначен |

разряд |

ADCHM (бит 4) регистра SFIOR. При установке |

этого |

||||||

разряда |

скорость |

преобразования |

АЦП |

увеличивается. |

Однако |

при |

этом |

||

увеличивается и энергопотребление микроконтроллера. |

|

|

|

|

|||||

При работе с АЦП по прерываниям разрешение прерывания осуществляется |

|||||||||

установкой |

в |

«1» |

разряда ADIE регистра ADCSRA при |

установленном |

флаге I |

||||

(бит 7) |

регистра |

SREG. Как и флаги остальных прерываний, флаг |

ADIF |

||||||

сбрасывается |

аппаратно при запуске |

подпрограммы обработки прерывания |

от |

АЦП |

|||||

или программно записью в него логической «1». |

|

|

|

|

|

||||

50