- •Минимизация логических функций

- •Минимизация логических функций методом Квайна

- •Минимизация логических функций методом Квайна

- •Минимизация логических функций методом Квайна

- •Минимизация логических функций методом Квайна

- •Минимизация логических функций методом карт Карно

- •Минимизация логических функций методом карт Карно

- •Минимизация логических функций методом карт Карно

- •Минимизация логических функций методом карт Карно

- •Минимизация логических функций методом карт Карно

- •Минимизация логических функций методом карт Карно

- •Минимизация логических функций методом карт Карно

- •Минимизация логических функций методом карт Карно

- •Минимизация логических функций методом карт Карно

- •Минимизация логических функций методом карт Карно

- •Минимизация логических функций методом карт Карно

- •Минимизация логических функций методом карт Карно

- •Как использовать элементы с разным числом входов

Минимизация логических функций методом карт Карно

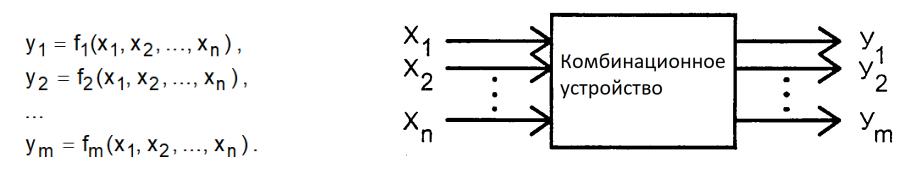

Синтез комбинационных устройств с несколькими выходами.

Комбинационной схемой (комбинационным устройством) называется цифровое устройство, выходные сигналы которого зависят только от входных сигналов и не зависят от предыдущих состояний этого устройства. Если множество входных сигналов комбинационного устройства X = {x1, x2, …, xn} и множество выходных сигналов

Y = {y1, y2, …, ym}, то в общем случае комбинационное устройство будет описываться системой логических уравнений Y=F(X), или

При синтезе комбинационного устройства, описываемого системой m логических функций, то есть имеющего несколько (m) выходов, карты Карно составляют для каждой логической функции. Можно произвести минимизацию каждой из этих m функций и таким образом синтезировать устройство, состоящее из m раздельно действующих цепей, каждая из которых реализовывала бы определенную логическую функцию. Однако если даже каждая из этих функций будет построена минимальным образом, в целом комбинационное устройство может оказаться не минимальным. Поэтому целесообразно рассматривать все m функций в совокупности. При этом стремятся выделить в них общие члены или группы членов так, чтобы с выходов функциональных элементов, которые их реализуют, можно было бы снимать одни и те же сигналы для формирования нескольких логических функций.

Минимизация логических функций методом карт Карно

Принцип получения минимальной формы сводится к нахождению минимального набора дизъюнктивных членов с минимальным числом входящих в них аргументов, достаточного для получения всех формируемых устройством функций. Однако при таком подходе некоторые функции могут оказаться не в минимальной форме.

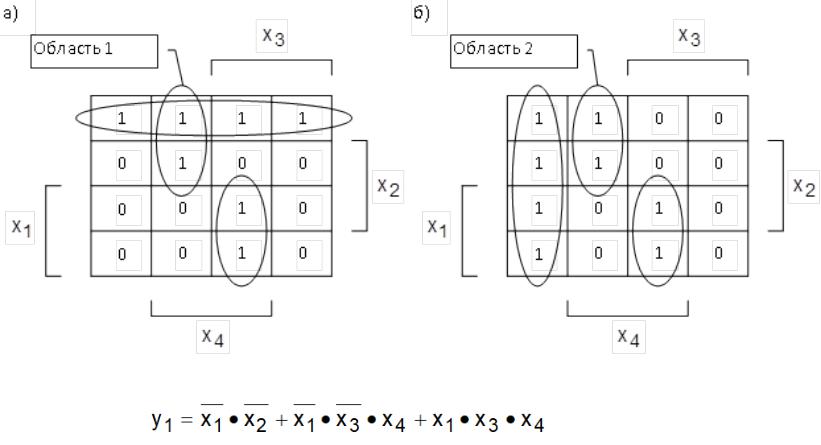

Пример 2. Рассмотрим совместную минимизацию двух логических функций y1 (а) и y2 (б), заданных следующими картами Карно.

Минимизация функции y1 не вызывает затруднений и приводит к МДНФ следующего вида:

Минимизация логических функций методом карт Карно

При минимизации функции y2 область 2 не следует объединять с другими клетками, поскольку такая же область (область 1) имеется на карте Карно для функции y1 и она уже реализована соответствующим членом МДНФ. С учетом этого факта МДНФ для функции y2 примет вид:

Из сравнения выражений для МДНФ функций y1 и y2 видно, что они имеют по 2 общих дизъюнктивных члена. Их можно реализовать устройствами, выходные сигналы которых будут участвовать в формировании функций y1 и y2

одновременно. Таким образом, при минимизации логических функций устройств с несколькими выходами следует стремиться к выявлению возможно большего числа одинаковых областей, охватывающих единицы в картах Карно разных функций.

Минимизация логических функций методом карт Карно

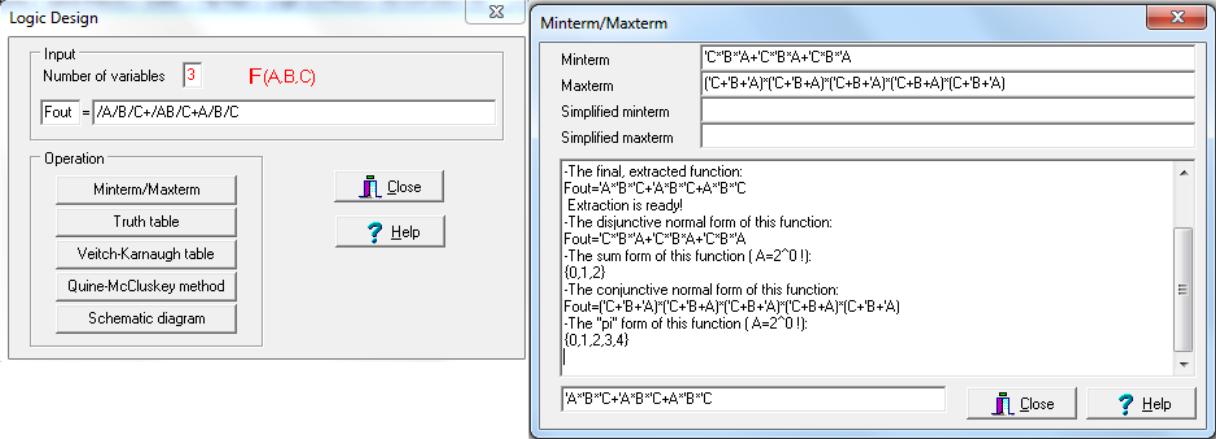

•Современные программы-симуляторы электронных устройств позволяют автоматизировать минимизацию логических функций. К таким относится и симулятор TINA (платная версия). В меню Tools выбираем инструмент Logic Design (в бесплатной версии TINA-TI он отсутствует), устанавливаем Number of variables – 3 и набираем функцию алгебры логики (ФАЛ). Перед инверсными переменными будем ставить наклонную черту «/». Вместо наклонной черты можно ставить верхний штрих «’».

•Нажимаем Minterm/Maxterm и получаем алгебраические выражения СДНФ и СКНФ.

Минимизация логических функций методом карт Карно

Далее нажимаем Truth table и получаем для проверки исходную таблицу истинности.

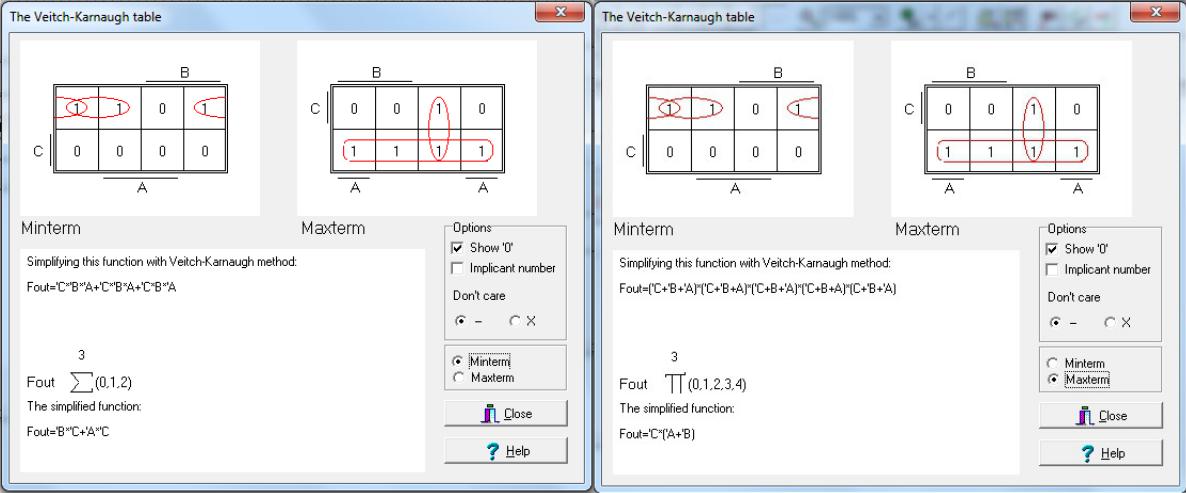

Нажав кнопку Veitch-Karnaugh table, вы получите возможность выполнить операцию графической минимизации ФАЛ. Если нажать кнопку Minterm, получим выраженную через минтермы упрощенную выходную СДНФ:

Если нажать кнопку Maxterm, получим выраженную через макстер- мы упрощенную СКНФ:

Минимизация логических функций методом карт Карно

Минимизация логических функций методом карт Карно

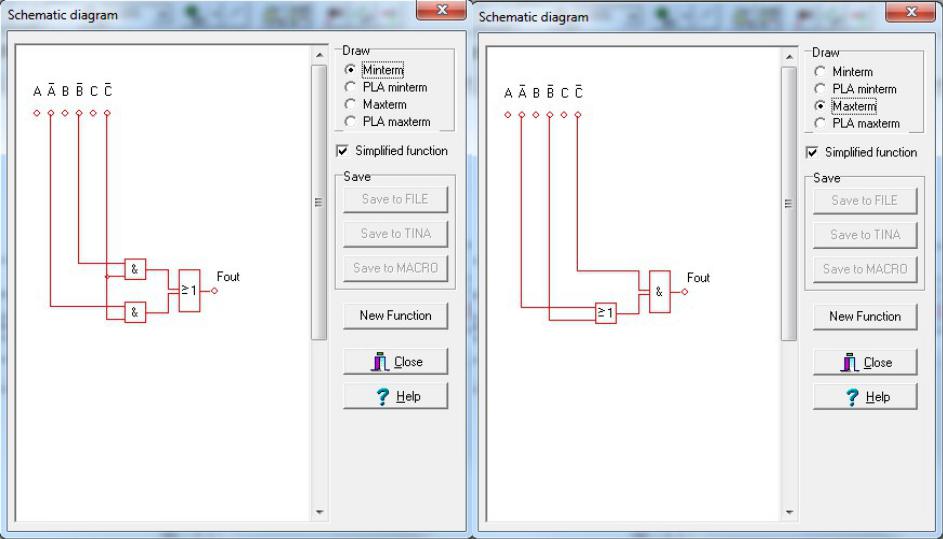

Нажав Schematic Diagram и выбрав Minterm, получим схемную реализацию ФАЛ на элементах 2И, 2ИЛИ. Если выбрать Maxterm, получим схемную реализацию на элементах 2ИЛИ, 2И.

Таким образом, программа TINA позволяет провести минимизацию и реализовать функции

алгебры логики в виде комбинационных схем из цифровых логических элементов.

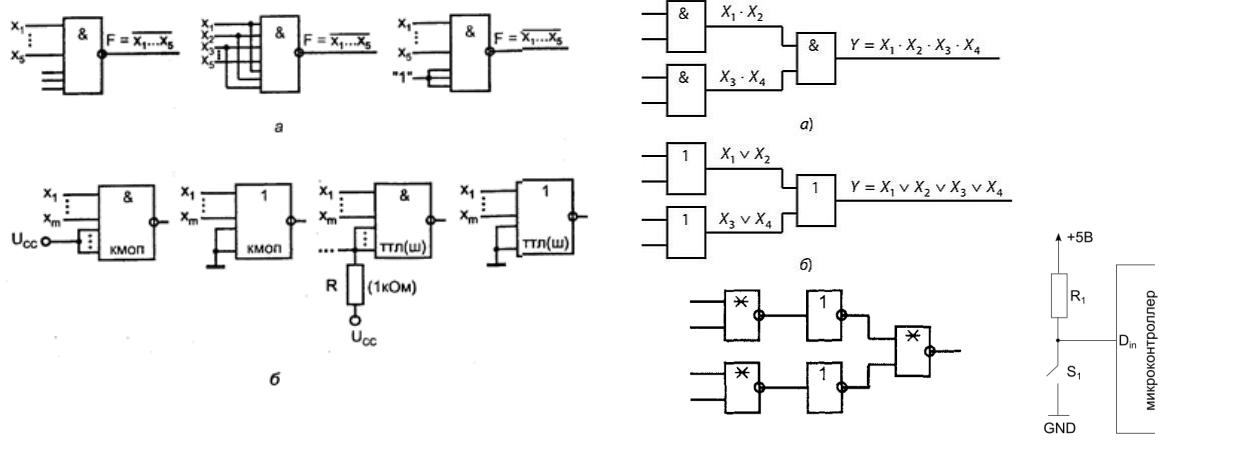

Как использовать элементы с разным числом входов

•Логический 0 – соединение входа ЛЭ с землей.

•Логическая 1 – соединение входа ЛЭ с напряжение питания (+5 В) через резистор для ТТЛ – 1 КОм, для КМОП – напрямую без резистора.

•Если количество входов избыточное, лишние входы можно объединять. Недостаток – увеличение входного тока. Правильнее подавать логический 0 или логическую 1.

•Если количество входов недостаточное, использовать дополнительные логические элементы И, ИЛИ.