Обама Х.С. Лаб 2

.docxМИНИСТЕРСТВО ЦИФРОВОГО РАЗВИТИЯ, СВЯЗИ И МАССОВЫХ КОММУНИКАЦИЙ РОССИЙСКОЙ ФЕДЕРАЦИИ

Ордена Трудового Красного Знамени федеральное государственное

бюджетное образовательное учреждение высшего образования

"Московский технический университет связи и информатики"

Факультет Радио и Телевидения

Лабораторная работа № 2

" системой автоматизированного проектирования "

Выполнил студент групп БРМ1902:

Обама Х.С.

Бонсэн Й.Ф

Проверил:

Шубин Д.Н.

.

Цель работы.

Целью работы является изучение системы автоматизированного проектирования (САПР) Xilinx ISE WebPack, ознакомление с основами языка VHDL и реализация на ПЛИС логической схемы комбинационного типа с использованием функционала графического редактора и модулей на языке описания аппаратуры VHDL

Задания для выполнения лабораторной работы

Предварительная подготовка к выполнению лабораторной работы

1. Изучить описание к данной лабораторной работе и рекомендованную литературу.

2. Ознакомиться с основами языка программирования VHDL

3. Используя сведения, полученные при подготовке, написать листинг программы, описывающей заданное устройство на языке VHDL. Данные для проектирования устройства можно получить у преподавателя или взять из Таблицы 2.1 (номер варианта уточнить у преподавателя). Из Таблицы 2.2 переписать свой вариант установки для значений переменных для выполнения симуляции.

4. Подготовить ответы на контрольные вопросы, приведенные в данном описании лабораторной работы.

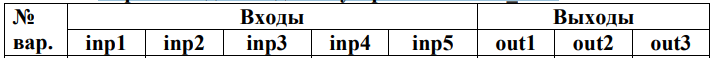

Варианты для создания устройства demo_vhdl

![]()

Варианты установки значений переменных, мкс

![]()

![]()

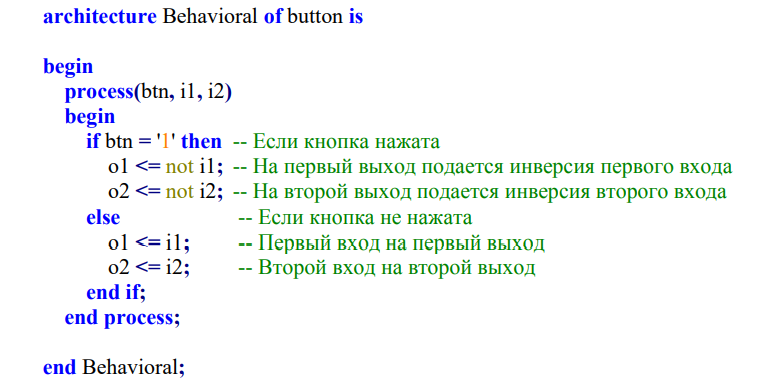

архитектура модуля будет иметь следующий вид

готовая

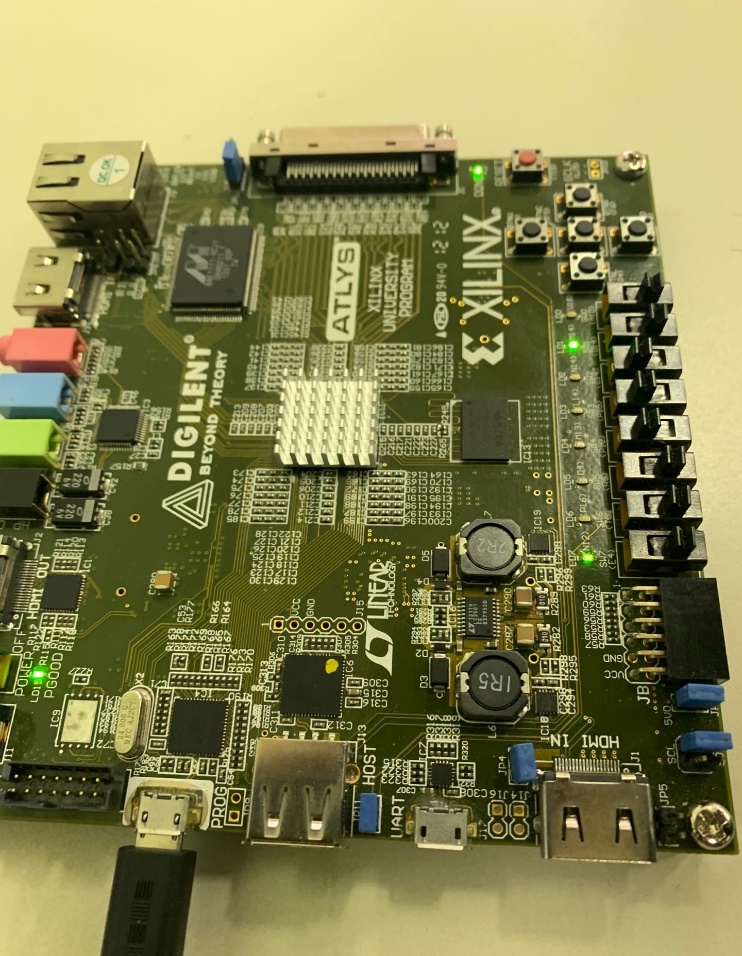

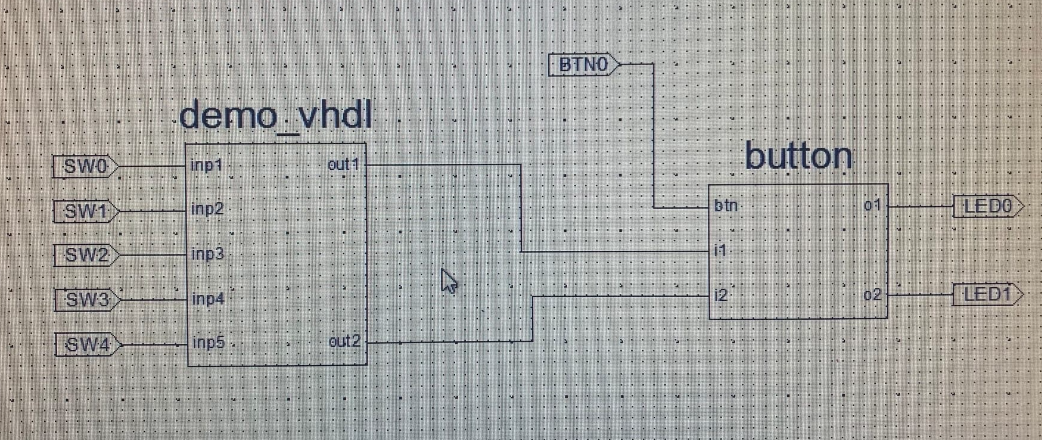

схема, представленный на рисунке

1

Рис. 1. Готовая схема цифрового устройства

Посмотрев работу цифрового устройства в режиме симуляции, окно симулятора iSim можно закрыть и перейти к следующему этапу проектирования.

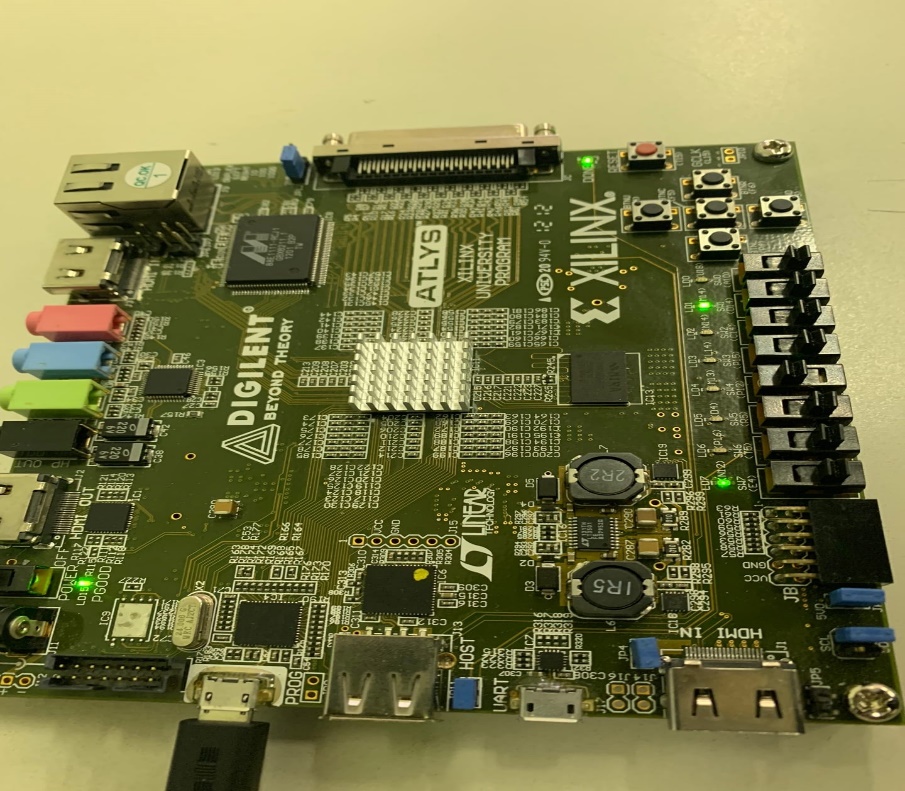

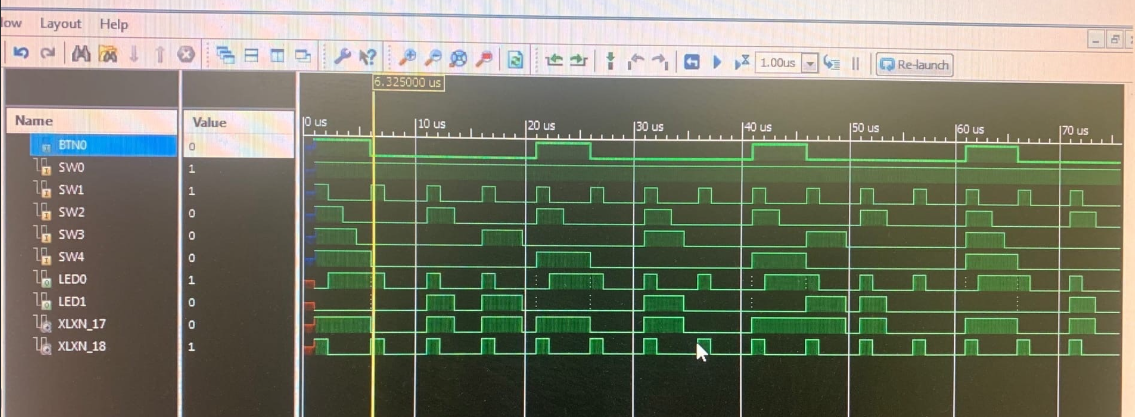

Рис.

2. Симуляция проекта

Рис.

2. Симуляция проекта

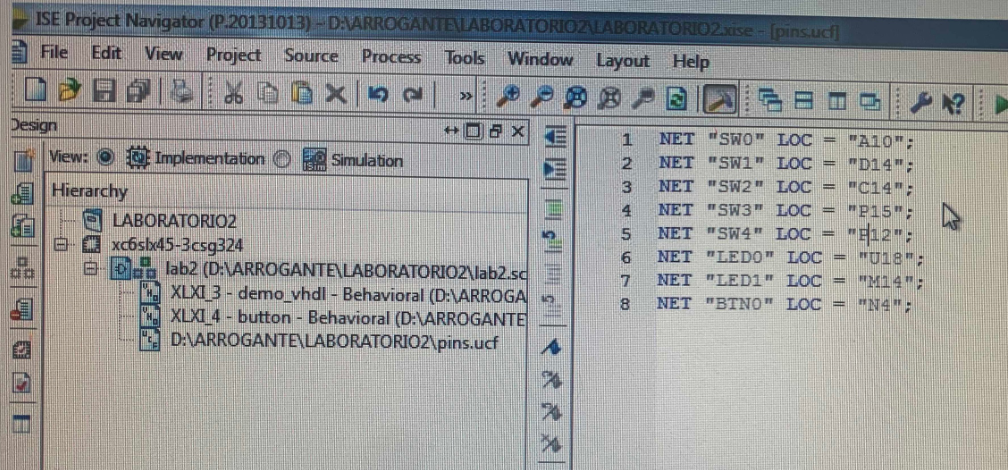

Синтаксис связывания имеет следующий вид: NET "Имя_Маркера" LOC = "Вывод_на_плате";

Соответственно, описание всех связей маркеров будет выглядеть так:

Рис. 3. Создание связи с выводами отладочной платы

Результаты представлено на рисунок 4

|

|

|

|

|

|