L_R_2

.docxМинистерство цифрового развития, связи и массовых коммуникаций Российской Федерации

Ордена Трудового Красного Знамени федеральное государственное бюджетное образовательное учреждение высшего образования

МОСКОВСКИЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ СВЯЗИ И ИНФОРМАТИКИ

(МТУСИ)

Факультет "Радио и телевидение"

Кафедра "Радиотехнические системы"

Лабораторная работа № 2

по дисциплине микропроцессорные устройства

Выполнил студент гр. БРМ1902:

Обама Х.С.

Бонсэн Й.Ф.

Проверил Д.Н.Шубин

Цель работы

Целью работы является изучение системы автоматизированного проекти-рования (САПР) Xilinx ISE WebPack, ознакомление с основами языка VHDL и реализация на ПЛИС логической схемы комбинационного типа с использо-ванием функционала графического редактора и модулей на языке описания аппаратуры VHDL.

Вариант для создания устройства demo_vhdl

№ вар. |

Входы |

Выходы |

||||||||||

inp1 |

inp2 |

inp3 |

inp4 |

inp5 |

out1 |

out2 |

out3 |

|||||

7 |

ИЛИ-НЕ |

И |

НЕ |

+ |

+ |

+ |

||||||

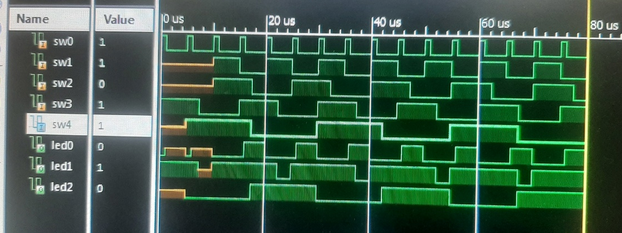

Вариант установки значений переменных , мкс

№ вар. |

BTN0 |

SW1 |

SW2 |

SW3 |

SW4 |

||||||||

DC |

T |

STO |

T |

STO |

T |

STO |

T |

STO |

T |

||||

7 |

20 |

5 |

10 |

10 |

10 |

15 |

0 |

20 |

5 |

25 |

|||

Обозначения:

DC – Duty Cycle (рабочий цикл);

T – Period (период);

STO – Starting Time Offset (смещения времени начала).

Для всех переключателей Cancel after Time Offset (отмена после смещения времени) – 100мкс

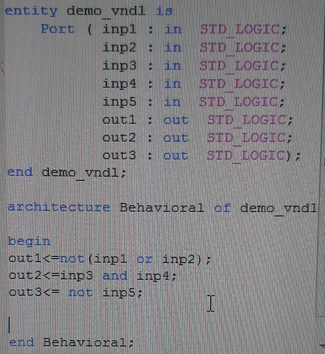

Рисунок 1 - Шаблон VHDL модуля

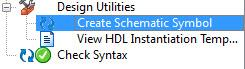

Рисунок 2 – Создание схематического символа

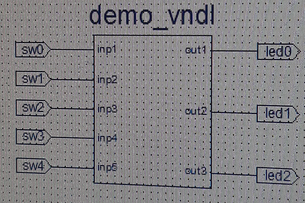

Рисунок 3 - VHDL модуль в виде символа

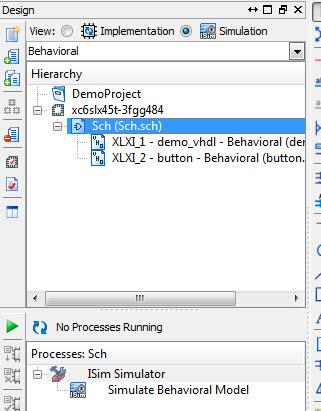

Рисунок 4 – Запуск процесса симуляции

Рисунок 5 - Главное окно симулятора iSim

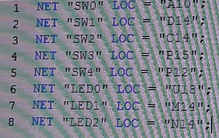

Создание связи с выводами отладочной платы

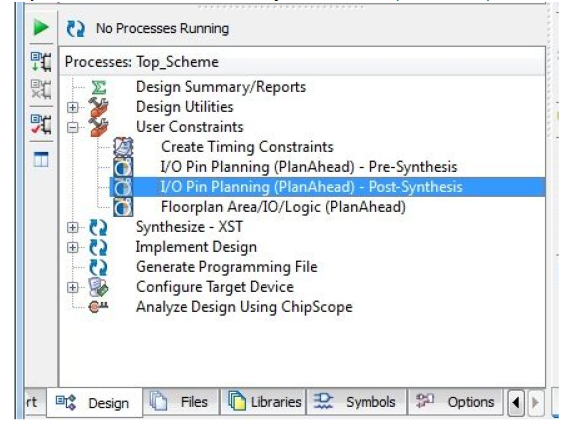

Рисунок 6 - Процесс для создания Implementation Constraints File

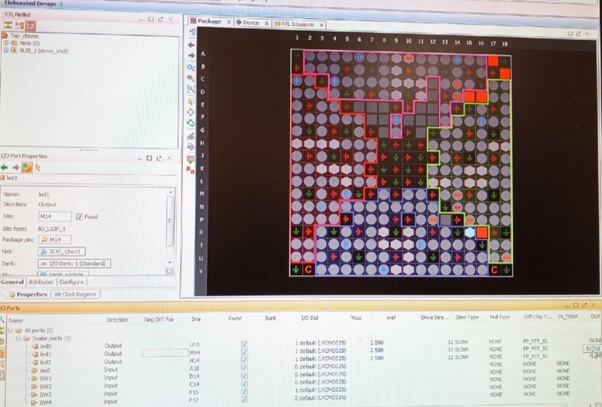

Рисунок 7 - Главное окно программы Plan Ahead

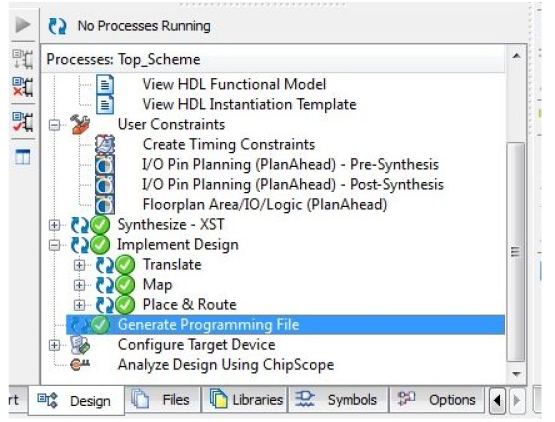

Создание конфигурационного файла

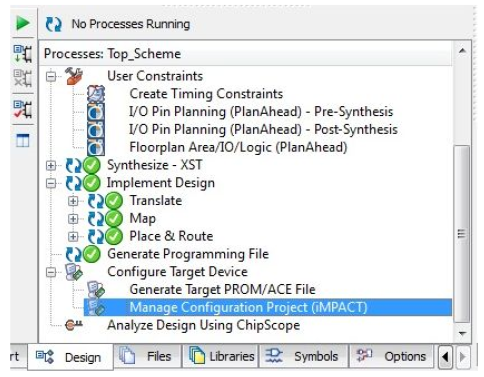

Рисунок 8 - Успешное создание конфигурационного файла

Конфигурирование отладочной платы

Рисунок 9 - Запуск программы iMPACT

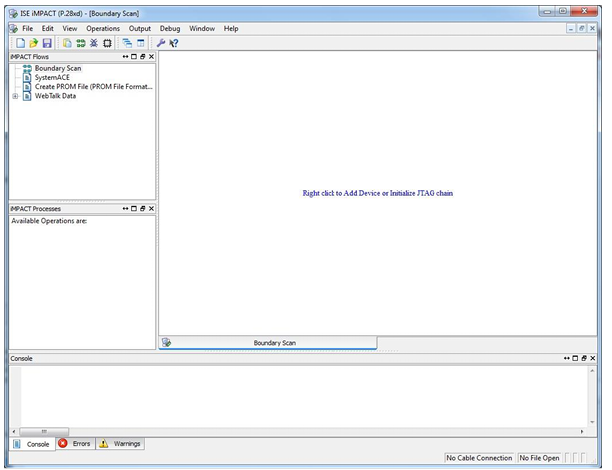

Рисунок 10 - Главное окно программы iMPACT

Рисунок 11 - Implementation Constraints File

Рисунок 12 - Привязанный конфигурационный файл

Рисунок 13 - Оповещение об успешном конфигурировании

Рисунок 14 - Светодиод DONE

Проверка работы платы

out1<= not (inp1 or inp2)

out2<= inp3 and inp4

out3<= not inp5

Выводы по работе

В ходе выполнения лабораторной работы мы изучили систему автоматизированного проектирования (САПР) Xilinx ISE WebPack, ознакомились с основами языка VHDL и реализацией на ПЛИС логической схемы комбинационного типа с использованием функционала графического редактора и модулей на языке описания аппаратуры VHDL.

Москва 2022