Лаба 2

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра Безопасности жизнедеятельности

отчет

по лабораторной работе №2

по дисциплине «Проектирование проблемно ориентированных вычислительных устройств»

Тема: Представление комбинационных схем и простых триггерных

устройств

Студенты гр. |

|

|

|

|

|

Преподаватель |

|

Буренева О.И. |

Санкт-Петербург

2022

Цель работы.

Выполнить модификацию и осуществить моделирование комбинационной схемы на основе различных способов задания логической функции, а также исследовать использование комбинационной схемы в сочетании с запоминающим элементом.

Задание на лабораторную работу

Вариант 0: функция 10000010

Задание на лабораторную работу

1. Создать в системе QuestaSim новый проект, включив в него файл Lab2.v. Изменить текст программы Lab2.v так, чтобы реализовать одну из функций таблицы. Сигнал clock при выполнении п.п. 1 – 7 не используется, и соответствующие присваивания закомментированы.

2. Выполнить компиляцию проекта.

3. Запустить процедуру моделирования, вызвав опцию Simulate системы моделирования. Открыть окна наблюдения Source, Process, Signals, Wave.

4. Выполнить моделирование в автоматическом режиме. Просмотреть временную диаграмму, убедиться в правильности реализации логической функции. Сохранить программу в новом файле.

5. Модифицировать программу так, чтобы функция вычислялась на основе разложения Шеннона по одной или двум переменным. Выполнить п.п. 2 и 4.

6. Выполнить описание той же логической функции с использованием оператора case или UDP (по заданию преподавателя). Выполнить п.п. 2 и 4.

8. Вызвать в окно редактора программу, сохраненную в п. 4. Раскомментировать присваивания сигналу clock. Отметим, что в представленном в образце варианте единичное состояние сигнала clock «охватывает» момент изменения сигналов x_0 – x_2.

9. Добавить сигнал и оператор, описывающие триггер типа D со статическим управлением, на информационный вход которого поступает выход комбинационной схемы. Выполнить п.п. 2 и 4.

10. Скорректировать программу так, чтобы реализовался триггер с динамическим управлением. Выполнить п.п. 2 и 4. Сравнить результаты по п.п. 9 и 10.

11. Описать схему, задерживающую сигнал с выхода комбинационной схемы еще на один такт. Для этого добавить описание дополнительного триггера с динамическим управлением и тем же сигналом синхронизации clock, а информационный вход соединить с выходом «первого» триггера. Для корректного описания такой синхронной задержки присваивания должны быть неблокирующими. Выполнить п.п. 2 и 4. А что если здесь использовать блокирующие присваивания?

12. Выполнить компиляцию и моделирование на схемотехническом уровне одного из вариантов описания комбинационной схемы. Для этого воспользоваться синтезирующей САПР Quartus II в соответствии с рекомендациями Приложения 2 данного пособия.

При выполнении этого этапа требуется коррекция программы:

– изменить заголовок программы, определив входы и выходы модуля, объявить режимы портов и типы данных, передаваемых через них;

– исключить оператор initial, тестовые воздействия будут формироваться в отдельном файле.

Выполнив компиляцию, изучить RTL-представление и физическую реализацию (Schematic view) устройства. Оценить затраты и быстродействие схемы.

Содержание этого пункта может изменяться в зависимости от используемого в практикуме оборудования.

13. Выполнить загрузку проекта, созданного по п.12, в реальную микросхему средствами синтезирующей САПР.

При переходе к практической имплементации триггерных схем рекомендуется:

– заменить блок генерации исходных данных таким фрагментом:

always @ ( posedge clock)

begin

if(reset) takt=0;

else (takt!=9) takt=takt+1;

else takt=0;

x_0= takt[0];

x_1= takt[1];

x_2= takt[2];

end

– понизить частоту генератора тактового сигнала для удобства наблюдения работы схемы с помощью осциллографа (Приложение 3).

Вывести на внешние контакты макетной платы сигналы clock и выходные сигналы проекта, вход Reset подключить к механическому переключателю, на вход синхронизации осциллографа подать выход старшего разряда счетчика. Наблюдать работу схемы.

Выполнение работы

Текст первой программы представлен в листинге 1.

module lab2;

parameter truth_table=8'b01000001;

wire error;

reg x_0, x_1, x_2, z, clock;

reg [3:0] takt;

initial begin

clock='b0;

x_0='b0;

x_1='b0;

x_2 ='b0;

$monitor("takt = %d, %b %b1 %b1", takt, x_0, x_1, x_2);

for (takt=0;takt!=8;takt=takt+1)

begin

#20 // clock=?b1;

#5 x_0= takt[0];

x_1= takt[1];

x_2= takt[2];

// #5 clock=?b0 ;

end

$finish;

end

assign

error = (z == truth_table[{x_2, x_1, x_0}])? 0:1;

always @(x_0,x_1,x_2)

begin

z = (~x_2 && ~x_1 && ~x_0) || (x_2 && x_1 && ~x_0);

end

endmodule

Листинг 1. Код программы с расчетом функции

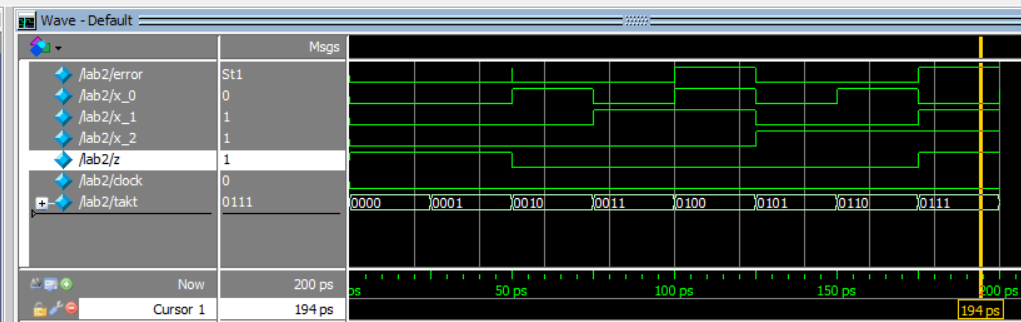

Временная диаграмма представлена на рис.1

Рисунок 1. Временная диаграмма

Код программы с использованием разложения Шеннона представлен в листинге 2.

module lab2;

parameter truth_table=8'b01000001;

wire error;

reg x_0, x_1, x_2, z, clock;

reg [3:0] takt;

initial begin

clock='b0;

x_0='b0;

x_1='b0;

x_2 ='b0;

$monitor("takt = %d, %b %b1 %b1", takt, x_0, x_1, x_2);

for (takt=0;takt!=8;takt=takt+1)

begin

#20 // clock=?b1;

#5 x_0= takt[0];

x_1= takt[1];

x_2= takt[2];

// #5 clock=?b0 ;

end

$finish;

end

assign

error = (z == truth_table[{x_2, x_1, x_0}])? 0:1;

always @(x_0,x_1,x_2)

begin

if (~x_0)

z = ~x_1 && ~x_2 || x_1 && x_2;

else

z = 0;

end

endmodule

Листинг 2. Код программы с использованием разложения Шеннона

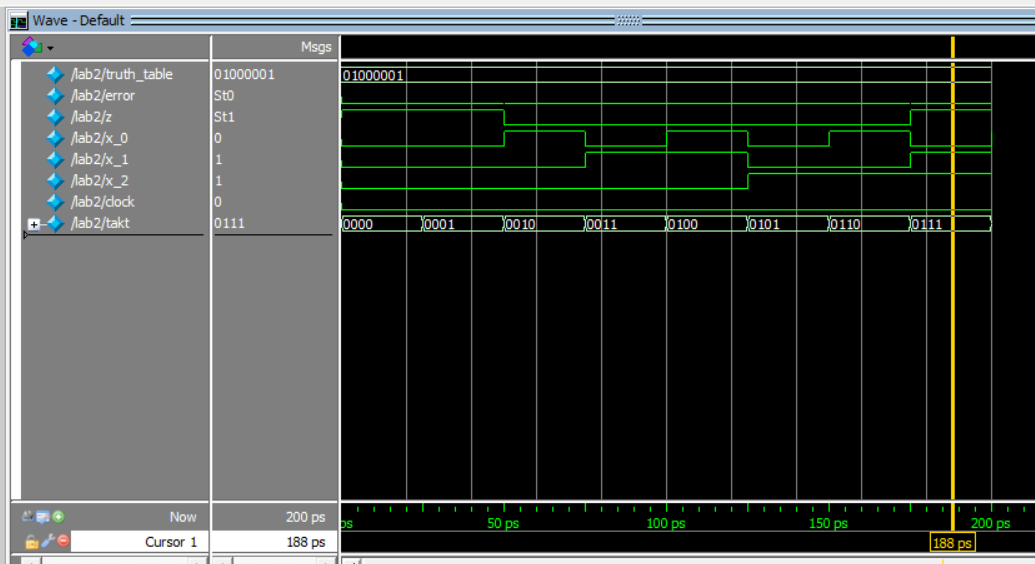

Временная диаграмма представлена на рис.2

Рисунок 2. Временная диаграмма

Код программы с использованием UDP представлен в листинге 3.

module lab2;

parameter truth_table=8'b01000001;

wire error;

wire z;

reg x_0, x_1, x_2, clock;

reg [3:0] takt;

my_logic my_logic_init(z, x_2, x_1, x_0);

initial begin

clock='b0;

x_0='b0;

x_1='b0;

x_2 ='b0;

$monitor("takt = %d, %b %b %b, %b", takt, x_2, x_1, x_0, z);

for (takt=0;takt!=8;takt=takt+1)

begin

#20 // clock=?b1;

#5 x_0= takt[0];

x_1= takt[1];

x_2= takt[2];

// #5 clock=?b0 ;

end

$finish;

end

assign

error = (z == truth_table[{x_2, x_1, x_0}])? 0:1;

endmodule

primitive my_logic(zt,a,b,c);

output zt;

input a,b,c;

table

// a, b, c : zt;

0 0 0 : 1;

0 0 1 : 0;

0 1 0 : 0;

0 1 1 : 0;

1 0 0 : 0;

1 0 1 : 0;

1 1 0 : 1;

1 1 1 : 0;

endtable

endprimitive

Листинг 3. Код программы с UPD

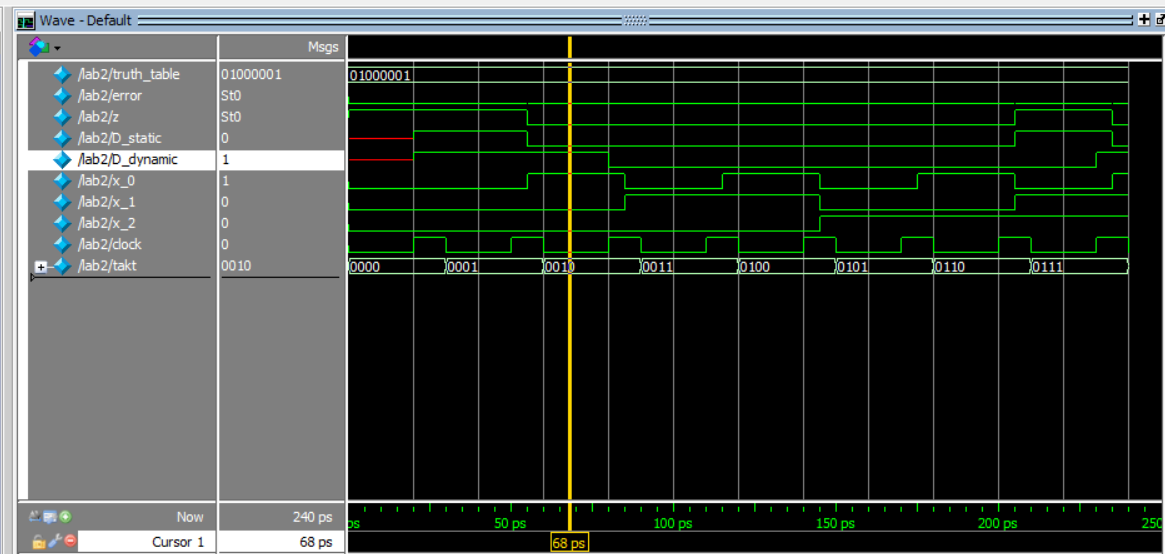

Временная диаграмма представлена на рис.3

Рисунок 3. Временная диаграмма

Код программы с реализацией триггера со статическим управлением

представлен в листинге 4.

module lab2;

parameter truth_table=8'b01000001;

wire error;

wire z;

reg D;

reg x_0, x_1, x_2, clock;

reg [3:0] takt;

my_logic my_logic_init(z, x_2, x_1, x_0);

initial begin

clock='b0;

x_0='b0;

x_1='b0;

x_2 ='b0;

$monitor("takt = %d, %b %b %b, %b", takt, x_2, x_1, x_0, z);

for (takt=0;takt!=8;takt=takt+1)

begin

#20 clock='b1;

#5 x_0= takt[0];

x_1= takt[1];

x_2= takt[2];

#5 clock='b0 ;

end

$finish;

end

assign

error = (z == truth_table[{x_2, x_1, x_0}])? 0:1;

always @(clock, z)

if (clock) D = z;

endmodule

Листинг 4. Код программы со статическим триггером.

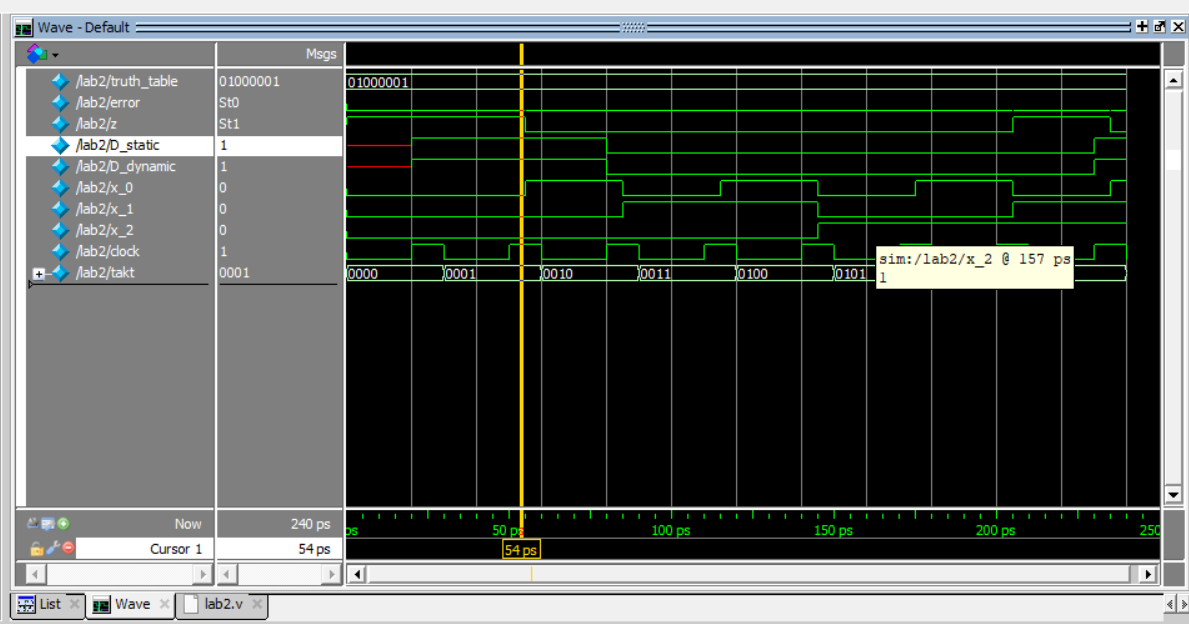

Временная диаграмма представлена на рис.4

Рисунок 4. Временная диаграмма

Для реализации динамического триггера изменить список чувствительности оператора always и использовать неблокирующее присваивание.

Код программы, реализующей динамический и статический триггеры, представлен в листинге 5.

module lab2;

parameter truth_table=8'b01000001;

wire error;

wire z;

reg D_static;

reg D_dynamic;

reg x_0, x_1, x_2, clock;

reg [3:0] takt;

my_logic init(z, x_2, x_1, x_0);

initial begin

clock='b0;

x_0='b0;

x_1='b0;

x_2 ='b0;

$monitor("takt = %d, %b %b %b, %b", takt, x_2, x_1, x_0, z);

for (takt=0;takt!=8;takt=takt+1)

begin

#20 clock='b1;

#5 x_0= takt[0];

x_1= takt[1];

x_2= takt[2];

#5 clock='b0 ;

end

$finish;

end

assign

error = (z == truth_table[{x_2, x_1, x_0}])? 0:1;

always @(clock, z)

if (clock) D_static = z;

always @(posedge clock)

D_dynamic <= z;

Endmodule

Листинг 5. Код программы с двумя триггерами.

У динамического триггера выход сигнала меняется только по фронту синхросигнала clock, что дает отставание на один такт. Временная диаграмма представлена на рис.5

Рисунок 5. Временная диаграмма

Чтобы увеличить задержку на еще один такт добавим дополнительный динамический триггер к выходу первого триггера. Код программы представлен в листинге 6.

module lab2;

parameter truth_table=8'b01000001;

wire error;

wire z;

reg D_static;

reg D_dynamic;

reg x_0, x_1, x_2, clock;

reg [3:0] takt;

my_logic init(z, x_2, x_1, x_0);

initial begin

clock='b0;

x_0='b0;

x_1='b0;

x_2 ='b0;

$monitor("takt = %d, %b %b %b, %b", takt, x_2, x_1, x_0, z);

for (takt=0;takt!=8;takt=takt+1)

begin

#20 clock='b1;

#5 x_0= takt[0];

x_1= takt[1];

x_2= takt[2];

#5 clock='b0 ;

end

$finish;

end

assign

error = (z == truth_table[{x_2, x_1, x_0}])? 0:1;

always @(posedge clock)

D_static <= z;

always @(posedge clock)

D_dynamic <= D_static;

Endmodule

Листинг 6. Код программы с двумя динамическими триггерами

Временная диаграмма представлена на рис. 6

Рисунок 6. Временная диаграмма

Если заменить неблокирующие присваивания на блокирующие, то они будут выполняться не параллельно, а последовательно. Таким образом второй триггер не будет отставать на такт от первого триггера. Результат моделирования представлен на рисунке 7.

Рисунок 7. Моделирование с блокирующими присваиваниями

Реализация для компиляции и моделирования

module lab2(x, z);

input x;

output z;

wire [2:0] x;

wire z;

assign z = (~x[2] & ~x[1] & ~x[0]) | (x[2] & x[1] & ~x[0]);

endmodule

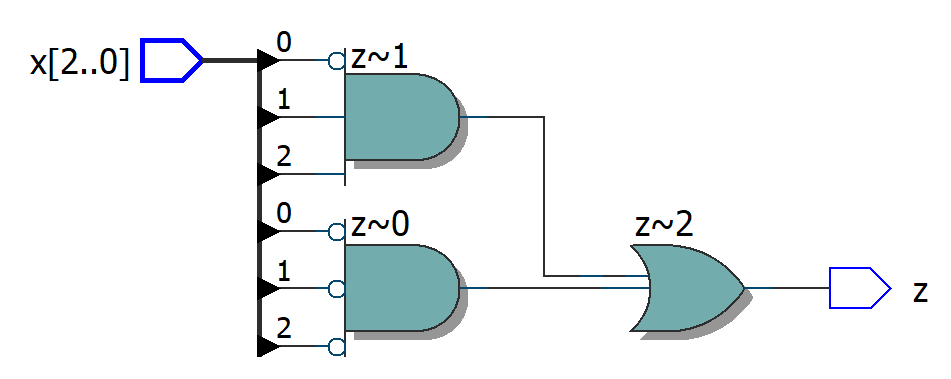

RTL получившейся модели

Вывод

В ходе выполнения лабораторной работы был изучен процесс реализации

логических комбинационных схем и триггеров при проектировании

устройства на языке Verilog.