Лаба 4

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра Вычислительной техники

отчет

по лабораторной работе №4

по дисциплине «Проектирование проблемно ориентированных вычислительных устройств»

Тема: Описание цифровых автоматов

Студенты гр. |

|

|

|

|

|

Преподаватель |

|

Буренева О.И. |

Санкт-Петербург

2022

Цель работы.

Разработать описание автомата и программу для тестирования автомата, включающую исследуемый автомат и генератор тестирующих воздействий, на базе синтаксиса языка VerilogHDL.

Вариант задания

Таблица 1. Вариант задания

Enc_4 : S0→2'b00, S1→2'b01, S2→2'b10,

2’b00→2'b00, x1→2'b01, x2→2'b10, x3→2'b11,

y0→'b0, y1→'b1.

Задание на лабораторную работу

1. Создать в системе моделирования новый проект, на основании трафарета, содержащегося в файле st_mash.v, создать Verilog-описание автомата соответствии заданием, которое выдается преподавателем как один из вариантов таблицы 4.3 или 4.4. Кроме варианта таблиц переходов преподаватель задает форму описания - однопроцессную или многопроцессную. На первом этапе использовать явное кодирование состояний, входов и выходов.

2. Разработать программу для тестирования автомата, включающую исследуемый автомат и генератор тестирующих воздействий и включить ее в проект. В качестве образца целесообразно использовать файл Test_lab4.v. Выполнить компиляцию проекта.

3. Запустить процесс моделирования с опцией полной видимости объектов используя пункты меню Simulate→Design optimisation→Visibility→Apply full visibility, там же в закладке Design units задать вершину проекта и поле Output design name – имя опримизированной версии (произвольно). Отметить Start immediately и нажать OK. Выполнить пошаговое моделирование на интервале первых четырех периодов синхронизации. Фиксировать вызовы операторов и пояснять их исполнение.

4. Выполнить моделирование проекта в автоматическом режиме и наблюдать временную диаграмму работы. Подтвердить правильность функционирования проекта.

5. Преобразовать описание автомата так, чтобы использовались символьные представления состояний и некоторых входных комбинаций. Наименование состояний должно задаваться в программе тестирования и соответствовать опции ENC в заданном варианте.

Выполнить пп. 3 – 5. Убедится в возможности использования символических имен данных Verilog.

Выполнение работы

Проанализируем автомат, заданный вариантом задания. Переходы и

выходы автомата представлены в таблице 2.

Состояние Вход |

S0 |

S1 |

S2 |

x0 |

S0/y0 |

S1/y1 |

S2/y1 |

x1 |

S1/y1 |

S2/y1 |

S0/y0 |

x2 |

S0/y0 |

S0/y0 |

S1/y1 |

x3 |

S2/y1 |

S1/y1 |

S0/y0 |

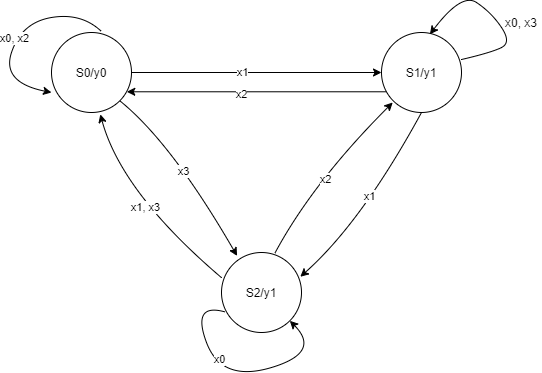

Диаграмма состояний представлена на рисунке 1.

Рисунок 1. Диаграмма состояний

Код для устройства, реализующий автомат с явным кодированием состояний, представлен в листинге 1

module st_mash(in, out, reset, clock);

parameter state_size=2;

parameter in_size=2;

parameter out_size=1;

input in;

output out;

input reset, clock;

wire [in_size-1:0] in;

reg [out_size-1:0] out;

reg [state_size-1:0] current;

reg [state_size-1:0] next;

always @(in, current)

begin

case (current)

2'b00:

case (in)

//смотрим по состояниям автомата

2'b00:next=2'b00;

2'b01:next=2'b01;

2'b10:next=2'b00;

2'b11:next=2'b10;

default:next=2'b00;

endcase

2'b01:

case (in)

2'b00:next=2'b01;

2'b01:next=2'b10;

2'b10:next=2'b00;

2'b11:next=2'b01;

default:next=2'b01;

endcase

2'b10:

case (in)

2'b00:next=2'b10;

2'b01:next=2'b00;

2'b10:next=2'b01;

2'b11:next=2'b00;

default:next=2'b10;

endcase

default:next=2'b00;

endcase

end

always @(current)

case(current)

2'b00:out='b0;

2'b01:out='b1;

2'b10:out='b1;

default:out='b0;

endcase

always @(posedge clock or posedge reset)

begin

if (reset == 1) current = s0;

else current = next;

end

// current=next;

//always @(posedge reset)

// current=s0;

endmodule

Программа для тестирования с генератором тестирующих воздействий

представлена в листинге 2

module Test_lab4;

reg [1:0] in_data;

reg reset,clock;

reg [2:0] takt;

wire [0:0] out_data;

st_mash moodle(in_data,out_data,reset,clock);

initial

begin

clock='b0;

reset='b0;

#5 reset='b1;

#10 reset='b0;

#5

for (takt=0; takt<=7;takt=takt+1)

begin

case(takt)

0:in_data=2'b01; //1

1:in_data=2'b11; //1

2:in_data=2'b01; //1

3:in_data=2'b00; //1

4:in_data=2'b10; //1

5:in_data=2'b10; //0

6:in_data=2'b11; //1

7:in_data=2'b11; //0

//Таким образом, полностью обходится автомат

endcase

#5 clock='b1;

#10 clock='b0;

#20;

end

end

endmodule

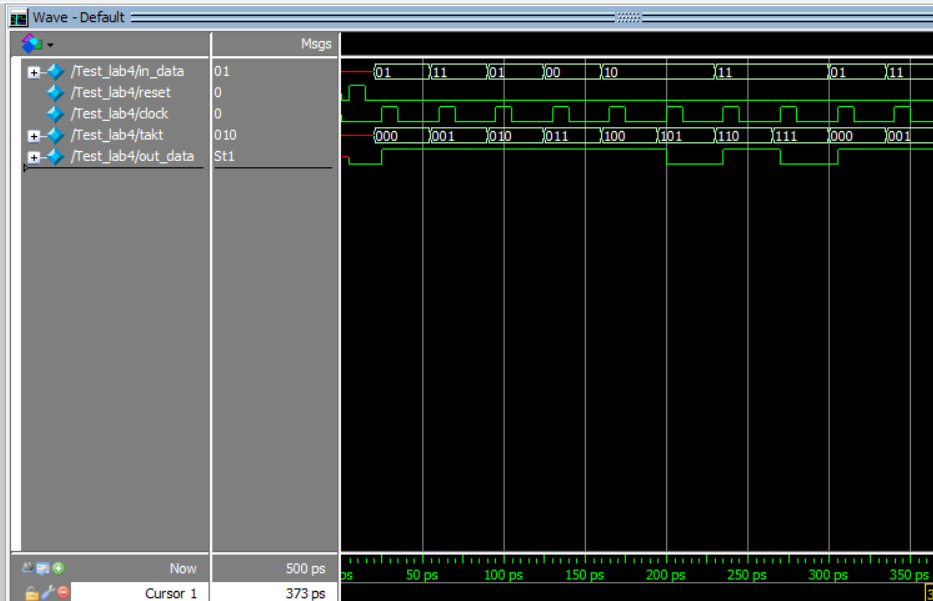

Временная диаграмма работы устройства представлена на рисунке 2

Рисунок 2. Временная диаграмма работы автомата

Временная диаграмма показывает, что переключения автомата

соответствуют заданию.

Код для устройства, реализующего автомат с символьным кодированием

состояний, представлен в листинге 3.

module st_mash_sym(in, out, reset, clock);

parameter state_size=2;

parameter in_size=2;

parameter out_size=1;

input in;

output out;

input reset, clock;

wire [in_size-1:0]

x0 = 2'b00,

x1 = 2'b01,

x2 = 2'b10,

x3 = 2'b11;

reg [out_size-1:0]

y0 = 'b0,

y1 = 'b1;

parameter [state_size-1:0]

s0=2'b00,

s1=2'b01,

s2=2'b10;

wire [in_size-1:0] in;

reg [out_size-1:0] out;

reg [state_size-1:0] current;

reg [state_size-1:0] next;

always @(in, current)

begin

case (current)

s0:

case (in)

//смотрим по состояниям автомата

x0:next=s0;

x1:next=s1;

x2:next=s0;

x3:next=s2;

default:next=s0;

endcase

s1:

case (in)

x0:next=s1;

x1:next=s2;

x2:next=s0;

x3:next=s1;

default:next=s1;

endcase

s2:

case (in)

x0:next=s2;

x1:next=s0;

x2:next=s1;

x3:next=s0;

default:next=s2;

endcase

default:next=s0;

endcase

end

always @(current)

case(current)

s0:out=y0;

s1:out=y1;

s2:out=y1;

default:out=y0;

endcase

always @(posedge clock)

current=next;

always @(posedge reset)

current=s0;

endmodule

Программа для тестирования с генератором тестирующих воздействий

представлена в листинге 4.

module Test_lab4_sym;

parameter [1:0]

x0=2'b00,

x1=2'b01,

x2=2'b10,

x3=2'b11;

parameter [1:0]

s0=2'b00,

s1=2'b01,

s2=2'b10;

parameter [0:0]

y0='b0,

y1='b1;

reg [1:0] in_data;

reg reset,clock;

reg [2:0] takt;

wire [0:0] out_data;

st_mash_sym moodle(in_data,out_data,reset,clock);

initial

begin

clock=y0;

reset=y0;

#5 reset=y1;

#10 reset=y0;

#5

for (takt=0; takt<=7;takt=takt+1)

begin

case(takt)

0:in_data=x1; //1

1:in_data=x3; //1

2:in_data=x1; //1

3:in_data=x0; //1

4:in_data=x2; //1

5:in_data=x2; //0

6:in_data=x3; //1

7:in_data=x3; //0

//Таким образом, полностью обходится автомат

endcase

#5 clock=y1;

#10 clock=y0;

#20;

end

end

endmodule

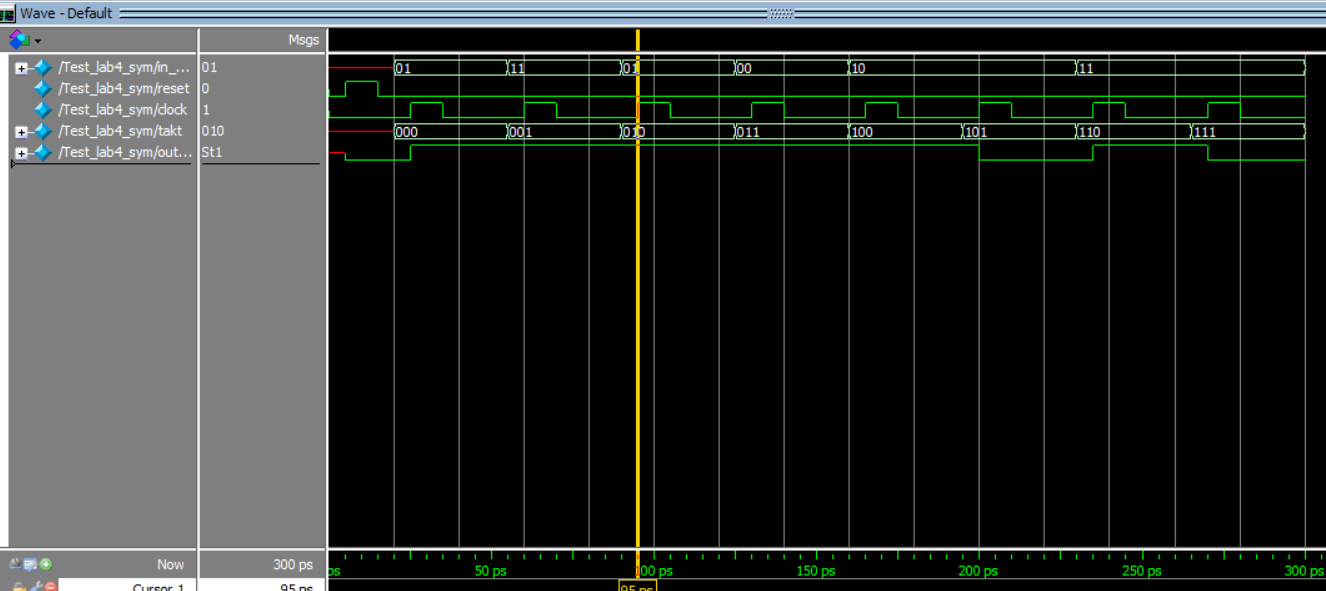

Временная диаграмма работы устройства представлена на рисунке 3

Рисунок 3. Временная диаграмма работы автомата

Диаграммы совпали, символьные имена работают корректно.

Вывод

В ходе выполнения лабораторной работы был изучен процесс разработки

устройства, реализующего логику автомата, и программы для его

тестирования на языке Verilog.

Вопросы к отчету:

В чем отличие описания автоматов Мили и Мура? Что нужно добавить или убрать, чтобы получить автомат Мили?

Сколько процессов в этой программе? (столько же, сколько и блоков always)

Как уменьшить их количество? (Совместить блоки по общим условиям в switch-case конструкции; в листинге 1 оставлена пасхалка)