1 курс 1 семестр / лекции / Лекция 1 ЦП система команд

.pdf

3.2. Программа и ее прерывания.

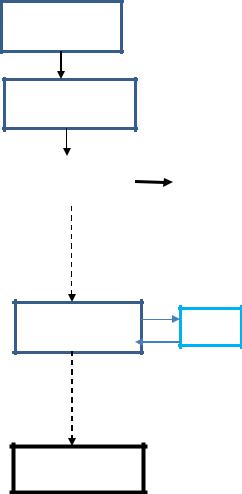

Код программы это - последовательность выполнения инструкций, которая может нарушаться внутренними или внешними причинами, рис.1: -внутренние причины- исключения или особые ситуации при выполнении инструкций (деление на ноль);

-внешние причины аппаратные прерывания —

вызовы процедур под воздействием электрических сигналов на специальные выводы процессора;

-программные прерывания, не нарушают последовательность инструкций, предписанную программистом. Поэтому прерываниями они по сути не являются — это всего лишь особый способ вызова системных сервисов BIOS и операционной системы;

-сигнал аппаратного сброса или инициализации процессора - начало функционирование компьютера.

начало

Инструкция 1

Инструкция 2 |

|

стоп |

|

|

|

Инструкция N

печать

Конец

Рис.1

3.3. Адресация и порядок исполнения инструкций. |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

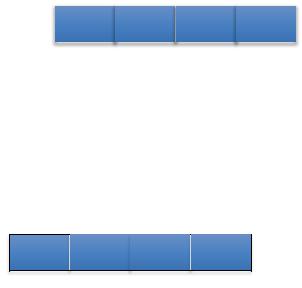

Адрес текущей исполняемой инструкции хранится |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

Инстр. 1 |

|

|

|

|

|

Счетчик |

|

|||||||||

в специальном регистре – указателе инструкций, |

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

команд |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

подсчет которого ведет счетчик команд. |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

Инстр. 2 |

|

|

|

|

|

|

|

||||||||

После исполнения линейной инструкции счетчик |

|

|

|

|

|

|

|

|

|

|

|||||||||

команд увеличивает свое значение на ее длину, т.е. |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

укажет на начало следующей инструкции. |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

Инстр. 3 |

|

|

|

|

|

|

||||||||

Кроме |

линейных |

инструкций |

существуют |

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

инструкции |

передачи |

управления, |

которые |

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

Инстр. 4 |

|

|

|

Процедура |

|

||||||||||

разделяются на |

инструкции переходов и |

вызовов |

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

процедур. |

|

|

|

|

|

|

|

Условие ? |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

Инстр. 5 |

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Инструкции переходов могут быть безусловными и |

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

условными, |

а |

инструкции вызова |

процедур |

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

Инстр. 6 |

|

|

|

|

|

||||||||||

характерны тем, что процессор сохраняет в памяти |

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

следующую инструкцию, на которую должно быть |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

Инстр. 7 |

|

|

|

|

|

||||||||||

передано |

|

управления, |

после |

исполнения |

|

|

|

|

|

|

|

|

|

||||||

процедуры.

Условный переход (вызов) зависит от состояния флагов (признаков) на момент исполнения данной инструкции.

Если переход (вызов) не состоится, то

исполняется инструкция, расположенная в памяти вслед за текущей.

1.4. Структурная схема процессора.

В составе имеются 3 основных блока:

-операционный блок,

обеспечивающий вычисление с сохранением их результатов;

-блок управления,

обеспечивающий команды и их исполнение;

-интерфейсный блок ,

обеспечивающий связь процессора с различными устройствами ЭВМ или компьютера.

Рис.3.1. Схема процессора

По числу и способу использования регистров операционного блока различают следующие типы П:

аккумуляторные, много аккумуляторные и стековые.

Процессоры с одним регистром результата иногда называют П с аккумуляторной архитектурой или просто аккумуляторными. Их отличительной характеристикой является относительная простота аппаратной реализации операционного и управляющего блоков, а также упрощенный формат команд.

В большинстве современных П специальные регистры результата не используются, а их функции может выполнять любой регистр блока Регистра Общего Назначения (РОН) или ячейка памяти. Такую архитектуру называют

много аккумуляторной.

П со специальной оперативной памятью называется стековым П. Различают два типа организации стековой памяти в зависимости от правила доступа: очередь и стек. Правила доступа определяется применительно к входным (записываемым) и выходным (читаемым) последовательностям слов. Существует два типа правил доступа: FIFO (First-In-First-Out — первый поступивший

удаляется первым) и LIFO (Last-In-First-Out — последний поступивший извлекается первым) .

4. Система команд.

4.1. Общие сведения.

В понятие «система команд» входят: форматы команд и обрабатываемых данных; список команд, их функциональное назначение; способы адресации данных.

Команды Процессора (П) подразделяются на следующие функциональные группы:

-пересылки данных и ввода-вывода; -арифметических и логических операций; -передачи управления.

4.2. Структура команд. Команда П в общем случае содержит операционную и адресные

части. |

|

|

|

|

|

|

|

|

|

n |

k d |

|

|

|

|

f |

|

|

|

|

|

|

|

|

|

n-k бит информации; |

|

КОП – код операций |

|

А1 |

|

А2 |

А3 |

А4 |

|

|

|

|

d-f бит информации. |

|||||

|

|

|

|

|

|

|

|

|

|

Операционная часть |

|

|

Адресная часть |

|

|||

Адресная часть команды может иметь четыре адресных поля А1, А2, А3, А4.

Они кодируют адреса операндов исполнения (Al, А2), адрес результата (АЗ) и адрес следующей команды (А4)

А1  А2

А2  А3

А3  А4

А4

В зависимости от указываемого числа адресов команды подразделяются на безадресные, 1-, 2-, 3- и 4-адресные.

Почти во всех П исключен адрес А4 .

Использование адреса результата АЗ в адресном поле команды во многих случаях также оказывается избыточным. Это обосновывается тем, что результат арифметических и логических операций над двумя операндами обычно может быть помещен на место одного из операндов, который в дальнейшем, скорее всего, использоваться не будет.

При переходе к 2-адресным командам в их адресное поле необходимо вводить дополнительные разряды, кодирующие назначение адресуемых операндов: кто из них является источником, а кто — приемником информации.

Группа безадресных команд, в которых осуществляется безадресное (неявное) задание операнда. К безадресным командам относятся команды управления процессором, например, пуска, останова. Безадресными также являются команды, реализующие операции со стеком. В стековых операциях операнд, адресуемый указателем стека SP, неявно задается кодом команды.

4.2. Способы адресации операндов и команд.

Способ прямой адресации.

Все адреса, содержащиеся в адресном поле, полностью определяют адрес операнда в памяти. Прямая адресация неэкономична с точки зрения затрачиваемых разрядов для адресации.

Обозначения:

АК – командный адрес - адрес, указанный в команде; АИ – исполнительный адрес - адрес к которому происходит обращение. При прямой адресации АК=АИ

Процессор |

Память |

АК

АИ

Все операции с регистровыми операндами реализуются Операционным Блоком без обращения к Оперативной Памяти, команды с регистровыми операндами выполняются быстрее других типов команд.

Неявная адресация — способ адресации, при котором адресное поле в команде отсутствует, а адрес операнда

подразумевается кодом операции.

n |

|

k |

Ак = КОП |

|

|

|

КОП – код операций |

|

|

|

|

|

|

|

КОП соответствует адрес определенного операнда (откуда берутся или куда заносятся данные)

Неявно адресуются отдельные регистры процессора, например, аккумулятор,

индексный и базисный, указатель стека.

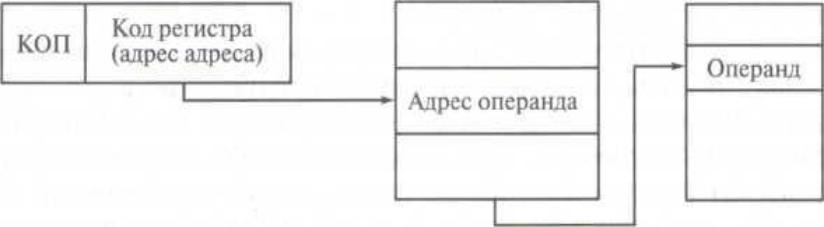

Косвенная адресация —адрес, указываемый в команде, которая является указателем ячейки регистра, а ячейка регистра содержит исполнительный адрес операнда в памяти. Фактически при косвенной адресации в команде указывается адрес адреса. Для обозначения косвенной адресации используется запись Ак = (Ак)

Процессор |

РОН |

Оперативная память |

Адрес регистра намного короче полного адреса операнда памяти

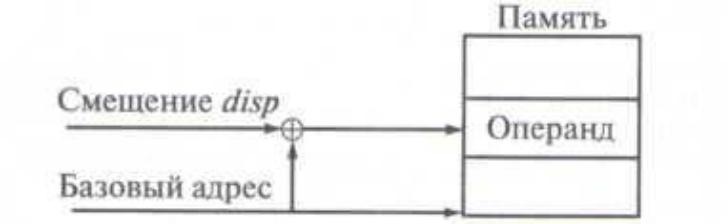

Развитием метода косвенной адресации является относительная адресация, или базирование. Вычисление исполнительного адреса Аи операнда в памяти в виде суммы базового значения адреса и «смещения» указываемого в команде.

Аи

Формирование исполнительного адреса Аи при относительной адресации.

Вычисление исполнительного адреса Аи связано с потерей времени, при определении Аи, поэтому операцию суммирования заменяют операцией конкатенации (приписывания разрядов).

При конкатенации базовый адрес содержит старшие разряды, а смещение — младшие разряды адреса Аи.

При изменении базовых адресов блоков содержимое этих блоков не меняется и блоки можно свободно перемещать в пределах всего адресного пространства памяти.