1 курс 1 семестр / лекции / Лекция 3 Инструкц ариф лог перех

.pdfЛекция 3. Инструкции программирования.

Вопросы:

1.Логические инструкции.

2.Арифметические инструкции.

3.Инструкции перехода.

Литература:

1. Цифровая схемотехника и архитектура компьютера. Дэвид М. Харрис и Сара Л. Харрис, 2009г , с. 776-786

1.Логические инструкции.

1.1.Инструкции типа R

Логические операции AND, OR, и NOR.

Соответствующие им одноименные инструкции типа R производят побитовые операции над значениями двух регистров-источников и помещают результат в регистр-назначение.

Код на языке ассемблера:

and $s3, $s2, $s1 or $s3, $s2, $s1 xor $s3, $s2, $s1

Регистр назначения rd

Анализ результата:

1. Инструкция and обеспечивает перемножение бит и полезна для наложения маски (англ. masking) на биты, т.е. для обнуления ненужных битов. Операция 0xFFFF0000 AND 0x46A1F0B7 = 0x46A10000. Инструкция and маскирует два младших байта и помещает два старших незамаскированных байта со значением 0x46A1 из регистра $s2 в регистр $s3.

2. Инструкция or обеспечивает логическое сложение битов хорошо использовать для объединения битов из двух регистров. Например, в результате операции 0x347A0000 OR 0x000072FC = 0x347A72FC получаем комбинацию двух значений .

3. Инструкция xor выполнение следующих действий:

1 xor1=0; 1 xor 0=1; 0 xor1=1; 0 xor0=0 при объединении разных значениях 2-х бит -1, а при одинаковых значениях – 0. Позволяет в результате операции инвертировать старшие байты и оставить неизменным младшие байты, т.е. 0x347A0000 ХOR 0x000072FC = 0xF85E72FC

4. В архитектуре MIPS не определена операция инвертирования битов NOT. Инструкцию NOR можно использовать в качестве замены (инструкция NOR сначала делает операцию OR с исходными значениями, затем побитно инвертирует результат этой операции).

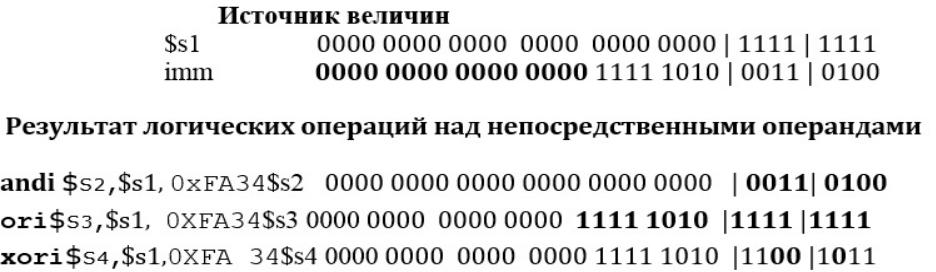

1.2. Инструкции типа I.

Логические инструкции также могут работать с непосредственными операндами. Это инструкции типа I, как andi, ori и xori. Инструкция nori не определена

потому, что редко нужна и легко может быть заменена уже имеющимися инструкциями. Поскольку эти инструкции работают с 32-битным значением регистра и 16-битной константой, то сначала они дополняют константу до 32 бит

нулями.

Анализ результата:

1. При выполнении инструкции andi младший байт регистра получает значение младшего байта добавляемой константы 0011 0100

2. При выполнении инструкции ori изменения получили два байта

регистра $s1 1111 1010 |1111 |11112

3. При выполнении инструкции xori изменения получили только

три бита в двух младших байтах 1100 |10112

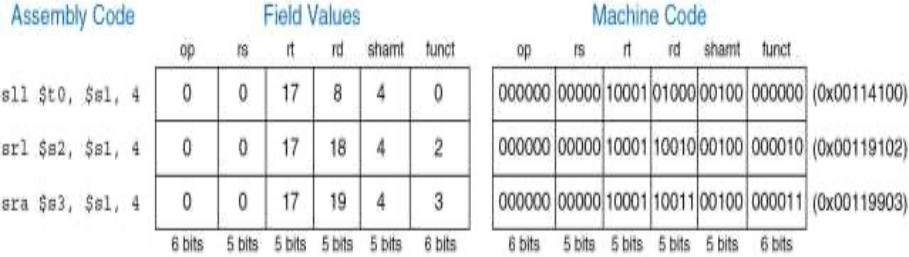

1.3. Инструкции сдвига.

Инструкции сдвига сдвигают значение в регистре влево или вправо на любое заданное количество бит, вплоть до 31. Операции сдвига фактически умножают или делят сдвигаемые значения на степени двойки. Сдвиг значения влево на М битов эквивалентен умножению на 2М . Сдвиг вправо на М битов – делению на 2М.

В архитектуре MIPS существуют следующие инструкции сдвига: sll (логический сдвиг влево, англ.: shift left logical);

srl (логический сдвиг вправо, англ.: shift right logical);

sra (арифметический сдвиг вправо, англ.: shift right arithmetic).

Cдвиги влево всегда заполняют освобождающиеся младшие биты нулями. Вместе с тем, сдвиги вправо могут быть как логическими (в освобождающиеся старшие биты заполняются нули), так и арифметическими (освобождающиеся старшие биты заполняются значением знакового бита- единицами).

Машинные коды инструкций сдвига типа R.

В адресе поля rt (регистра $s1) хранится число, значение которого нужно сдвигать, поле shamt задаёт величину сдвига (4d - 00100 b). Результат сдвига помещается в регистр $t0 по адресу поля rd Числа в адресах полей инструкций rt, rd.

Значение числа в регистре $s1:

$s1 1111 0011 0000 0000 0000 0010 1010 1000

Результат выполнения инструкций:

1. Логический сдвиг влево, значение регистра $t0 $t0 0011 0000 0000 0000 0010 1010 1000 0000

2.Логический сдвиг вправо, значение регистра $s2 $s2 0000 1111 0011 0000 0000 0000 0010 1010

3.Арифметический сдвиг вправо, значение регистра $s3

$s3 1111 1111 0011 0000 0000 0000 0010 1010

Арифметические инструкции.

Умножение и деление отличаются от других арифметических операций. Умножение двух 32-битных чисел даёт 64-битное произведение. Деление двух 32-битных чисел даёт 32-битное частное и 32-битный остаток.

В архитектуре MIPS определено два регистра специального

назначения hi и lo, в которые сохраняются результаты

умножения и деления.

Инструкция mult $s0, $s1 умножает значения из регистров $s0 и $s1. Старшие 32 бита произведения помещаются в регистр hi, а младшие - в регистр lo.

Аналогично, инструкция div $s0, $s1 вычисляет значение $s0/$s1. Частное помещается в lo, а остаток - в hi.

В архитектуре MIPS есть и другая команда умножения, которая помещает 32-битный результат в регистры общего назначения. Инструкция mul $s1, $s2, $s3 умножает значения из $s2 и $s3 и сохраняет 32-битный результат в $s1, где размещаются адреса регистров РОН1 и РОН2, что соответствует регистрам hi и lo.

3. Инструкции перехода.

Инструкции переходов могут быть условного и безусловного типа.

Инструкции условных переходов, также называемые инструкциями ветвления (англ.: branch),проверяют какое-либо условие и осуществляют переход только в том случае, если проверка дает ИСТИНУ.

Инструкции безусловного перехода (англ.: jump) осуществляют переход всегда.

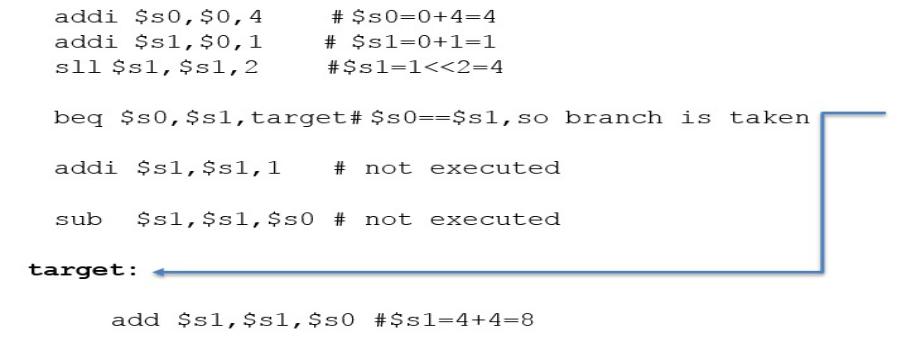

Система команд MIPS содержит две основные инструкции условного перехода: ветвление при равенстве (beq, от англ. branch if equal) и ветвление при неравенстве (bne, от англ. branch if not equal).

Инструкция beq осуществляет переход, когда содержимое двух регистров равно, а bne осуществляет переход, если оно не равно.

001 сдвиг влево на 2 бита получим 100

Пример использование инструкции кода beq:

при сдвиге влево на 2 бита получаем равенство двух регистров $s1= $s0 – условие target выполнено!

Следующей выполненной инструкцией будет инструкция add, располагающаяся сразу за меткой с именем target. Две инструкции, расположенные между инструкцией ветвления и меткой, не выполняются.