1 курс 1 семестр / лекции / Лекция_7_Микроархитектура_процессор —_копия

.pdf

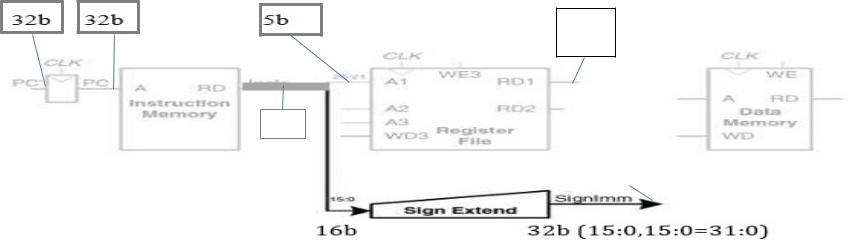

2.3. Исполнение команды, требующей смещение.

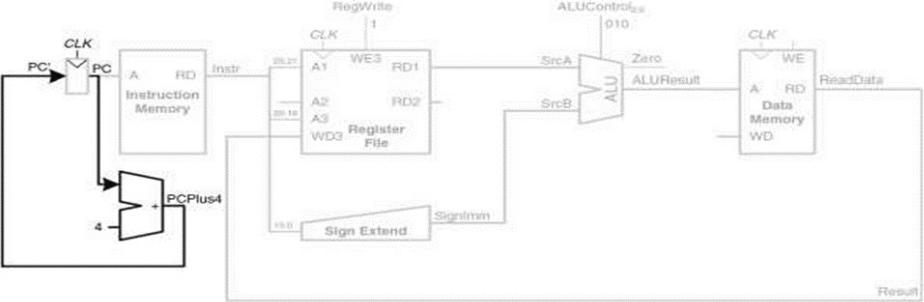

Команда: Lw $a0, 4($0) # загрузка в $ a0 по адресу (смещение)4 относительно базового адреса $0. Эта команда – чтение из памяти и загрузка в RF требует следующие операции: 1. Чтение команды из RF по порту RD. 2. Определение 32 битного адреса для памяти DM и его вычисление по смещению. 3. Чтение данных из памяти DM по вычисленному адресу А из порта RD. 4 Запись из памяти DM в RF по порту WD3.

SrcА 32 b

Instr 25:21

32b

|

SrcB |

Расширение знака |

32 b |

|

Исполнение команды со смещением:

Команде Lw требуется смещение (offset) – число (в примере 4), которое будет прибавлено к базовому адресу нулевого регистра $0. Смещение передается как непосредственный операнд (immediate), то есть находится непосредственно в поле Inctr (15:0), занимая младшие 16 бит. Так как 16-битное число может быть как положительным, так и отрицательным, то над ним должна быть выполнена операция знакового расширения до 32 бит. Данная команда Lw должна вычислить адрес,

затем по этому адресу прочитать слово в памяти данных DM, а затем вернуть это слово (записать его) в регистровом файле RF по адресу А3 через порт WD3.

Инструкция Lw $a0, 4($0) – это инструкция I- типа, которая имеет следующий вид:

31 |

26 25 |

21 20 |

16 15 |

0 |

Вполе rt содержится адрес $a0, который определяет куда его поместить в RF.

Вполе imm содержится значение числа 4,который используется для определения

адреса памяти в DM.

В поле rs содержится адрес базового регистра, который также используется для определения адреса памяти в DM.

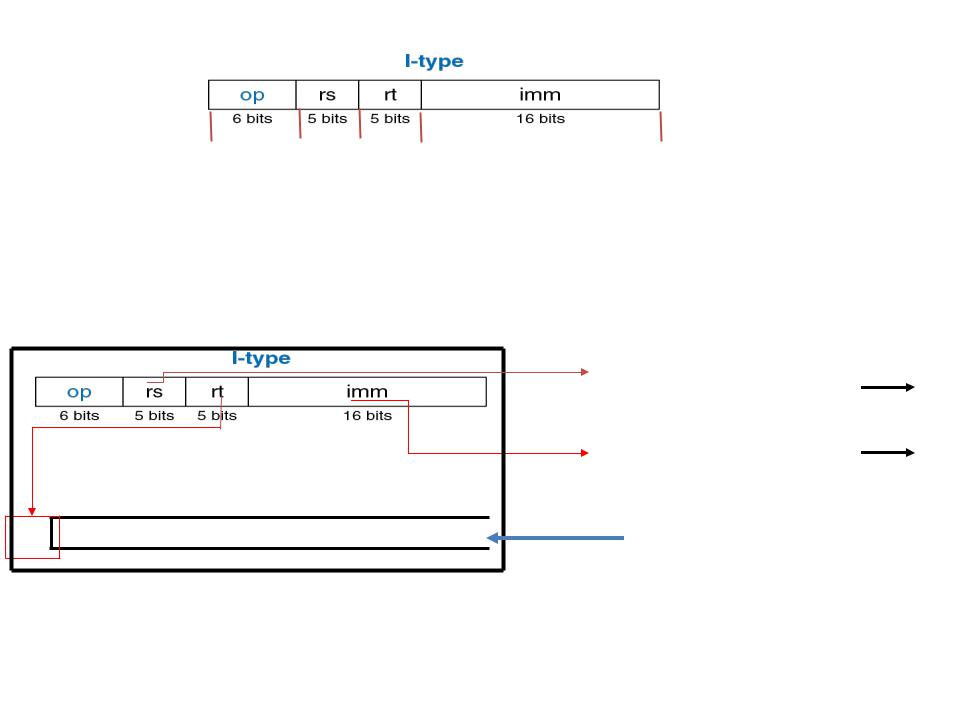

Тогда обработка команды в RF имеет следующий вид:

Адрес

А3

|

адрес |

Значение адреса регистра $0 |

Src A |

|||

$0 |

|

0х00000000 |

|

|||

|

|

32b |

||||

|

|

Значение числа 4 с расширением |

||||

|

|

Src B |

||||

|

|

|

|

|

|

|

RF |

|

0х 0000 |

0004 |

|

||

|

|

32 b |

||||

|

|

|

|

|||

|

|

|

|

|

||

$a0 |

|

|

|

|

|

|

|

|

DM |

|

|

||

|

|

|

|

|

|

|

Src A - значение первого числа для определения адреса регистра памяти в DM. Src B - значение второго числа для определения адреса регистра памяти в DM. Адрес А3 регистра $a3 определяется адресом его размещения в RF и находится в

поле rt исполняемой команды.

2.3.1. Определение адреса чтения слова в DM за счет суммирования 2-х адресов команды.

5b |

|

32b |

|

|

|

32b

32b

16b |

32b |

Расширение

знака

1.АЛУ получает на входы два операнда по 32 бита каждый: SrcА и SrсB

2.Суммированием управляет Трех битный управляющий сигнал ALUControl:

ALUControl=000, на выходе 32-битный 0; ALUControl=111 на выходе 32-битная 1;

ALUControl=010 на выходе из АЛУ 32-битный суммарный результат ALUResult.

3. 32 – битный сигнал ALUResult подается на адресный вход А памяти данных DM, который определяет адрес регистра в DM, где находится искомое слово – слово прочитано в порту RD, как только значение адреса появится в А памяти DM.

2.3.2. Определение адреса записи данных в RF и их запись из памяти DM.

32b

32b

5b 32b

Регистр результата, в который команда Lw запишет прочитанное из памяти DM значение выхода (RD), определяется 5 битовым полем rt (Instr 20:16) этой же команды Lw, которое подключено к 5 битовому адресному входу А3 третьего порта (WD3) файла регистров RF. Управляющий сигнал RegWrite=1, в свою очередь, соединен со входом разрешения записи порта (WE3) RF и активен во время выполнения команды запись.

Запись происходит по положительному значеннию тактового сигнала СLK, которым заканчивается такт процессора исполнения команды Lw.

2.3.3. Формирование нового адреса счетчика команд РС.

Формирование нового адреса PC’ происходит в сумматоре PCPlus4 с появлением нового тактового импульса, который обеспечивает постоянное суммирование числа 4 (адресация по словам) со старым адресом РС:

PC’ = PC+4

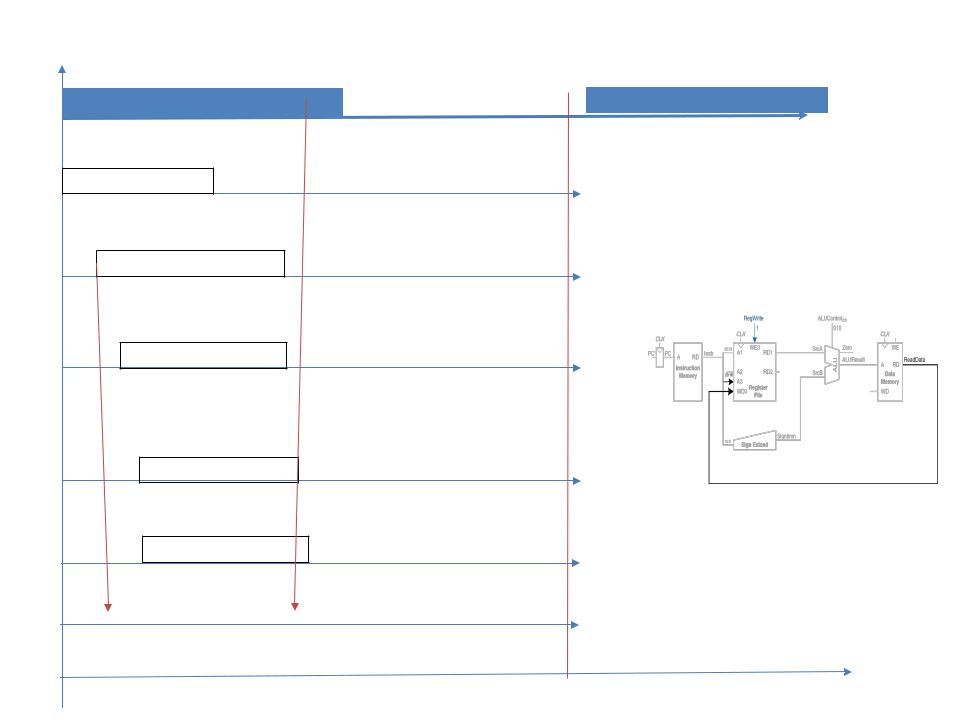

Временная диаграмма исполнения команды Lw $a0, 4($0).

CLK синхроимпульсы |

|

|

|

|

|

Тактовый импульс |

пауза |

|

Тактовый импульс |

|

|

|

T- период тактового сигнала |

|

PC = A1 адрес команды |

|

|||

|

|

|

||

Стадия выборки адреса

tнс

RF = команда Lw $a0, 4($0)

Стадия расшифровка команды |

tнс |

|

RF = формирование адреса чтения в DM

Формирование SrcA и SrcB |

tнс |

|

ALU = вычисление адреса для DM

SrcA + SrcB вычисление А |

tнс |

|

DM = чтение данных по адресу А, WE=0

Стадия чтение по адресу А

RF = запись данных по адресу А3 в порт WD3, WE3=1 tнс

|

Определение А3 |

|

Запись данных |

|

tнс |

||

|

|

|

|

|

|||

PC = PC’ адрес новой команды |

|||||||

|

|

|

|||||

|

Новый А |

Стадия выборки адреса |

|||||

|

|

|

|

|

|

|

|

tнс

tнс

T- период тактового сигнала