1 курс 1 семестр / 10.03.01_1_семестр / 10.03.01_1_семестр / ПЗ_4_Исследование_работы_АЛУ

.pdf

Практическое занятие № 4. Исследование работы арифметикологического устройства

Цель и содержание

Синтезировать схему арифметико-логического устройства и исследовать его работу.

Содержание работы: 1 Теоретическая часть

2Задание

3Контрольные вопросы

1 Теоретическая часть

Арифметико-логическое устройство (АЛУ, Arithmetic/Logical Unit (ALU) объединяет различные арифметические и логические операции в одном узле. Например, типичное АЛУ может выполнять сложение, вычитание, сравнение величин, операции «И» и «ИЛИ». АЛУ входит в ядро большинства компьютерных систем.

На рис. 4.1 показано условное обозначение N-разрядного АЛУ с N- разрядными входами и выходами. В АЛУ поступает управляющий сигнал F, который определяет, какую функцию нужно выполнить.

Иногда можно встретить обозначение сигналов управления голубым цветом. Это делается, чтобы отличать их от сигналов данных.

A B

N

N  N

N

АЛУ 3 F

N

N

Y

Рис. 4.1 – Условное обозначение арифметико-логического устройства

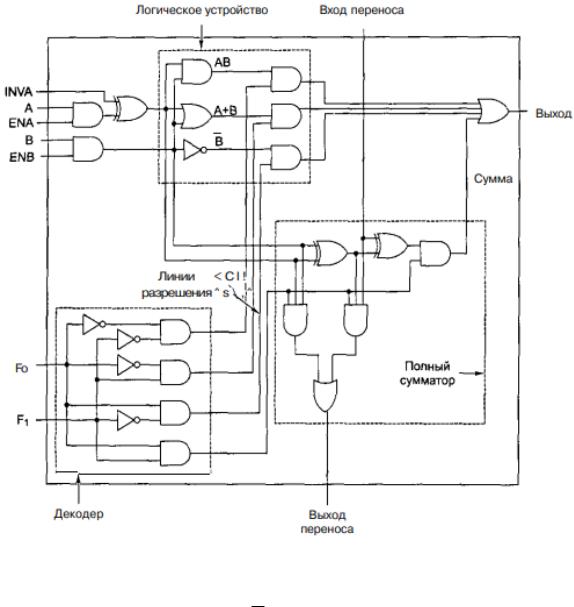

На рис. 4.2 изображена схема АЛУ. Представленное устройство может вычислять одну из 4 следующих функций:

-А И В;

-А ИЛИ В;

-Β ;

-А+В.

Выбор функции зависит от того, какие сигналы поступают на линии F0 и F1: 00,01,10 или 11 (в двоичной системе счисления). Обратите внимание, что здесь А+В означает арифметическую сумму А и В, а не логическую операцию И.

В левом нижнем углу схемы находится двухразрядный декодер, который порождает сигналы включения для четырех операций. Выбор операции определяется сигналами управления F0 и F1. В зависимости от значений F0 и F1 выбирается одна из четырех линий разрешения, и тогда выходной сигнал выбранной функции проходит через последний вентиль ИЛИ.

Рис. 4.2 – Одноразрядное АЛУ

В верхнем левом углу схемы находится логическое устройство для

вычисления А И В, А ИЛИ В и Β , но по крайней мере один из этих результатов проходит через последний вентиль ИЛИ в зависимости от того, какую из разрешающих линий выбрал декодер. Так как ровно один из выходных сигналов декодера будет равен 1, то и запускаться будет ровно один из четырех вентилей И. Остальные три вентиля будут выдавать 0 независимо от значений А и В. АЛУ может выполнять не только логические и арифметические операции над А и В, но и делать их равными нулю, отрицая ENA (сигнал разрешения А) или ENB (сигнал разрешения В).

При нормальных условиях и ENA, и ENB равны 1, чтобы разрешить поступление обоих входных сигналов, а сигнал INVA равен 0. В этом случае

Аи В просто поступают в логическое устройство без изменений.

Внижнем правом углу находится полный сумматор для подсчета суммы А и В и для осуществления переносов. Переносы необходимы, поскольку несколько таких схем могут быть соединены для выполнения операций над целыми словами.

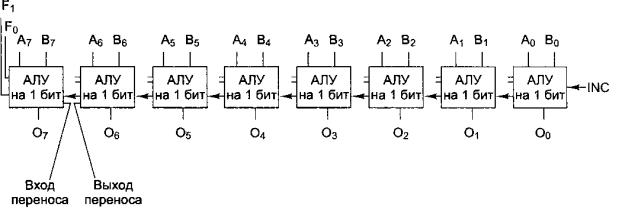

Одноразрядные схемы, подобные той, которая изображена на рис. 4.2, называются разрядными микропроцессорными секциями. Они позволяют разработчику сконструировать АЛУ любой желаемой ширины. На рис. 4.3 показана схема 8-разрядного АЛУ, составленного из восьми одноразрядных секций. Сигнал INC (увеличение на единицу) нужен только для операций сложения. Он дает возможность вычислять такие суммы, как А+1 и А+В+1.

Рис. 4.3 – Восемь одноразрядных секций, соединенных в 8-разрядное АЛУ (сигналы разрешения и инверсии не показаны для упрощения схемы)

Задание

Спроектировать в программе Quartus схему одноразрядного арифметико-логического устройства, представленного на рисунке 4.2. Входящий в состав данной схемы полный сумматор можно не создавать заново, а использовать уже созданный элемент (практическое занятие № 2). Для этого зайдите в меню Project и выберите команду Add/Remove Files in Project… В появившемся окне найдите нужный файл и добавьте его командой Add.

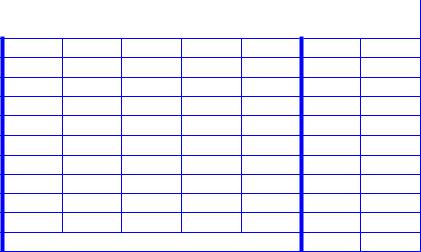

После создания схемы проведите ее симуляцию и отразите в отчете следующую таблицу истинности. (ENA, ENB и INVA по умолчанию будем считать соответственно равными 1, 1 и 0).

|

Входные значения |

|

|

Выходы |

|||

|

|

|

|

|

|

|

|

A |

B |

Cin |

F0 |

F1 |

|

S |

Сout |

Прочие

Контрольные вопросы

1.Что такое АЛУ?

2.Каким образом на АЛУ поступают управляющие сигналы? Как работает декодер?

3.Что такое микропроцессорные секции? Как они соединяются между

собой?

4.Каким образом в программе Quartus II можно создать n-разрядное

АЛУ?

5.Какое максимальное число, с которым можно производить операции

в32-битном АЛУ?

Содержание отчета

1Название, цель работы

2Задание (таблица истинности АЛУ)

3Письменные ответы на контрольные вопросы