3856

.pdfДля получения правильного результата фильтрации необходимо предусмотреть деление на 4096. Уравнение фильтрации будет выглядеть следующим образом:

y/4096 (C0 *16)(x0 *256) (С1 *16)(x1 *256)(С2 *16)(x2 *256) (C3 *16)(x3 *256)

На рис. 4.54 показана имитационная модель КИХфильтра на 4 отвода с перегружаемыми коэффициентами с использованием блока FIR Compiler v5.0, а на рис. 4.55 результаты имитационного моделирования.

Рассмотрим разработку имитационной модели систолического КИХ-фильтра (тип фильтра - Single-Rate FIR) с использованием блока FIR Compiler v6.3 являющимся аналогом функции FIR Compiler v6.3 САПР Xilinx ISE

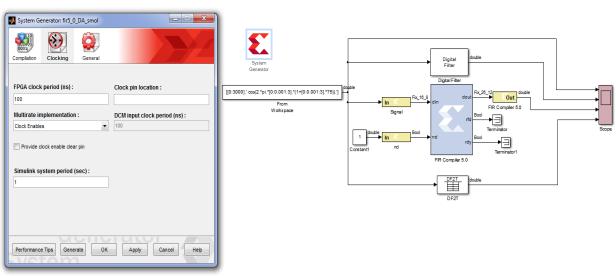

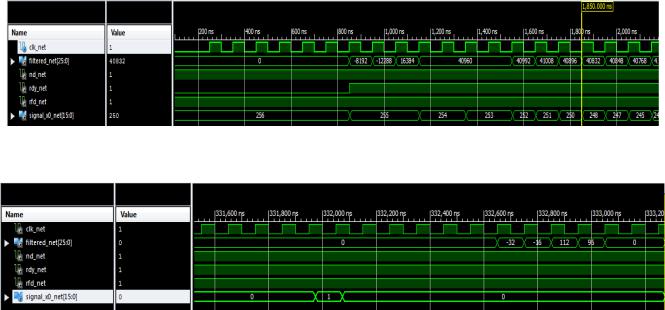

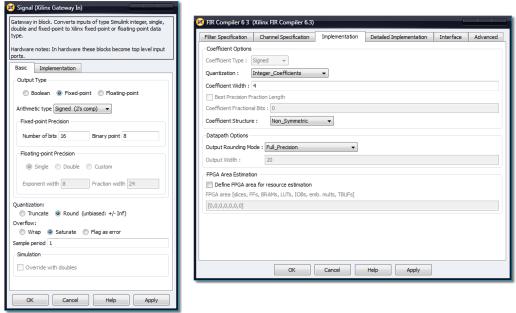

получаемой с помощью генератора параметризированных ядер XLogiCORE IP (рис. 4.56). На рис. 4.57 показан формат представления входного сигнала и закладка “реализация” блока FIR Compiler 6.3. Входной сигнал представляется в формате FIX_16_8 а коэффициенты фильтра в формате FIX_4_0. Профильтрованный сигнал представляется с 20битной точностью. На рис. 4.58 показано имитационное моделирование.

С помощью блока System Generator создадим в автоматическом режиме проект фильтра и испытательный стенд. На рис. 4.59 показано функциональное моделирование с использованием моделирующей программы сгенерированной в автоматическом режиме (период синхросигнала 100 нс).

271

272

Рис. 4.49. (а) Задание частоты тактирования системы (фильтра) в САПР ISE (100 ns) и периода симуляции в Simulink (1 с); б) - модель КИХ-фильтра на четыре отвода с использованием блока

FIR Compiler v5.0

272

273

Рис. 4.50. Настройки блока FIR Compiler 5.0: а) – закладка спецификация фильтра; б) – закладка реализация фильтра. Коэффициенты фильтра несимметричные, со знаком, квантованные, представлены в формате FIX_8_4

273

274

Рис. 4.51. Имитационное моделирование в системе Matlab/Simulink КИХ-фильтра на четыре отвода созданного с помощью блоков Digital Filter, FIR Compiler 5.0 и DF2T

274

275

Рис. 4.52. Входной сигнал умножается на масштабный множитель 256, коэффициенты фильтра на 16. Период синхросигнала 100 нс

Рис. 4.53. Импульсная характеристика фильтра. Коэффициенты умножаются на 16

275

276

Рис. 4.54. Модель КИХ-фильтра на 4 отвода с перегружаемыми коэффициентами с использованием блока FIR Compiler v5.0

276

277

Рис. 4.55. При достижении 2500 отсчета происходит загрузка вектора значений коэффициентов

[1 1 1 1] вместо [-2 -1 7 6]

277

278

Рис. 4.56. Систолический КИХ-фильтр на четыре отвода с использованием блока FIR Compiler v6.3

278

279

а) б)

Рис. 4.57. Настройки блоков: а) – входной сигнал представляется в формате FIX_16_8; б) – закладка реализация, коэффициенты фильтра целые, со знаком, представлены в формате

FIX_4_0

279

280

Рис. 4.58. Имитационное моделирование фильтра на четыре отвода созданного с помощью блока FIR Compiler 6.3

Рис. 4.59. Функциональное моделирование с использованием моделирующей программы на языке VHDL сгенерированной в автоматическом режиме. Входной сигнал умножается на 256, а коэффициенты фильтра не масштабируются

280