3222

.pdf

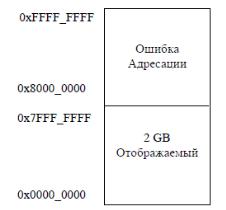

Рис. 1.5. Размещение виртуального адресного пространства режима User

Сегмент пользователя начинается с адреса 0x0000_0000 и заканчивается адресом 0x7FFF_FFFF. Обращения по всем остальным адресам вызывают прерывания по ошибке адресации.

Процессор находится в режиме User, если в регистре StatusCP0 установлены следующие значения разрядов:UM=1; EXL=0; ERL=0.

В табл. 1.3 приводятся характеристики сегмента useg режима

User.

|

|

|

|

|

|

|

Таблица 1.3 |

|

Адрес |

Регистры |

|

Имя |

Диапазон |

|

Размер |

||

|

состояния |

сегмента |

адресов |

|

сегмента |

|||

|

EXL |

ERL |

|

UM |

|

|

|

|

А(31)=0 |

0 |

0 |

|

1 |

useg |

0x0000_0000 |

|

2GB |

|

|

|

|

|

|

→ |

|

( 231байт) |

|

|

|

|

|

|

0x7FFF_FFFF |

|

|

Для всех допустимых виртуальных адресов режима User старший значащий бит адреса равен нулю, поскольку в режиме User допустимо обращение только к нижней половине карты

21

виртуальной памяти. Любая попытка обращения по адресу со старшим битом, равным 1, в режиме User вызывает прерывание по ошибке адресации. В режиме TLB виртуальный адрес перед преобразованием расширяется содержимым 8-разрядного поля ASID, образуя уникальный виртуальный адрес. Кэшируемость ссылки для страницы в этом режиме определяется установкой определенных бит строки TLB. В режиме FM, область виртуальных адресов 0x0000_0000-0x7FFF_FFFF преобразуется в область физических адресов 0x4000_0000-0xBFFF_FFFF. Кэшируемость задается полем KU регистра ConfigCP0.

Режим Kernel

Процессор находится в режиме Kernel, когда регистр StatusCP0 содержит хотя бы одно из следующих значений: UM = 0; ERL = 1; EXL = 1 Когда обнаруживается исключение, биты EXL или ERL устанавливаются, и процессор входит в режим Kernel. При завершении процедуры обработки исключения обычно выполняется команда возвращения из исключения (ERET). Команда ERET осуществляет переход по PC исключения, очищает ERL и EXL (если ERL=0). В результате возможен возврат процессора в режим User.

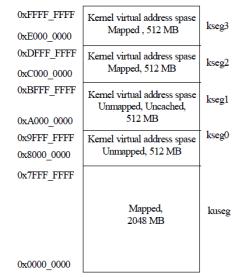

Виртуальное адресное пространство режима Kernel разделено на области в соответствии со значением старших битов виртуального адреса, как показано на рисунок 1.6. Кроме того, в табл. 1.4 содержатся характеристики сегментов режима

Kernel.

22

Рис.1.6. Виртуальное адресное пространство режима Kernel Таблица 1.4

Адрес |

Регистры |

Имя |

Диапазон |

Размер |

|||||

|

состояния |

сег- |

адресов |

сегмен- |

|||||

|

EXL |

ERL |

UM |

мента |

|

та |

|

||

A(31)=0 |

|

|

|

kuseg |

0x0000_0000 |

2 GB |

|||

|

|

|

|

|

→ |

(231) |

|||

|

|

|

|

|

0x7FFF_FFF |

|

|

|

|

|

|

|

|

|

F |

|

|

|

|

A(31:29)=1002 |

|

|

|

kseg0 |

0x8000_0000 |

512 MB |

|||

|

UM = 0 |

|

→ |

(229) |

|||||

|

|

0x9FFF_FFFF |

|

|

|

||||

|

|

или |

|

|

|

|

|||

A(31:29)=1012 |

|

ksegl |

0xA000_0000 |

512 MB |

|||||

EXL=1 |

|||||||||

|

|

→ |

(2 |

29 |

) |

||||

|

|

или |

|

|

|||||

|

|

|

0xBFFF_FFFF |

|

|

|

|||

|

ERL=1 |

|

|

|

|

||||

A(31:29)=1102 |

kseg2 |

0xC000_0000 |

512 MB |

||||||

|

|

|

|||||||

|

|

|

|

|

→ |

(229) |

|||

|

|

|

|

|

0xDFFF_FFFF |

|

|

|

|

A(31:29)=1112 |

|

|

|

kseg3 |

0xE000_0000 |

512 MB |

|||

|

|

|

|

|

→ |

(229) |

|||

|

|

|

|

|

0xFFFF_FFFF |

|

|

|

|

23

Режим Kernel, Пространство пользователя (kuseg)

Если старший значащий бит виртуального адреса A[31]=0, то выбирается виртуальное адресное пространство kuseg объемом 2 Гбайт, отображенное на адреса 0x0000_0000 - 0x7FFF_FFFF.

При ERL=0 в режиме TLB виртуальный адрес расширяется 8-битным значением поля ASID для образования уникального виртуального адреса. Кэшируемость определяется полем C строки TLB.

При ERL=0 в режиме FM, область виртуальных адресов 0x0000_0000-0x7FFF_FFFF преобразуется в область физических адресов 0x4000_0000-0xBFFF_FFFF. Кэшируемость задается полем KU регистра ConfigCP0.

При ERL = 1 в режимах TLB и FM, область адресов пользователя становится неотображаемым и некэшируемым адресным пространством. Виртуальный адрес kuseg соответствует тому же физическому адресу и не включает поле ASID. То есть, область виртуальных адресов kuseg соответствует области физических адресов 0x0000_0000-0x7FFF_FFFF.

Режим Kernel, пространство 0 режима Kernel (kseg0).

Если в режиме Kernel три старших бита виртуального адреса равны 1002 , выбирается виртуальное адресное пространство kseg0. Это область размером 229 байт (512 MB), которая расположена внутри границ, определяемых адресами

0x8000_0000 и 0x9FFF_FFFF.

Вне зависимости от состояния бита ERL и режима работы ссылки к kseg0 не отображаются, а физический адрес получается вычитанием 0x8000_0000 из виртуального адреса. Кэшируемость сегмента kseg0 определяется значением поля K0

регистра ConfigCP0.

24

Режим Kernel, пространство 1 режима Kernel (kseg1)

Если в режиме Kernel три старших бита виртуального адреса равны 1012 , выбирается виртуальное адресное пространство kseg1. Это область размером 229 байт (512 MB), которая расположена внутри границ, определяемых адресами

0xA000_0000 и 0xBFFF_FFFF.

Вне зависимости от состояния бита ERL и режима работы ссылки к kseg1 не отображаются, а физический адрес получается вычитанием 0xA000_0000 из виртуального адреса.

Режим Kernel, пространство 2 режима Kernel (kseg2)

Если в режиме Kernel три старших бита виртуального адреса равны 1102 , выбирается виртуальное адресное пространство kseg2.

Врежиме TLB вне зависимости от состояния бита ERL это виртуальное пространство отображается через TLB и его кэшируемость определяется полем C строки TLB.

Врежиме FM вне зависимости от состояния бита ERL это виртуальное пространство зафиксировано в физических адресах 0xC000_0000 - 0xDFFF_FFFF и его кэшируемость определяется полем K23 Регистра ConfigCP0.

Если в режиме Kernel три старших бита виртуального

адреса равны 1112 выбирается32-разрядное виртуальное адресное пространство kseg3. В режиме TLB вне зависимости от состояния бита ERL это пространство отображается через TLB и его кэшируемость определяется полем C строки TLB.В режиме FM вне зависимости от состояния бита ERL это виртуальное пространство зафиксировано в физических адресах 0xE000_0000 - 0xFFFF_FFFF и его кэшируемость определяется полем K23 регистра Config.

25

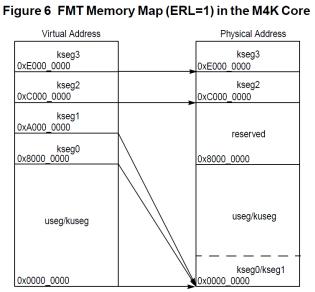

Особенности реализации MMU с помощью FMT

Основные особенности реализации блока управления памятью с помощью FixedMappingTranslation – фиксированное отображение адресов следующие: доступные пользователю адреса в user-mode сдвигаются на 0x40000000; это способ имитации части поведения TLB без TLB как такового; не защищает различные пользовательские программы друг от друга; требует минимального количества аппаратных ресурсов; опция FMT реализована на всех ядрах MIPS Technologies; используется в ядре MIPS M4K / микроконтроллере PIC32MX.

Принцип трансляция виртуальных адресов в физические с помощью Fixed Mapping Translation представлены на рис. 1.7 и 1.8.

Рис. 1.7. Карта памяти FMTпри установки бита ERL в 0

26

Рис. 1.8. Карта памяти FMTпри установки бита ERL в 1

1.1.5. Интерфейс памяти SRAM

Общие замечания

Если бы операнды хранились только в регистрах, то мы могли бы писать лишь простые программы, содержащие не более 32 переменных.

Поэтому данные также можно хранить в памяти. По сравнению с регистровым файлом память имеет много места для хранения данных, но доступ к ней занимает больше времени. По этой причине часто используемые переменные хранятся в регистрах. Комбинируя память и регистры, программа может получать доступ к большим объёмам данных достаточно быстро. Память устроена как массив слов с данными. Архитектура MIPS использует 32 битные адреса памяти и 32-битные слова с данными. MIPS использует побайтовую адресацию памяти. Это

27

значит, что каждый байт памяти имеет уникальный адрес. Однако, для лучшего понимания, мы сначала покажем пословную адресацию памяти, а потом расскажем про побайтовую адресацию памяти в MIPS.

На рис. 1.9 изображен массив памяти с пословной адресацией. Видно, что каждое 32-битное слово данных (англ.: word) имеет уникальный 32-битный адрес (англ.: wordaddress). И 32-битные адреса слов, и 32-битные значения (англ.: data) на Рис. 6.1 записаны в шестнадцатеричной системе счисления. Как видно из рисунка, значение 0xF2F1AC07 хранится в памяти по адресу 1 (шестнадцатеричные числа часто записываются с префиксом 0x). При графическом изображениипамяти традиционно размещают меньшие адреса внизу, а большие – наверху.

MIPS использует команду загрузить слово (англ.: loadword), lw, для чтения слова данных из памяти в регистр. В приведённом ниже примере кода показана загрузка слова, находящегося в памяти по адресу 1, в регистр $s3.

Рис. 1.9. Память с пословной адресацией

Инструкция lw определяет эффективный адрес в памяти как сумму базового адреса и смещения. Базовый адрес (записан в скобках в инструкции) является регистром. Смещение (записано перед скобками) является константой. В примере кода 6.6 базовый адрес – это регистр $0, содержащий значение 0, а сдвиг – это 1, поэтому инструкция lw читает значение из памяти по адресу ($0 + 1) = 1. Послевыполнения команды загрузки слова (lw) в $s3 появляется значение 0xF2F1AC07,

28

которое находилось в памяти по адресу 1, как было показано на рис. 1.9.

Загрузка слова из памяти с пословной адресацией

# This assembly code (unlike MIPS) assumes word-addressable memory

lw $s3, 1($0) # read memory word 1 into $s

Аналогичным образом MIPS использует инструкцию сохранить слово (англ.: storeword), sw, для записи данных из регистра в память. В примере кода программа записывает значение регистра $s7 в слово памяти с адресом 5. Эти примеры для простоты использовали $0 в качестве базового адреса, но на самом деле для указания базового адреса можно использовать любой регистр.

Запись слова в память с пословной адресацией

# This assembly code (unlike MIPS) assumes word-addressable memory

sw $s7, 5($0) # write $s7 to memory word 5

В двух предыдущих примерах показана компьютерная архитектура с пословной адресацией памяти. Но модель памяти MIPS имеет не пословную, а побайтовую адресацию, при которой каждый байт данных имеет уникальный адрес.

Так как 32-битное слово состоит из четырёх 8-битных байтов, то адрес каждого слова (англ.: word address) кратен четырём, как показано на рис. 1.10, где 32-битные адреса и значения слов тоже представлены в шестнадцатеричной системе счисления.

29

Рис. 1.10. Память с побайтовой адресацией

Впримере кода показано, как читать и записывать слова

впамять MIPS, адресуемую побайтно. Адрес слова – это порядковый номер слова, умноженный на четыре. Программа на ассемблере MIPS читаетслова 0, 2 и 3 и записывает слова 1, 8 и 100. Смещение может быть записано в десятичной или шестнадцатеричной системе счисления.

Доступ к памяти с побайтовой адресацией

lw $s0, 0($0) # read data word 0 (0xABCDEF78) into

$s0 |

|

|

lw |

$s1, 8($0) |

# read data word 2 (0x01EE2842) into |

$s1 |

|

|

lw $s2, 0xC($0) |

# read data word 3 (0x40F30788) into $s2 |

|

sw |

$s3, 4($0) |

# write $s3 to data word 1 |

sw |

$s4, 0x20($0) # write $s4 to data word 8 |

|

sw |

$s5, 400($0) |

# write $s5 to data word 100 |

Архитектура MIPS также включает инструкции lb и sb, которые загружают и сохраняют отдельные байты, а не слова. Они похожи на инструкции lw и sw и будут рассмотрены далее.

Вместо кэш, ядро M4K содержит интерфейс для SRAM типа памяти, который тесно связан с ядром.

30