2841

.pdf

1.2.6. Программирование платы ПЛИС

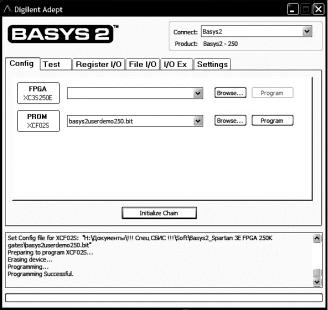

Digilent Basys 2

Осуществляется по средствам программы Adept компании Digilent, поставляется в комплекте с отладочной платой Digilent Basys 2 (см. рис. 1.2.9). Данная отладочная плата включает в себя две программируемые микросхемы

FPGA XC3S250E и PROM XCF02S.

Перед программированием необходимо подключить отладочную плату к ПК, переключить плату в режим «РС», осуществить удаление предыдущей прошивки и произвести программирование. В режиме «ROM» производиться непосредственная работа установленной прошивки (в случае программирования PROM).

Рис. 1.2.9. Диалоговое окно программы Adept

21

Подача входных сигналов на данной плате осуществляется при помощи набора переключателей, обозначенных SW0 – SW7, четырех не фиксируемых кнопок BTN0 – BTN3, а также есть возможность задания входных импульсов с клавиатуры, на плате для этого предусмотрен разъем PS/2. Выходные сигналы поступают на светодиоды LD0 – LD7, светодиодную панель или на монитор через разъем VGA.

Для проверки работоспособности перед началом программирования необходимо выполнить установку тестовой прошивки для проверки всех органов управления платой (файл basys2userdemo250.bit) или использовать вложенную утилиту «Test» программы Adept.

22

2.ЛАБОРАТОРНЫЕ РАБОТЫ

2.1.Лабораторная работа № 1. Проектирование функциональных узлов комбинационного типа

2.1.1.Общие указания по выполнению лабораторной работы

Целью лабораторной работы является углубление и закрепление знаний студентов в области основных понятий цифровой схемотехники, моделей и параметров логических элементов, а также получение навыков в проектировании программируемых логических интегральных схем (ПЛИС) с использованием систем автоматизированного проектирования (САПР) на языке VHDL.

Лабораторный практикум посвящен проектированию структур функциональных узлов комбинационного и последовательностного типа. В рамках данной лабораторной работы необходимо изучить структуру и основные принципы построения проекта на языке описания аппаратных средств VHDL с использованием программного комплекса ActiveHDL, построить модели простейших мультиплексоров и дешифраторов.

Перед выполнением лабораторной работы студент должен самостоятельно выполнить домашнее задание в соответствии с данными методическими указаниями.

Студент, явившийся на занятия, должен иметь методические указания по данной лабораторной работе. В начале занятия преподаватель проверяет выполнение студентом домашнего задания и наличие заготовки отчета по данной лабораторной работе в его рабочей тетради.

К выполненной работе прилагаются необходимые схемы, эскизы, тексты и результаты проектирования, протоколы работы с программным комплексом и другие материалы согласно указаниям по оформлению отчета.

23

2.1.2. Домашние задания и указания по их выполнению

Задание 1. Ознакомиться с моделями простейших логических элементов, системами их параметров. Изучить основные узлы комбинационного типа и их назначение. Для этого необходимо воспользоваться лекциями по курсу и литературой [1, С. 7-22].

Задание 2. Ознакомиться с основными принципами и методами построения моделей функциональных узлов на логическом уровне. При выполнении домашнего задания студент должен ознакомиться с основными сведениями о языке VHDL и способами описания проекта. Для этого необходимо воспользоваться лекциями по курсу и литературой [1, С. 81-91, С. 637-642, С. 673-680].

2.1.3.Вопросы к домашнему заданию

1.Дать определение идеализованного логического элемента.

2.Перечислить основные логические элементы, представить таблицы истинности.

3.Перечислить основные функциональные узлы комбинационного типа цифровой схемотехники, дать краткое описание.

4.Дать определение двоичного дешифратора, мультиплексора и демультиплексора, представить таблицы состояний, пояснить принцип работы.

5.Дать определение компаратора кода, сумматора и умножителя, представить таблицы состояний, пояснить принцип работы.

24

2.1.4. Лабораторные задания и указания по их выполнению

Задание 1. Построить и отладить модели мультиплексоров на логическом уровне, опираясь на пример приведенный в домашнем задании, схемы мультиплексоров представлены на рис. 2.1.1 и 2.1.2. Для каждой схемы необходимо построить временные диаграммы, демонстрирующие их работу.

Рис. 2.1.1. Схема мультиплексора «2-1»

Рис. 2.1.2. Схема мультиплексора «4-1»

25

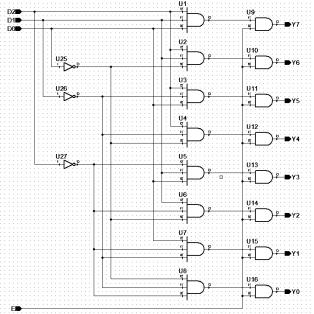

Задание 2. Построить и отладить модели дешифраторов на логическом уровне, опираясь на пример приведенный в домашнем задании, схемы дешифраторов представлены на рис. 2.1.3, 2.1.4 и 2.1.5. Для каждой схемы необходимо построить временные диаграммы, демонстрирующие их работу и соответствующие их таблицам состояний.

Рис. 2.1.3. Схема дешифратора «2-4» с инверсными выходами

Рис. 2.1.4. Схема дешифратора «2-4» с использованием разрешающего сигнала «E»

26

Рис. 2.1.5. Схема дешифратора «3-8» с использованием разрешающего сигнала «E»

Задание 3. Используя материал задания 2 и модель дешифратора «3-8» на языке описания аппаратуры VHDL, полученной на лабораторном практикуме, построить проект данного устройства в среде Xilinx ISE. В качестве внутреннего модуля в проекте использовать код VHDL, сгенерированный в результате моделирования в Active HDL. Подачу разрешающего импульса осуществить при помощи фиксируемого переключателя платы sw, задание входной последовательно по средствам кнопок btn, для отображения выходных сигналов использовать светодиоды Ld. Пример кода представлен ниже:

module DC_38E(input [0:2] btn, input [0:0] sw,

output [0:7] Ld);

27

DC38EN impl(.D0(btn [0]), .D1(btn [1]),

.D2(btn [2]), .E(sw [0]),

.Y0(Ld[0]), .Y1(Ld[1]), .Y2(Ld[2]), .Y3(Ld[3]),

.Y4(Ld[4]), .Y5(Ld[5]), .Y6(Ld[6]), .Y7(Ld[7]));

endmodule

DC38EN – имя файла с расширением *.vhd. RTL код проектируемого дешифратора.

Параметры файла конфигурации basys.ucf:

NET "ld<7>" LOC = "g1" ;

NET "ld<6>" LOC = "p4" ;

NET "ld<5>" LOC = "n4" ;

NET "ld<4>" LOC = "n5" ;

NET "ld<3>" LOC = "p6" ;

NET "ld<2>" LOC = "p7" ;

NET "ld<1>" LOC = "m11" ;

NET "ld<0>" LOC = "m5" ;

NET "sw<0>" LOC = "p11";

NET "btn<2>" LOC = "m4";

NET "btn<1>" LOC = "c11";

NET "btn<0>" LOC = "g12";

Задание 4. Используя материал задания 2 и модель дешифратора «2-4» на языке описания аппаратуры VHDL, полученной на лабораторном практикуме, построить проект данного устройства в среде Xilinx ISE. В качестве внутреннего модуля в проекте использовать код VHDL, сгенерированный в результате моделирования в Active HDL. Подачу разрешающего импульса осуществить при помощи встроенного тактового генератора clk на 25МГц, установку входной последовательно по средствам переключателей sw, для отображения выходных сигналов использовать светодиоды Ld. Пример кода представлен ниже:

28

module DC_24E(input [0:1] sw, input clk,

output [0:3] ld);

DC24EN impl(.D0(sw [0]), .D1(sw [1]), .E(clk),

.Y0(ld[0]), .Y1(ld[1]),

.Y2(ld[2]), .Y3(ld[3]));

endmodule

DC24EN – имя файла с расширением *.vhd. RTL код проектируемого дешифратора.

Параметры файла конфигурации basys.ucf:

NET "ld<3>" LOC = "p6" ;

NET "ld<2>" LOC = "p7" ;

NET "ld<1>" LOC = "m11" ;

NET "ld<0>" LOC = "m5" ; NET "clk" LOC = "b8"; NET "sw<1>" LOC = "l3"; NET "sw<0>" LOC = "p11";

2.1.5.Контрольные вопросы

1.Какова цель лабораторной работы?

2.В чем заключается лабораторное задание? Пояснить ход его выполнения.

3.Какие данные являлись исходными для выполнения работы?

4.Пояснить работу полученных моделей функциональных узлов комбинационного типа.

5.Сформулируйте выводы по данной лабораторной

работе.

29

2.2. Лабораторная работа № 2. Проектирование иерархических модулей

2.2.1. Общие указания по выполнению лабораторной работы

Целью лабораторной работы является углубление и закрепление знаний студентов в области функциональных узлов комбинационного типа цифровой схемотехники. В рамках данной лабораторной работы необходимо построить на логическом уровне иерархическую модель дешифратора адреса м мультиплексора с использованием программного комплекса Active-HDL на языке описания аппаратуры VHDL.

Перед выполнением лабораторной работы студент должен самостоятельно выполнить домашнее задание в соответствии с данными методическими указаниями.

Студент, явившийся на занятия, должен иметь методические указания по данной лабораторной работе. В начале занятия преподаватель проверяет выполнение студентом домашнего задания и наличие заготовки отчета по данной лабораторной работе в его рабочей тетради.

К выполненной работе прилагаются необходимые схемы, эскизы, тексты и результаты проектирования, протоколы работы с программным комплексом и другие материалы согласно указаниям по оформлению отчета.

2.2.2. Домашние задания и указания по их выполнению

Задание 1. Ознакомиться со структурой и принципом работы основных узлов комбинационного типа (двоичные дешифраторы, мультиплексоры и демультиплексоры, компараторы и сумматоры, матричные умножители). Для этого необходимо воспользоваться лекциями по курсу и литературой [1, С. 73-95, С. 104-122].

Задание 2. Изучить методы построения иерархических блоки (ИБ) FUB (Functional user block). ИБ применяются при

30