Архитектура построения и средства защиты СПЦС. Поздышева О.В., Мордовин А.И

.pdfФГБОУ ВПО «Воронежский государственный технический университет»

О. В. Поздышева А. И. Мордовин

АРХИТЕКТУРА ПОСТРОЕНИЯ И СРЕДСТВА ЗАЩИТЫ СПЦС

Утверждено Редакционно-издательским советом университета в качестве учебного пособия

Воронеж 2015

УДК 681.3

Поздышева О. В. Архитектура построения и средства защиты СПЦС: учеб. пособие [Электронный ресурс]. – Электрон. текстовые, граф. данные (2,05 Мб) / О. В. Поздышева, А. И. Мордовин. – Воронеж : ФГБОУ ВПО «Воронежский государственный технический университет», 2015. – 1 электрон. опт. диск (CD-ROM). – Систем. требования:

ПК 500 и выше; 256 Мб ОЗУ; Windows XP; Adobe Reader; 1024x768; CD-ROM; мышь. – Загл. с экрана.

В учебном пособии содержится краткий теоретический материал по принципам построения и алгоритмам функционирования микроконтроллеров на примере процессора семейства 8051 (C8051F120/30).

Издание соответствует требованиям Федерального государственного образовательного стандарта высшего профессионального образования по специальности 090302 «Информационная безопасность телекоммуникационных систем», дисциплине «Архитектура построения и средства защиты СПЦС».

Табл. 5. Ил. 35. Библиогр.: 4 назв.

Рецензенты: ОАО «Концерн «Созвездие» (канд. техн. наук, ведущий науч. сотрудник О.В. Поздышева);

д-р техн. наук, проф. А. Г. Остапенко

©Поздышева О.В., Мордовин А.И., 2015

©Оформление. ФГБОУ ВПО «Воронежский государственный технический университет», 2015

ВВЕДЕНИЕ

Несмотря на непрерывное развитие и появление все новых и новых 16- и 32-разрядных микроконтроллеров и микропроцессоров, наибольшая доля мирового микропроцессорного рынка и по сей день остается за 8- разрядными устройствами. Согласно данным компании Semico Research Corp., Phoenix, в 2005 году общий мировой объем продаж микроконтроллеров всех типов составил $11,4 миллиарда, при $5,56 миллиарда (или 48,6%) пришлось на долю 8-разрядных кристаллов. Это в 2,5 раза больше объема продаж ближайших конкурентов: 16-разрядных микроконтроллеров ($2,1 млрд.) и DSP ($2,4). По всем прогнозам аналитических компаний на ближайшие 5 лет лидирующее положение 8-разрядных микроконтроллеров на мировом рынке сохранится.

В настоящее время среди всех 8-разрядных микроконтроллеров - семейство MCS-51 является несомненным лидером по количеству разновидностей и количеству компаний, выпускающих его модификации. Оно получило свое название от первого представителя этого семейства - микроконтроллера 8051, выпущенного в 1980 году на базе технологии HMOS. Удачный набор периферийных устройств, возможность гибкого выбора внешней или внутренней программной памяти и приемлемая цена обеспечили этому микроконтроллеру успех на рынке. С точки зрения технологии микроконтроллер 8051 являлся для своего времени очень сложным изделием - в кристалле было использовано 128 тыс. транзисторов, что в 4 раза превышало количество транзисторов в 16-разрядном микропроцессоре

8086.

Важную роль в достижении такой высокой популярности семейства 8051 сыграла открытая политика фирмы Intel, родоначальницы архитектуры, направленная на широкое распространение лицензий на ядро 8051 среди

3

большого количества ведущих полупроводниковых компаний мира.

В результате на сегодняшний день существует более 200 модификаций микроконтроллеров семейства 8051, выпускаемых почти 20-ю компаниями. Эти модификации включают в себя кристаллы с широчайшим спектром периферии: от простых 20-выводных устройств с одним таймером и 1К программной памяти до сложнейших 100выводных кристаллов с 10-разрядными АЦП, массивами таймеров-счетчиков, аппаратными 16-разрядными умножителями и 64К программной памяти на кристалле. Каждый год появляются все новые варианты представителей этого семейства. Основными направлениями развития являются: увеличение быстродействия (повышение тактовой частоты и переработка архитектуры), снижение напряжения питания и потребления, увеличение объема ОЗУ и FLASH памяти на кристалле с возможностью внутрисхемного программирования, введение в состав периферии микроконтроллера сложных устройств типа системы управлениями приводами, CAN и USB интерфейсов и т.п.

Все микроконтроллеры из семейства MCS-51 имеют общую систему команд. Наличие дополнительного оборудования влияет только на количество регистров специального назначения.

Основными производителями клонов 51-го семейства в мире являются фирмы Philips, Siemens, Intel, Atmel, Dallas, Temic, Oki, AMD, MHS, Gold Star, Winbond, Silicon Systems и

ряд других.

4

ГЛАВА 1. АРХИТЕКТУРА МИКРОКОНТРОЛЛЕРОВ СЕМЕЙСТВА 8051

1.1. Процессорное ядро CIP-51

МК семейств C8051F12х и C8051F13х используют разработанное фирмой Silicon Labs’ процессорное ядро CIP-51, которое по системе команд полностью совместимо с ядром MCS-51TM. Для разработки программного обеспечения могут использоваться стандартные 803x/805x ассемблеры и компиляторы. Ядро содержит все периферию, соответствующую стандарту 8052, включая пять 16-разрядных таймеров/счетчиков, два полнодуплексных УАПП, 256 байт внутреннего ОЗУ, 128 байт адресного пространства регистров специального назначения, а также 8/4 8-разрядных порта ввода/вывода.

CIP-51 использует конвейерную архитектуру, что существенно повышает скорость выполнения команд по сравнению со стандартной архитектурой 8051. В МК с архитектурой 8051 все команды, кроме MUL и DIV, исполняются за 12 или 24 системных тактовых цикла при максимальной тактовой частоте 12…24 МГц. МК с ядром CIP51 исполняют 70% своих команд за один или два системных тактовых цикла, и только четыре команды требуют более четырех системных тактовых циклов.

Система команд CIP-51 состоит из 109 команд. В приведенной ниже таблице все команды сгруппированы по времени их выполнения.

Отношение системных тактовых циклов к количеству команд

Количество команд |

26 |

50 |

5 |

14 |

7 |

3 |

1 |

Количество |

|

|

|

|

|

|

|

системных тактовых |

1 |

2 |

2/3 |

3 |

3/4 |

4 |

4/5 |

циклов |

|

|

|

|

|

|

|

5

При работе на максимальной для ядра CIP-51 тактовой частоте 100 МГц производительность МК C8051F120/1/2/3 и C8051F130/1/2/3 может достигать 100 MIPS (МК C8051F124/5/6/7 имеют максимальную производительность 50

MIPS).

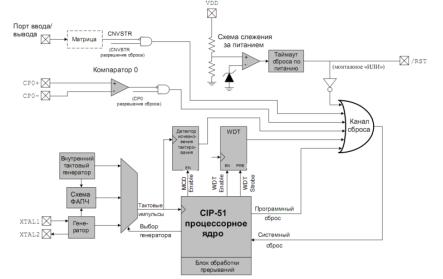

Ядро CIP-51 имеет ряд важных особенностей, которые позволяют улучшить общую производительность и упростить использование МК в конечных приложениях (рис. 1.1).

20 источников прерываний (8051 имеет 7 источников прерываний) позволяют многочисленным аналоговым и цифровым периферийным модулям прерывать работу МК. Система управления прерываниями требует меньшего вмешательства со стороны программы, что улучшает ее производительность. Дополнительные источники прерываний очень полезны при построении многозадачных систем, работающих в режиме реального времени.

Имеется семь источников сброса: встроенная схема слежения за напряжением питания, сторожевой таймер, детектор исчезновения тактирования, компаратор 0, принудительный программный сброс, входной сигнал CNVSTR0 и вывод /RST. Вывод /RST является двунаправленным, т.е. может быть как входом внешнего сигнала сброса, так и выходом сигнала сброса, сгенерированного внутри МК схемой слежения за питанием. Любой источник сброса, за исключением схемы слежения за питанием и входного вывода сброса, могут быть отключены программно; для включения/отключения схемы слежения за питанием используется вывод MONEN. Сторожевой таймер может быть включен после сброса типа POR (сброс при включении питания) в процессе инициализации МК.

МК имеет внутренний автономный тактовый генератор, который после сброса используется как источник тактовых импульсов по умолчанию. При необходимости можно «на лету» переключиться на внешний тактовый генератор, который для генерации тактовых импульсов использует кварцевый или керамический резонатор, конденсатор, RC-цепочку или

6

внешний источник импульсов. В приложениях с пониженным энергопотреблением крайне полезным может быть режим работы МК с медленным (мало потребляющим) внешним кварцевым генератором с периодическим переключением на быстрый (до 24,5 МГц) внутренний генератор. Кроме этого, для повышения производительности МК можно использовать встроенную систему ФАПЧ, которая позволяет повысить частоту системного тактового сигнала.

Рис. 1.1. Структурная схема модуля тактирования и сброса

CIP-51 имеет стандартную (8051) структуру адресного пространства памяти программ и данных. В состав памяти входит ОЗУ объемом 256 байт, старшие 128 байт которого имеют двойную конфигурацию. В режиме косвенной адресации осуществляется доступ к старшим 128 байтам ОЗУ общего назначения, а в режиме прямой адресации осуществляется доступ к 128 байтам адресного пространства регистров специального назначения (SFR). Младшие 128 байт ОЗУ доступны в режиме как прямой, так и косвенной адресации. Из них первые 32 байта адресуются как четыре

7

банка регистров общего назначения, а следующие 16 байт адресуются побайтно или побитно.

Все МК имеют встроенный блок 8-Кбайтного ОЗУ. К этому встроенному 8-Кбайтному блоку памяти можно обращаться во всем диапазоне адресов 64 Кбайтной внешней памяти данных (с перекрытием адресов по 8-Кбайтным границам). Все МК имеют также интерфейс внешней памяти

(external memory interface – EMIF) для доступа к внешней памяти данных или к периферийным модулям, отображенным на эту память. На адресное пространство внешней памяти данных может быть отображена либо только встроенная память, либо только внешняя память, либо их комбинация (адреса до 8Кбайт относятся к встроенной памяти, адреса свыше 8Кбайт относятся к EMIF). EMIF может работать с мультиплексированными и немультиплексированными шинами адреса/данных.

Память программ МК C8051F12x и C8051F130/1 состоит из 128 Кбайт разделенной на банки Flashпамяти. 1024 байт памяти с адресами 0x1FC00 – 0x1FFF зарезервированы. Память программ МК C8051F132/3состоит из 64 Кбайт Flash-памяти. Эта память может перепрограммироваться внутрисистемно секторами по 1024 байт, не требуя при этом специального внешнего напряжения программирования.

Во всех МК имеются также два 128-байтных сектора памяти, занимающие адреса от 0x20000 до 0x200FF, которые могут использоваться программой пользователя для хранения данных.

8

1.2. Организация памяти микроконтроллеров семейства 8051

Организация памяти МК с ядром CIP-51 (рис. 1.2) соответствует стандарту 8051. Имеется две отдельных области памяти, память программ и память данных, которые разделяют одно и то же адресное пространство, но доступ к ним осуществляется командами различного типа. Имеется 256 байт внутренней памяти данных и 128 Кбайт (C8051F12х и

C8051F130/1) или 64 Кбайт (C8051F132/3) адресного пространства внутренней памяти программ, реализованных в

CIP-51.

Рис. 1.2. Карта распределения памяти

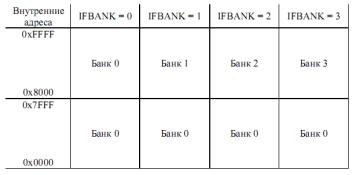

МК C8051F12х и C8051F130/1 имеют 128 Кбайт адресного пространства памяти программ. В МК эта память программ реализована в виде внутрисистемной перепрограммируемой Flash-памяти, разделенной на четыре

9

кодовых банка объемом 32 Кбайт каждый (рис. 1.3). Обычный кодовый банк (Банк 0) всегда доступен по адресам 0x0000…0x7FFF. Каждый из трех старших кодовых банков (Банк 1, Банк 2 и Банк 3) отображается на адресное пространство 0x8000…0xFFFF, в зависимости от значения бит регистра PSBANK. Биты IFBANK1-0 регистра PSBANK

определяют, какой из старших банков используется для выполнения кода, а бит COBANK регистра PSBANK выбирает банк, который используется для непосредственных операций чтения и записи Flash-памяти. Следует помнить, что 1024 байт памяти Банка 3 (0x1FC00…0x1FFF) зарезервированы и недоступны для хранения программы пользователя или данных. В МК C8051F132/3 физически реализовано 64 КБайт памяти программ, которая является внутрисистемной перепрограммируемой Flash-памятью, занимающей непрерывный блок адресов от 0x00000 до 0x0FFFF.

По умолчанию память программ настраивается только для чтения. Однако CIP-51 может записывать данные в память программ с помощью команды MOVX, для чего необходимо разрешить запись во Flash-память установкой в 1 бита PSCWL.0. Эта возможность позволяет CIP-51 обновлять программный код и использовать память программ для долговременного хранения данных.

Рис. 1.3. Карта распределения адресного пространства памяти для выборки команд

10