2363

.pdf

Считаем, что ток коллектора, ответвляющийся в цепь базы ничтожно мал, поэтому выходной ток распределяется по двум параллельным ветвям,

одна из которых содержит резистор Rк, а другая rэ и r*к. Так как r*к>> rэ, Rк,

получим

Rвыхэ= |

Uвых |

r*к||Rк=Rк r*к/( Rк+ r*к) Rк . |

(1.14) |

|

iвых |

||||

|

|

|

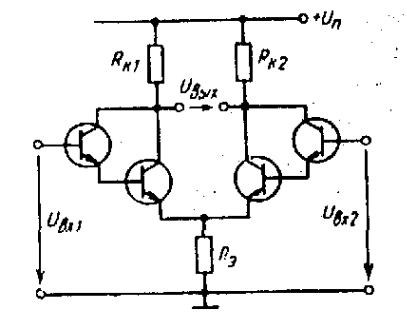

Так как, ДУ представлено в виде двух каскадов, то его выходное со-

противление, если пренебречь сопротивлением коллекторного перехода, в

два раза выше, чем каскада с ОЭ:

Rвых 2Rк. (1.15)

Входное сопротивление для разностного сигнала (дифференциальное сопротивление каскада) так же в два раза больше, чем у каскада с ОЭ.

Входное сопротивление каскада с ОЭ определяется из его эквивалент-

ной схемы (рис.1.7, в).

Так как входное напряжение Uвх складывается из падений напряжений на сопротивлении rб и rЭдиф, то можно записать так:

Uвх=U rб+Urэ=iб rб+rЭ (1+h21э) iб,

Rвх= |

Uвв |

|

iб rб rэ(1 h21э) |

rб rэ диф(1 h21э) . (1.16 ) |

iб |

|

iб |

||

|

|

|

Таким образом, входное сопротивление для ДУ:

Rвх=2 rб+rЭ диф (1+h21э) = 2h11э. (1.17)

= 2h11э. (1.17)

Входное сопротивление ДУ невелико и для его повышения можно включить в цепь эмиттера каждого транзистора равные по значению сопро-

тивления резисторы R0 так, чтобы rЭ диф= rЭ диф+R0 . Снижение коллекторных токов также увеличивает rЭ диф, но при этом уменьшается коэффициент уси-

ления.

При подключении нагрузки Rн к точкам 3 и 4 средняя точка будет все-

гда иметь нулевой потенциал, так как потенциалы симметричных точек Rн

изменяются на одно и тоже значение, но в противоположном направлении.

21

Поэтому каждый из каскадов ОЭ симметричной балансной схемы бу-

дет нагружен на резистор |

Rн |

, при этом дифференциальный коэффициент |

|||||||

2 |

|||||||||

|

|

|

|

|

|

|

|

||

усиления определяется |

|

|

|

|

|

|

|

|

|

|

|

|

h |

(R || |

Rн |

) |

|

|

|

|

|

|

|

|

|||||

Кд |

|

21э |

к |

2 |

|

|

|

||

|

|

|

|

. |

(1.18) |

||||

|

Rr / 2 h11э |

||||||||

|

|

|

|

|

|||||

Как видно из сравнения формул (1.13) и (1.18), дифференциальный ко-

эффициент при подключении нагрузки уменьшается.

Так как действие синфазного сигнала приводит к одинаковому измене-

нию коллекторных токов и напряжений транзисторов, то коллекторы транзи-

сторов в схеме (рис.1.7. а) можно объединить, представив работу каскада эк-

вивалентной схемой (рис.1.9.).

а) |

б) |

Рис. 1.9. Схема при подаче синфазного напряжения: |

|

а) схема при подаче синфазного напряжения, |

б) эквивалентная схема |

Тогда из эквивалентной схемы (рис.1.9, б) коэффициент усиления син-

фазного сигнала будет равен:

|

|

Uк.сф |

|

iк |

Rk |

|

|

h21э |

iб |

Rk |

|

|

|

K |

|

|

2 |

|

|

2 |

, |

( 1.19) |

|||||

|

|

|

|

|

|

|

|||||||

u.сф |

|

|

|

|

|

|

|

|

|

||||

|

Uвх.сф |

|

iб Rвх.сф |

|

iб |

Rвх.сф |

|

||||||

|

|

|

|

|

|||||||||

22

где Rвх.сф - входное сопротивление схемы для синфазных сигналов, которое

также найдем из эквивалентной схемы (рис.1.9)

R |

rб |

h |

(rэ |

R ) . |

( 1.20). |

||

вх.сф |

2 |

21э |

2 |

э |

|

||

Так как |

|

|

|

|

|

|

|

Rэ rэ,h21э Rэ rб , то Rвх.сф h21э Rэ . |

( 1.21) |

||||||

Подставим значение Rвх.сф в выражение (1.19), получим |

|

||||||

К |

|

|

Rк |

. |

|

(1.20) |

|

и.сф |

|

|

|

||||

|

|

2Rэ |

|

|

|||

|

|

|

|

|

|||

Для оценки степени усиления дифференциального и синфазного сигна-

лов применяют коэффициент подавления синфазного входного напряжения

Kп.сф . Отношение коэффициента усиления дифференциального сигнала Кд к

коэффициенту усиления синфазного сигнала Кс называется коэффициентом подавления синфазных сигналов Kп.сф (КООС):

К

Kп.сф Кд .

с

Значения коэффициента подавления достигают 10000 – 100000, т.е. 80 100

дБ.

Чем выше входное сопротивление дифференциального каскада, тем меньше входной ток синфазного сигнала, тем меньше изменения выходных напряжений Uвых1 и Uвых2. Для повышения входного сопротивления каскадно-

го входа синфазному сигналу необходимо увеличивать Rэ. Однако Rэ нельзя брать слишком большим, т.к. через этот резистор проходит ток покоя обоих транзисторов и при чрезмерно большом Rэ падение напряжения питания бу-

дет чрезмерно велико. Для устранения этого недостатка вместо резистора Rэ

включают транзистор по схеме с ОЭ, у которого сопротивление переменному току много больше сопротивления постоянному току (рис. 1.10).

23

Такая схема называется генератором стабильного тока (ГСТ). Основ-

ным функциональным звеном, обеспечивающим в ГСТ определенное и ста-

бильное значение выходного тока I0 и высокоомное сопротивление является

выходная цепь транзистора VT3, включенного по схеме ОЭ или ОИ.

Рис.1.10.1 Дифференциальный каскад с транзисторным источником тока в цепи эмиттера

Биполярный транзистор в схеме с ОЭ является стабилизатором тока,

обладающим большим выходным сопротивлением при наименьшем падении на нем напряжения. Для увеличения выходного сопротивления транзистора,

в цепь его эмиттера включают резистор сопротивлением от 100 до 1000 Ом,

обеспечивающий отрицательную обратную связь по току, а в цепь базы включают диод для температурной компенсации. При значении RT=1кОм ко-

эффициент ослабления синфазного сигнала превышает 60-80 дБ (рис.1.11).

В реальном дифференциальном каскаде с симметричным выходом не-

возможно обеспечить полную симметрию, приращение Uк1сф и Uк2сф

24

будут различными и на выходе схемы появляется Uвых.сф , который обу-

славливает дрейф нуля. Для снижения дрейфа нужно увеличивать RT.

Рис. 1.11. Дифференциальный каскад с диодом в цепи базы и резистором в цепи эмиттера источника тока

Работа дифференциального каскада с несимметричным выходом

Если нагрузка дифференциального каскада должна быть зазем-

ленной, то применяется несимметричный выход (рис.1.12)

Рис.1.12. Балансный каскад с несимметричным выходом

25

Дифференциальный коэффициент усиления дифференциального каска-

да при Rн  с несимметричным выходом очевидно в два раза меньше,

с несимметричным выходом очевидно в два раза меньше,

чем при симметричном выходе

|

U К 2дф |

К |

иэ |

h |

R |

|

|

К Д |

|

|

21э |

k |

. |

||

Uвх |

2 |

2(RГ / 2 h11э ) |

|||||

|

|

||||||

Когда входной сигнал Uвх1 |

подается на вход 1 от источника с внут- |

||||||

ренним сопротивлением RГ1 , а сигнал на входе 2 отсутствует, сигнал Uвх1

проходит через эмиттерный повторитель, выполненный на транзисторе VT1

и поступает на вход каскада ОБ на транзистор VT2, который усиливает сиг-

нал. При этом фаза выходного сигнала совпадает с входным сигналом, такой вход является неинвертирующим. Коэффициент усиления сигнала каскадом по первому входу К1.

Если входной сигнал |

Uвх2 поступает на вход 2 каскада, а сигнал на |

входе 1 отсутствует Uвх1 |

0, то фаза сигнала на выходе изменяется на |

противоположную, такой вход называется инвертирующим. Сигнал с входа 2

усиливается каскадом с ОЭ, в эмиттерную цепь которого включен эмиттер-

ный повторитель. В таком случае коэффициент усиления усилителя по вто-

рому входу К2.

|

Если о6а входа 1 и 2 дифференциального каскада с несимметричным |

||||||||||||||||

выходом подаются одновременно синфазные сигналы |

Uвх1 |

и |

Uвх2 , то |

||||||||||||||

приращение выходного напряжения |

Uвых.сф |

К1 Uвх1 |

К2 |

Uвх2 |

|||||||||||||

|

Если Uвх1.сф |

Uвх2.сф , получим |

|

|

|

|

|

|

|

|

|||||||

U |

|

U |

|

(К К |

|

) U |

|

К К |

|

К |

|

|

Rк |

. |

|||

вых.сф |

к2.сф |

2 |

вх.сф |

2 |

сф |

|

|

||||||||||

|

|

1 |

|

|

|

1 |

|

|

|

2Rэ |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

При действии противоположных сигналов |

|

|

|

|

|

|

|

|||||||||

|

Uвых.пф |

К1( |

Uвх1) |

К2Uвх2 |

(К1 |

Uвх1 |

К2 Uвх2 ). |

||||||||||

26

Если К |

К |

|

К |

Киэ |

; U |

|

Киэ ( U |

|

U |

|

) . |

2 |

|

вых.пф |

вх1 |

вх2 |

|||||||

1 |

|

|

2 |

|

2 |

|

|

||||

|

|

|

|

|

|

|

|

|

|

Формула показывает, что выходное напряжение в схеме пропорцио-

нально алгебраической разности входных напряжений в точках 1 и 2, т.е.

каскад усиливает разность входных напряжений.

Коэффициент подавления синфазного сигнала (КОСС)

|

|

|

КП |

Uвых.пф |

|

|

К Д |

. |

|

|

|

Uвых.сф |

|

К1 К2 |

|||

|

|

|

|

|

|

|||

Коэффициент подавления синфазной составляющей в схеме с симмет- |

||||||||

ричным выходом в |

1 |

|

раз выше, чем коэффициент подавления в схеме с не- |

|||||

|

|

|||||||

| |

| |

|

|

|

|

|

||

симметричным выходом КП.нс | | КП.с , где | |

| - разброс параметров |

|||||||

транзисторов.

В дифференциальных усилителях часто для задания эмиттерного тока транзисторов используется схема «токового зеркала». «Токовым зеркалом» называется электронное устройство с одним входом и одним или нескольки-

ми выходами, выходной ток (или токи) которого повторяет как по величине,

так и по направлению его входной ток. Простейшая схема токового зеркала на двух идентичных транзисторах VT1 и VT2 представлена на рисунке 1.12.

Транзистор VT1 используется в диодном включении.

Рис. 1.12. Схема токового зеркала

Так как его напряжение UКБ 0, то он работает на границе активного режима и режима насыщения. При этом его коллекторный и базовый токи

27

связаны соотношением IкVT1 |

IБVT1 h21э . Так как параметры транзисто- |

ров полностью идентичны, то из условия UБЭVT1 U БЭVT 2 следует, что |

|

IБVT1 IБVT 2 , при этом IКVT1 |

IКVT 2 , |

Iвх |

IКVT1 IБVT1 IБVT 2 , |

это условие можно записать |

|

|

I |

|

|

I |

|

|

(1 |

2 |

|

) , |

||

|

вх |

КVT1 |

|

|

|

|

||||||

|

|

|

|

|

h21э |

|||||||

|

|

|

|

|

|

|

|

|

||||

откуда |

|

|

|

|

|

|

|

|

|

|

|

|

IКVT1 |

I |

вх |

/(1 |

2/ h |

|

|

) , |

h21э 1, |

||||

|

|

|

|

|

|

21э |

|

|

|

|||

поэтому |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Iвх |

|

IКVT1 |

IКVT 2 , |

|||||||

следовательно, входной ток будет повторять выходной.

Использование токовых зеркал в качестве динамической нагрузки дифференциального каскада и в качестве источника тока в цепи эмиттеров позволяет получить коэффициент усиления входного дифференциального напряжения на одном каскаде свыше 5000 (при условии, что нагрузка на вы-

ходе усилителя отсутствует) и КОСС свыше 100 000 (100 дБ).

Рис. 1.13. Дифференциальный усилительный каскад с динамической на-

грузкой и источником тока в виде «токового зеркала»

28

Входное сопротивление дифференциального усилителя может быть существенно увеличено при использовании в каскаде полевых транзисторов.

При построении таких схем предпочтение отдается полевым транзисторам с управляющим р-п переходом. Это обусловлено следующими причинами:

более высокой стабильностью их характеристик;

большой электрической прочностью затвора (меньше боится пробоя статическим электричеством), большей допустимой разностью входных на-

пряжений (до 20-ЗОВ).

Типовая схема дифференциального каскада на транзисторе с управ-

ляющим p-n-переходом и каналом n-типа приведена па рис. 1.14.. Особенно-

стью этой схемы является использование в качестве истокового токозадаю-

щего элемента источника тока на полевом транзисторе VT3 и резисторе Rи.

Резисторы Rсм1 и Rсм2 предназначены для задания начального смещения на затворах транзисторов VT1 и VT2.

Рис. 1.14. Дифференциальный усилительный каскад на полевых транзисторах

Входное сопротивление дифференциального усилителя, выполненного на биполярных транзисторах, тоже может быть значительно увеличено при использовании в каскаде составных транзисторов. Следствием этого является

29

уменьшение входного тока усилителя, что крайне важно при его использова-

нии в виде интегральной схемы.

Рис. 1.15. Дифференциальный усилительный каскад на составных транзисторах

30