1916

.pdf

39

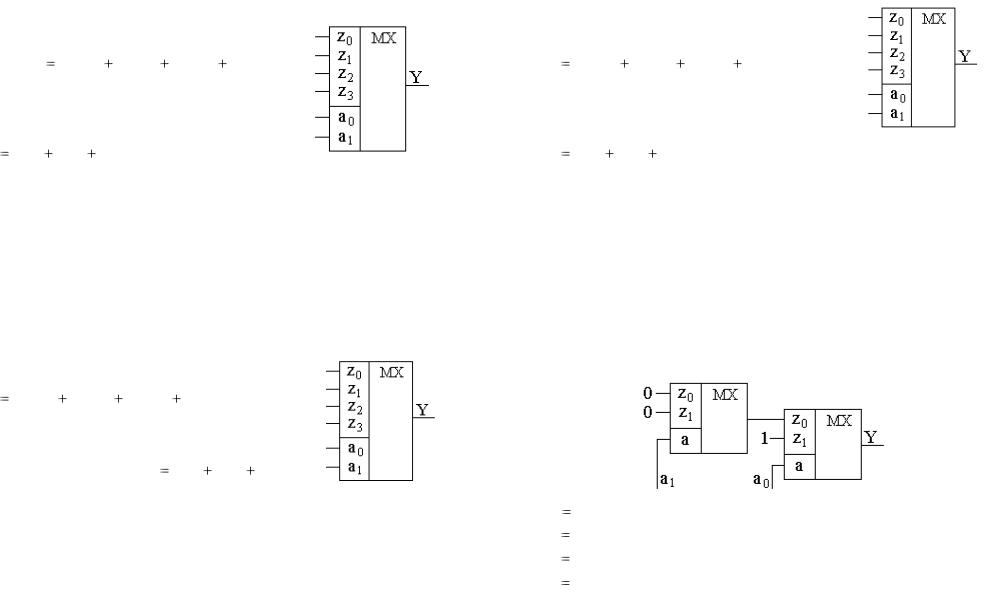

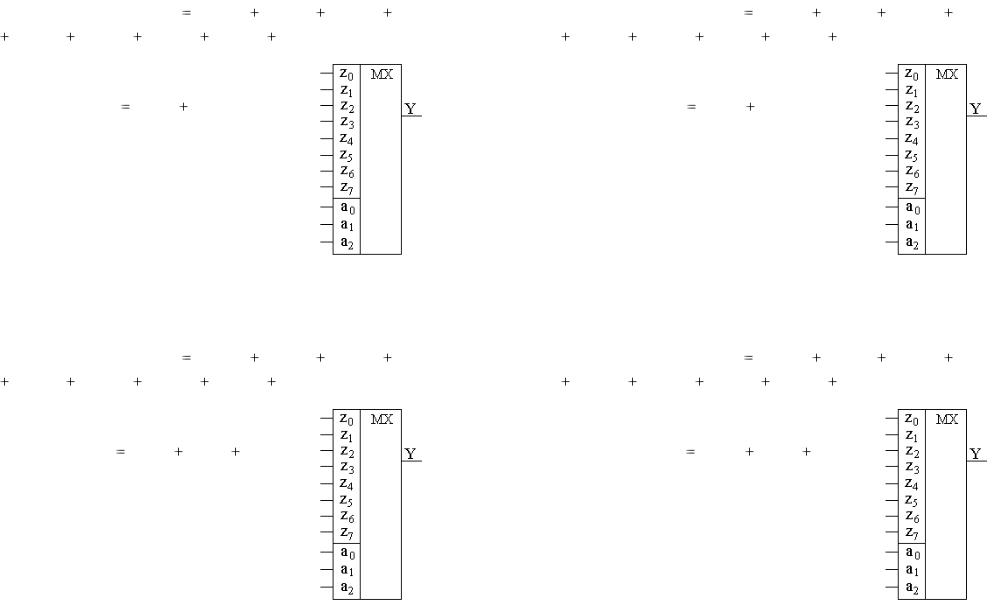

Задание {{9}}ТЗ ИЦМУ-5-9 КТ=1; МТ=0.6;

Отметьте правильный ответ Выходной сигнал показанного на рисунке

мультиплексора определяется выражени-

ем |

Y z0 a1a0 z1a1a0 z2 a1a0 z3 a1a0 . |

Если сигналы на входах a0 и a1 равны

соответственно |

a0 = x0 и a1 = x1 , то |

для |

|

реализации |

логической |

функции |

|

Y x1 x0 x1 x0 |

x1 x0 на входы z0 |

z1 z2 |

z3 |

необходимо подать последовательность бит

1101

1001

0100

1010

Задание {{10}}ТЗ ИЦМУ-5-10 КТ=1; МТ=0.6;

Отметьте правильный ответ Выходной сигнал показанного на рисунке

мультиплексора определяется выражением

Y z0 a1a0 z1a1a0 z2 a1a0 z3 a1a0 . Если

сигналы на входах a0 и a1 равны соответственно a0 = x0 и a1 = x1 , то для реализации

логической функции Y x1 x0 x1 x0 x1 x0 на входы z0 z1 z2 z3 необходимо подать по-

следовательность бит

1010

1001

1100

1011

40

Задание {{11}}ТЗ ИЦМУ-5-11 КТ=1; МТ=0.6;

Отметьте правильный ответ Выходной сигнал показанного на рисун-

ке мультиплексора определяется выражением

Y |

z0 a1a0 |

z1a1a0 |

z2 a1a0 |

z3 a1a0 . Если |

сигналы на входах a0 и a1 |

равны соот- |

|||

ветственно a0 = x0 |

и a1 = x1 , то для реали- |

|||

зации |

логической |

функции |

||

Y |

x1 x0 |

x1 x0 x1 x0 на входы z0 z1 z2 z3 |

||

необходимо подать последовательность бит

1101

1001

1100

1010

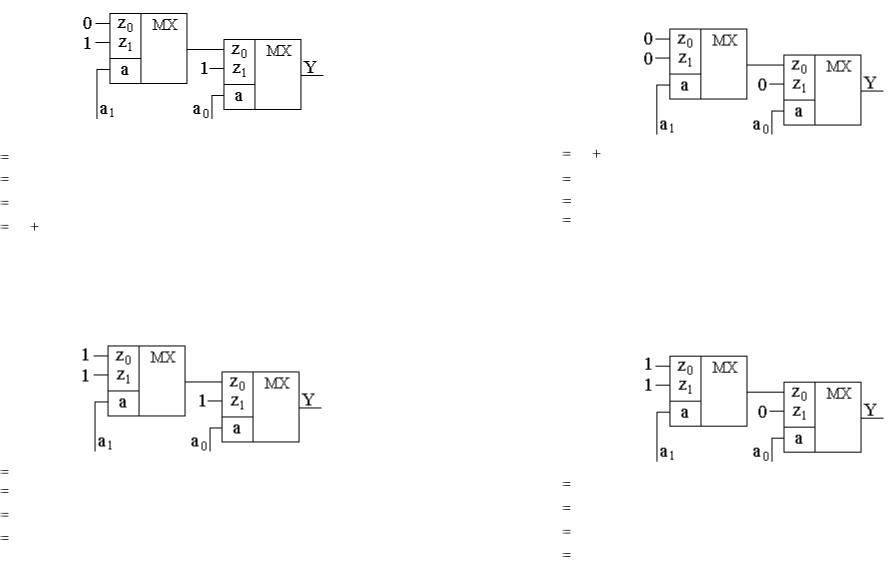

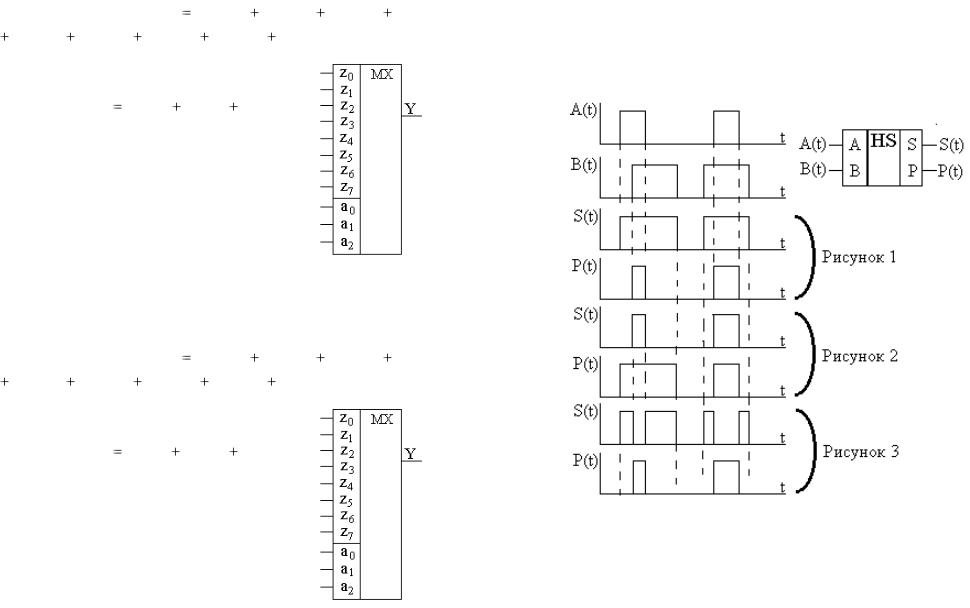

Задание {{12}}ТЗ ИЦМУ-5-12 КТ=1; МТ=0.4;

Показанное на рисунке соединение мультиплексоров формирует на выходе Y логическую функцию переменных a1 и a0 вида …

Y a1

Y a0

Y a1a0

Y a0

41

Задание {{13}}ТЗ ИЦМУ-5-13 КТ=1; МТ=0.4;

Показанное на рисунке соединение мультиплексоров формирует на выходе Y логическую функцию переменных a1 и a0 вида …

Y a1

Y a1

Y a1a0

Y a1 a0

Задание {{14}}ТЗ ИЦМУ-5-14 КТ=1; МТ=0.5;

Показанное на рисунке соединение мультиплексоров формирует на выходе Y логическую функцию переменных a1 и a0 вида …

Y 1

Y a0

Y a1a0

Y a1

42

Задание {{15}}ТЗ ИЦМУ-5-15 КТ=1; МТ=0.5;

Показанное на рисунке соединение мультиплексоров формирует на выходе Y логическую функцию переменных a1 и a0 вида …

Y a1 a0

Y a0

Y 0

Y a1

Задание {{16}}ТЗ ИЦМУ-5-16 КТ=1; МТ=0.5;

Показанное на рисунке соединение мультиплексоров формирует на выходе Y логическую функцию переменных a1 и a0 вида …

Y a0 Y a0 Y a1a0

Y a1

43

Задание {{17}}ТЗ ИЦМУ-5-17 КТ=1; МТ=0.5;

Показанное на рисунке соединение мультиплексоров формирует на выходе Y логическую функцию переменных a1 и a0 вида …

Y a1 a0

Y a1 a0

Y a1 a0

Y a1

Задание {{18}}ТЗ ИЦМУ-5-18 КТ=1; МТ=0.5;

Показанное на рисунке соединение мультиплексоров формирует на выходе Y логическую функцию переменных a1 и a0 вида …

Y a1a0

Y a0

Y a1a0

Y a1

44

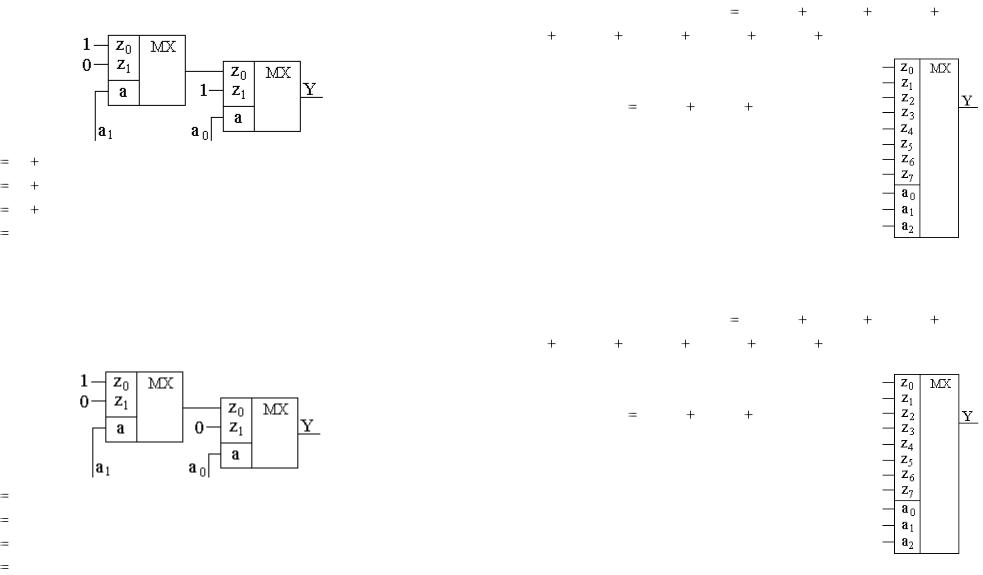

Задание {{19}}ТЗ ИЦМУ-5-19 КТ=1; МТ=0.9;

Отметьте правильный ответ Выходной сигнал показанного на рисунке мультиплексора оп-

ределяется выражением Y |

z0 |

|

2 |

|

|

|

|

|

z1 |

|

2 |

|

|

|

|

|

|

||||||||||

a |

a1a0 |

a |

a1a0 z2a2a1a0 |

||||||||||||||||||||||||

z3 |

|

2a1a0 |

z4a2 |

|

|

|

|

z5a2 |

|

|

|

z6a2a1 |

|

0 z7a2a1a0 . |

|||||||||||||

a |

a1a0 |

a1a0 |

|

a |

|||||||||||||||||||||||

Если сигналы на входах |

|

a |

|

равны |

a0 = x0 , |

||||||||||||||||||||||

a1 = x1 , a2 = x2 , то для реализации логической |

|||||||||||||||||||||||||||

функции Y |

x2 x1 x0 |

x2 x1 x0 |

|

x2 x1 x0 |

на вхо- |

||||||||||||||||||||||

ды z0 z1 z2 |

z3 z4 z5 z6 |

z7 |

необходимо подать |

||||||||||||||||||||||||

последовательность бит …

11010110

00110101

00010110

01011001

Задание {{20}}ТЗ ИЦМУ-5-20 КТ=1; МТ=0.9;

Отметьте правильный ответ Выходной сигнал показанного на рисунке мультиплексора оп-

ределяется выражением Y |

z0 |

|

2 |

|

|

|

|

|

z1 |

|

2 |

|

|

|

|

|

|

||||||||||

a |

a1a0 |

a |

a1a0 z2a2a1a0 |

||||||||||||||||||||||||

z3 |

|

2a1a0 |

z4a2 |

|

|

|

|

z5a2 |

|

|

|

z6a2a1 |

|

0 z7a2a1a0 . |

|||||||||||||

a |

a1a0 |

a1a0 |

|

a |

|||||||||||||||||||||||

Если сигналы на входах a |

|

равны |

a0 = x0 , |

||||||||||||||||||||||||

a1 = x1 , a2 = x2 , то для реализации логической |

|||||||||||||||||||||||||||

функции Y |

x2 x1 x0 |

x2 x1 x0 |

|

x2 x1 x0 |

на вхо- |

||||||||||||||||||||||

ды z0 z1 z2 z3 z4 z5 z6 z7 необходимо подать

последовательность бит …

00101100

00110101

11000101

01011001

45

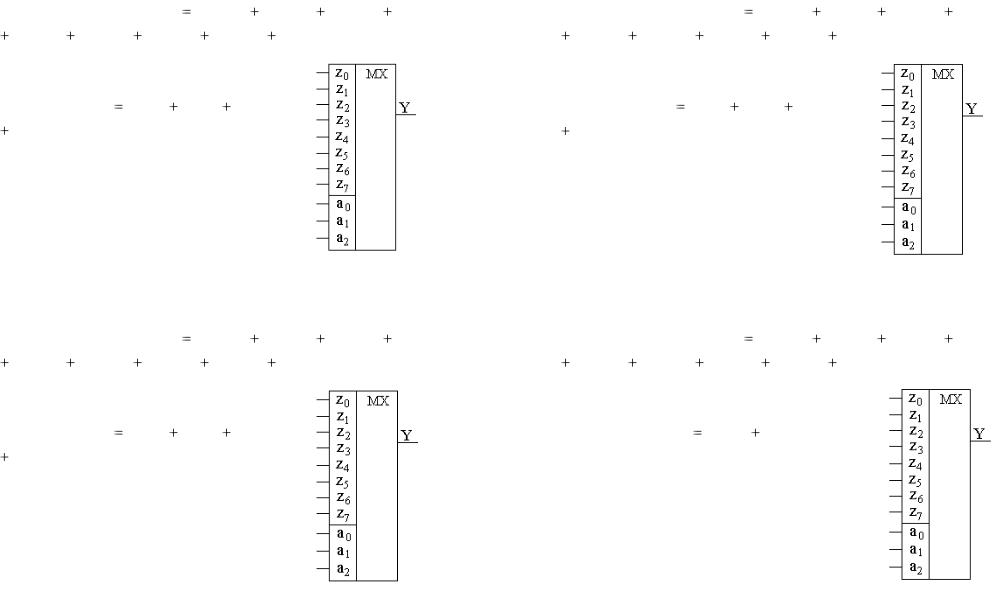

Задание {{21}}ТЗ ИЦМУ-5-21 КТ=1; МТ=0.9;

Отметьте правильный ответ Выходной сигнал показанного на рисунке мультиплексора оп-

ределяется выражением Y |

|

z0 |

|

|

2 |

|

|

|

|

|

|

z1 |

|

2 |

|

|

|

|

|

|

||||||||||||||||

|

a |

a1a0 |

a |

a1a0 z2a2a1a0 |

||||||||||||||||||||||||||||||||

z3 |

|

|

2a1a0 z4a2 |

|

|

|

|

|

|

z5a2 |

|

|

|

|

z6a2a1 |

|

0 |

|

z7a2a1a0 . |

|||||||||||||||||

a |

a1a0 |

a1a0 |

|

|

a |

|

||||||||||||||||||||||||||||||

Если сигналы на входах a равны a0 = x0 , |

||||||||||||||||||||||||||||||||||||

a1 = x1 , a2 = x2 , то для реализации логиче- |

||||||||||||||||||||||||||||||||||||

ской функции Y |

|

2 |

|

|

|

|

x2 x1 |

|

0 |

|

|

|

|

|

|

|

|

|

||||||||||||||||||

x |

x1x0 |

x |

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||

x2 |

|

|

z1 z2 |

z3 |

z4 z5 z6 z7 |

не- |

||||||||||||||||||||||||||||||

x1x0 на входы z0 |

||||||||||||||||||||||||||||||||||||

обходимо подать последовательность бит

…

01011001

10110101

10101000

10000110

Задание {{22}}ТЗ ИЦМУ-5-22 КТ=1; МТ=0.9;

Отметьте правильный ответ Выходной сигнал показанного на рисунке мультиплексора оп-

ределяется выражением Y |

|

|

z0 |

|

2 |

|

|

|

|

|

|

z1 |

|

2 |

|

|

|

|

|

|

|||||||||||||

a |

a1a0 |

a |

a1a0 z2a2a1a0 |

||||||||||||||||||||||||||||||

z3 |

|

|

2a1a0 z4a2 |

|

|

|

|

z5a2 |

|

|

|

|

z6a2a1 |

|

0 |

|

z7a2a1a0 . |

||||||||||||||||

a |

a1a0 |

a1a0 |

a |

|

|||||||||||||||||||||||||||||

Если сигналы на входах a равны a0 = x0 , |

|||||||||||||||||||||||||||||||||

a1 = x1 , a2 = x2 , то для реализации логиче- |

|||||||||||||||||||||||||||||||||

ской функции Y |

|

x2 x1 |

|

0 |

|

x2 |

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

x |

|

x1x0 |

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

x1 |

|

0 на входы |

|

z0 |

z1 z2 |

z3 z4 |

z5 z6 z7 |

не- |

|||||||||||||||||||||||||

x |

|

||||||||||||||||||||||||||||||||

обходимо подать последовательность бит

…

00100111

10110101

10110000

00011001

46

Задание {{23}}ТЗ ИЦМУ-5-23 КТ=1; МТ=0.9;

Отметьте правильный ответ Выходной сигнал показанного на рисунке мультиплексора оп-

ределяется выражением Y |

z0 |

|

2 |

|

|

|

|

|

|

z1 |

|

2 |

|

|

|

|

|

|

||||||||||||||||||

a |

a1a0 |

a |

a1a0 z2a2a1a0 |

|||||||||||||||||||||||||||||||||

z3 |

|

|

2a1a0 z4a2 |

|

|

|

|

|

|

z5a2 |

|

|

|

|

|

|

|

z6a2a1 |

|

0 |

|

z7a2a1a0 . |

||||||||||||||

a |

a1a0 |

a1a0 |

|

|

a |

|

||||||||||||||||||||||||||||||

Если сигналы на входах |

|

a |

равны a0 = x0 , |

|||||||||||||||||||||||||||||||||

a1 = x1 , a2 = x2 , то для реализации логиче- |

||||||||||||||||||||||||||||||||||||

ской функции Y |

|

2 x1x0 |

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

x |

|

|

x |

x1x0 |

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

x2 |

|

0 на входы z0 |

z1 |

z2 |

z3 z4 |

z5 z6 z7 необ- |

||||||||||||||||||||||||||||||

x |

||||||||||||||||||||||||||||||||||||

ходимо подать последовательность бит …

01011100

01011010

10111100

00010011

Задание {{24}}ТЗ ИЦМУ-5-24 КТ=1;

МТ=0.9;

Отметьте правильный ответ Выходной сигнал показанного на рисунке мультиплексора оп-

ределяется выражением Y |

z0 |

|

2 |

|

|

|

|

|

z1 |

|

2 |

|

|

|

|

|

|

|||||||||

a |

a1a0 |

a |

a1a0 z2a2a1a0 |

|||||||||||||||||||||||

z3 |

|

2a1a0 z4a2 |

|

|

|

|

z5a2 |

|

|

|

z6a2a1 |

|

0 z7a2a1a0 . |

|||||||||||||

a |

a1a0 |

a1a0 |

|

a |

||||||||||||||||||||||

Если сигналы на входах a |

равны |

a0 = x0 , |

||||||||||||||||||||||||

a1 = x1 , a2 = x2 , |

то для реализации логиче- |

|||||||||||||||||||||||||

ской функции |

|

Y |

x2 x1 x0 |

x0 на |

|

входы |

||||||||||||||||||||

z0 z1 z2 z3 z4 z5 z6 z7 |

необходимо подать по- |

|||||||||||||||||||||||||

следовательность бит … |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

10111100 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

10110101 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

01110101

01010101

47

Задание {{25}}ТЗ ИЦМУ-5-25 КТ=1; МТ=0.9;

Отметьте правильный ответ Выходной сигнал показанного на рисунке мультиплексора оп-

ределяется выражением Y |

|

|

z0 |

|

2 |

|

|

|

|

|

|

z1 |

|

2 |

|

|

|

|

|

|

|||||||||

|

|

a |

a1a0 |

a |

a1a0 z2a2a1a0 |

||||||||||||||||||||||||

z3 |

|

2a1a0 |

z4a2 |

|

|

|

|

z5a2 |

|

|

|

z6a2a1 |

|

0 |

|

z7a2a1a0 . |

|||||||||||||

a |

a1a0 |

a1a0 |

|

a |

|

||||||||||||||||||||||||

Если сигналы на входах |

a |

равны a0 = x0 , |

|||||||||||||||||||||||||||

a1 = x1 , a2 = x2 , то для реализации логиче- |

|||||||||||||||||||||||||||||

ской функции Y |

x2 x1 x0 |

|

x2 x1 на входы |

||||||||||||||||||||||||||

z0 z1 z2 z3 |

z4 z5 z6 z7 |

необходимо подать |

|||||||||||||||||||||||||||

последовательность бит …

00010011

00101111

10111100

01011111

Задание {{29}}ТЗ ИЦМУ-5-26 КТ=1; МТ=0.9;

Отметьте правильный ответ Выходной сигнал показанного на рисунке мультиплексора оп-

ределяется выражением Y |

|

|

z0 |

|

2 |

|

|

|

|

|

|

z1 |

|

2 |

|

|

|

|

|

|

||||||||||

|

|

a |

a1a0 |

a |

a1a0 z2a2a1a0 |

|||||||||||||||||||||||||

z3 |

|

2a1a0 |

z4a2 |

|

|

|

|

z5a2 |

|

|

|

z6a2a1 |

|

0 |

|

z7a2a1a0 . |

||||||||||||||

a |

a1a0 |

a1a0 |

|

a |

|

|||||||||||||||||||||||||

Если сигналы на входах |

a |

равны a0 = x0 , |

||||||||||||||||||||||||||||

a1 = x1 , |

a2 = x2 , то для реализации логиче- |

|||||||||||||||||||||||||||||

ской функции Y |

x2 x1 x0 |

|

x2 x1 x0 x2 x1 на |

|||||||||||||||||||||||||||

входы |

z0 |

z1 z2 z3 z4 z5 z6 |

z7 |

|

необходимо |

|||||||||||||||||||||||||

подать последовательность бит …

11010000

00111001

10111100

11000110

48

Задание {{30}}ТЗ ИЦМУ-5-27 КТ=1;

МТ=0.9;

Отметьте правильный ответ Выходной сигнал показанного на рисунке мультиплексора оп-

ределяется выражением Y |

z0 |

|

2 |

|

|

|

|

|

z1 |

|

2 |

|

|

|

|

|

|

|||||||||

a |

a1a0 |

a |

a1a0 z2a2a1a0 |

|||||||||||||||||||||||

z3 |

|

2a1a0 z4a2 |

|

|

|

|

z5a2 |

|

|

|

z6a2a1 |

|

0 z7a2a1a0 . |

|||||||||||||

a |

a1a0 |

a1a0 |

|

a |

||||||||||||||||||||||

Если сигналы на входах a |

равны a0 = x0 , |

|||||||||||||||||||||||||

a1 = x1 , a2 = x2 , |

то для реализации логичес- |

|||||||||||||||||||||||||

кой функции |

Y |

x2 x1 x0 |

x2 на |

входы |

||||||||||||||||||||||

z0 z1 z2 z3 z4 z5 z6 z7 |

необходимо |

подать |

||||||||||||||||||||||||

последовательность бит … |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

01001111 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

00001001 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

10111100 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

01011111 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Задание {{31}}ТЗ ИЦМУ-5-28 КТ=1; МТ=0.9;

Отметьте правильный ответ Выходной сигнал показанного на рисунке мультиплексора оп-

ределяется выражением Y |

|

z0 |

|

2 |

|

|

|

|

|

z1 |

|

2 |

|

|

|

|

|

|

|||||||||

|

a |

a1a0 |

a |

a1a0 z2a2a1a0 |

|||||||||||||||||||||||

z3 |

|

2a1a0 |

z4a2 |

|

|

|

|

z5a2 |

|

|

|

z6a2a1 |

|

0 |

z7a2a1a0 . |

||||||||||||

a |

a1a0 |

a1a0 |

|

a |

|||||||||||||||||||||||

Если сигналы на входах |

a |

равны a0 = x0 , |

|||||||||||||||||||||||||

a1 = x1 , a2 = x2 , |

то для реализации логичес- |

||||||||||||||||||||||||||

кой функции |

Y |

x2 x1 x0 |

|

x2 x1 x0 |

x0 |

на |

|||||||||||||||||||||

входы z0 |

z1 z2 z3 z4 |

z5 z6 z7 |

необходимо по- |

||||||||||||||||||||||||

дать последовательность бит …

10100000

00001001

01011111

01011110

49

Задание {{32}}ТЗ ИЦМУ-5-29 КТ=1; МТ=0.9;

Отметьте правильный ответ Выходной сигнал показанного на рисунке мультиплексора оп-

ределяется выражением Y |

|

|

z0 |

|

2 |

|

|

|

|

|

|

z1 |

|

2 |

|

|

|

|

|

|

|||||||||

|

|

a |

a1a0 |

a |

a1a0 z2a2a1a0 |

||||||||||||||||||||||||

z3 |

|

2a1a0 |

z4a2 |

|

|

|

|

z5a2 |

|

|

|

z6a2a1 |

|

0 |

|

z7a2a1a0 . |

|||||||||||||

a |

a1a0 |

a1a0 |

|

a |

|

||||||||||||||||||||||||

Если сигналы на входах |

a |

равны a0 = x0 , |

|||||||||||||||||||||||||||

a1 = x1 , a2 = x2 , то для реализации логичес- |

|||||||||||||||||||||||||||||

кой функции Y |

x2 x1 x0 |

|

x2 x1 x0 x1 x0 на |

||||||||||||||||||||||||||

входы z0 |

z1 z2 z3 |

z4 |

z5 z6 |

z7 |

|

необходимо |

|||||||||||||||||||||||

подать последовательность бит …

10001101

01100110

11001100

01010001

Задание {{33}}ТЗ ИЦМУ-5-30 КТ=1; МТ=0.9;

Отметьте правильный ответ Выходной сигнал показанного на рисунке мультиплексора оп-

ределяется выражением Y |

|

|

z0 |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

a |

a1a0 z1a2a1a0 z2a2a1a0 |

||||||||||||||||||||||||

z3 |

|

2a1a0 |

z4a2 |

|

|

|

|

|

|

|

z6a2a1 |

|

0 |

z7a2a1a0 . |

|||||||||||||

a |

a1a0 z5a2a1a0 |

|

a |

||||||||||||||||||||||||

Если сигналы на входах |

a |

равны a0 = x0 , |

|||||||||||||||||||||||||

a1 = x1 , a2 = x2 , то для реализации логичес- |

|||||||||||||||||||||||||||

кой функции Y |

x2 x1 x0 |

|

x2 x1 x0 x2 x0 |

на |

|||||||||||||||||||||||

входы z0 |

z1 z2 z3 |

z4 z5 z6 |

z7 |

|

необходимо |

||||||||||||||||||||||

подать последовательность бит … |

|

|

|

|

|

|

|

|

|||||||||||||||||||

01011010 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

00001010

10101001

01010101

50

6: Сумматоры

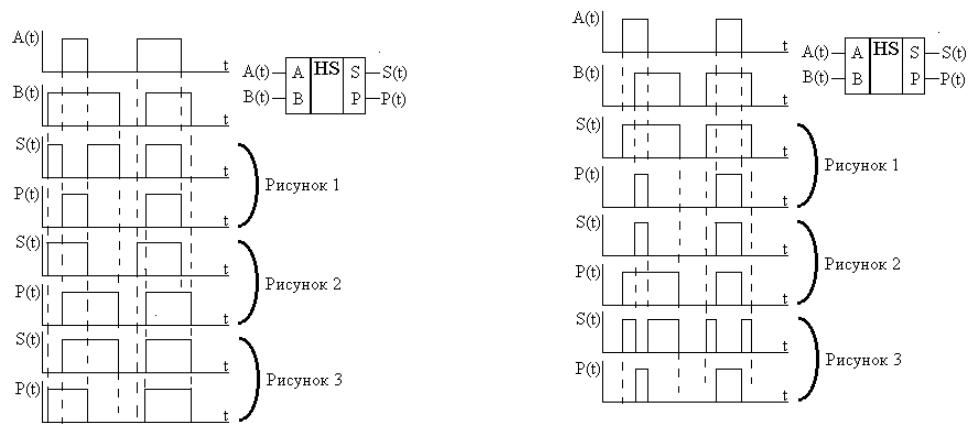

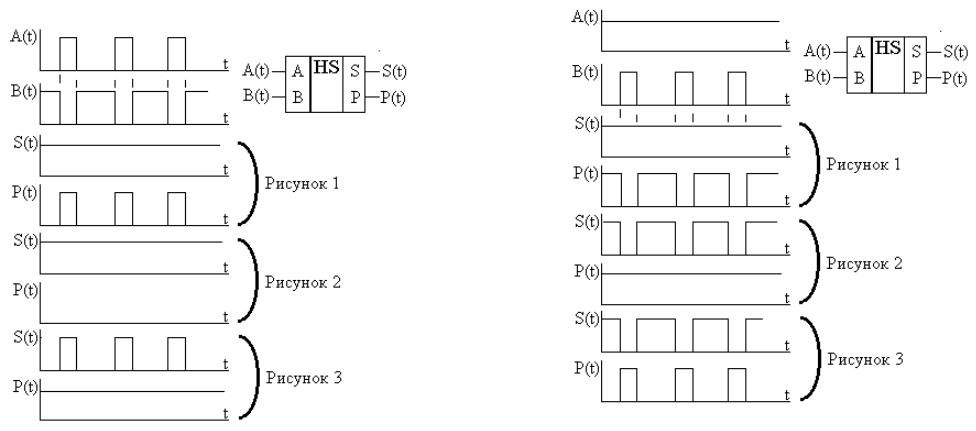

Задание {{1}}ТЗ ИЦМУ-6-1 КТ=1; МТ=0.8;

При подаче на входы полусумматора HS показанных на рисунке сигналов A(t) и B(t) выходные сигналы суммы S(t) и переноса P(t) имеют вид

Рисунок 3 Рисунок 2 Рисунок 1

51

Задание {{2}}ТЗ ИЦМУ-6-2 КТ=1; МТ=0.8;

При подаче на входы полусумматора HS показанных на рисунке сигналов A(t) и B(t) выходные сигналы суммы S(t) и переноса P(t) имеют вид

Рисунок 1 Рисунок 2 Рисунок 3

52

Задание {{3}}ТЗ ИЦМУ-6-3 КТ=1; МТ=0.8;

При подаче на входы полусумматора HS показанных на рисунке сигналов A(t) и B(t) выходные сигналы суммы S(t) и переноса P(t) имеют вид

Рисунок 1 Рисунок 2 Рисунок 3

53

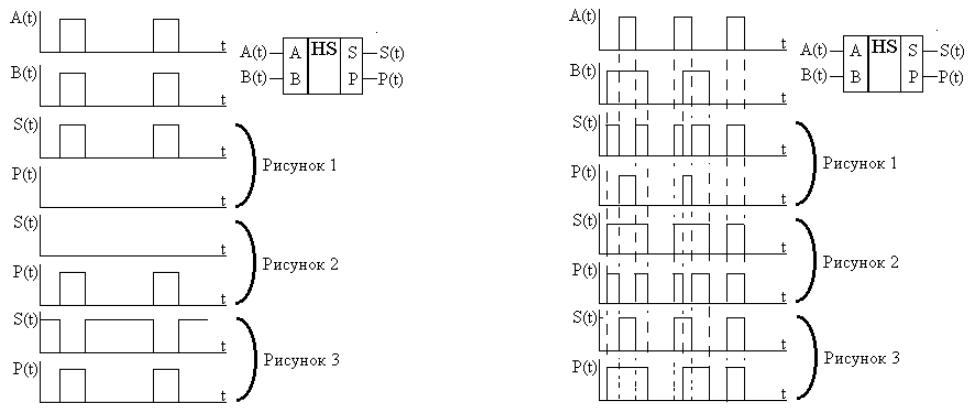

Задание {{4}}ТЗ ИЦМУ-6-4 КТ=1; МТ=0.8;

При подаче на входы полусумматора HS показанных на рисунке сигналов A(t) и B(t) выходные сигналы суммы S(t) и переноса P(t) имеют вид

Рисунок 3 Рисунок 2 Рисунок 1

54

Задание {{5}}ТЗ ИЦМУ-6-5 КТ=1; МТ=0.8;

При подаче на входы полусумматора HS показанных на рисунке сигналов A(t) и B(t) выходные сигналы суммы S(t) и переноса P(t) имеют вид

Рисунок 1 Рисунок 2 Рисунок 3

55

Задание {{6}}ТЗ ИЦМУ-6-6 КТ=1; МТ=0.8;

При подаче на входы полусумматора HS показанных на рисунке сигналов A(t) и B(t) выходные сигналы суммы S(t) и переноса P(t) имеют вид

Рисунок 1 Рисунок 2 Рисунок 3

Задание {{7}}ТЗ ИЦМУ-6-7 КТ=1; МТ=0.8;

При подаче на входы полусумматора HS показанных на рисунке сигналов A(t) и B(t) выходные сигналы суммы S(t) и переноса P(t) имеют вид

Рисунок 3 Рисунок 2 Рисунок 1

56 |

57 |

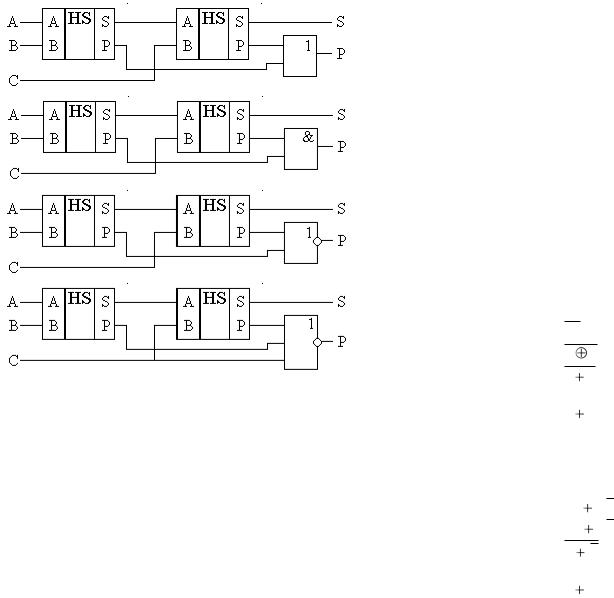

Задание {{8}}ТЗ ИЦМУ-6-8 КТ=1; МТ=0.3;

Схема полного сумматора на базе двух полусумматоров имеет вид …

Задание {{9}}ТЗ ИЦМУ-6-9 КТ=1; МТ=0.5;

Для реализации полного сумматора необходимо использовать два полусумматора и логический элемент …

2И

2ИЛИ-НЕ

2ИЛИ

2И-НЕ

58

Задание {{10}}ТЗ ИЦМУ-6-10 КТ=1; МТ=0.5;

Для реализации полного сумматора на двух полусумматорах выход переноса образуется объединением выходов переноса полусумматоров с помощью логического элемента … … 2ИЛИ

2И

2И-НЕ

2ИЛИ-НЕ

Задание {{11}}ТЗ ИЦМУ-6-11 КТ=1; МТ=0.5;

Для реализации полного сумматора необходимо использовать … полусумматора

Задание {{12}}ТЗ ИЦМУ-6-12 КТ=1; МТ=0.5;

Число входов полного сумматора равно …

7: Компараторы

Задание {{1}}ТЗ ИЦМУ-7-1 КТ=1; МТ=0.2;

Компаратор на равенство для одноразрядных слов a и b требует реализации логической функции вида …

ab

a b

a b ab

a b

Задание {{2}}ТЗ ИЦМУ-7-2 КТ=1; МТ=0.2;

Компаратор на равенство для одноразрядных слов a и b требует реализации логической функции вида …

ab ab

ab ab

a b ab

a b

59