Проектирование встроенных управляющих систем реального времени

..pdf

содержимое кэш-памяти второго уровня находится в кэш-памяти третьего уровня.

Во всех типах кэш-памяти используется следующая модель. MM разделяется на блоки фиксированного размера, которые называются строками кэш-памяти. Строка кэш-памяти состоит из нескольких последовательных байтов (обычно от 4 до 64). В любой момент несколько строк находятся в кэш-памяти. Когда происходит обращение к кэшпамяти, контроллер кэш-памяти проверяет, есть ли нужное слово в данный момент кэш-памяти. Если есть (попадание), то можно сэкономить время, требуемое на доступ к ОП. Если данного слова в кэш-памяти нет (промах), то какая-либо строка из нее удаляется, а вместо нее помещаетсянужнаястрокаизMM илиизкэш-памятиболеенизкогоуровня.

1.3.2.3. Кэш-память прямого отображения

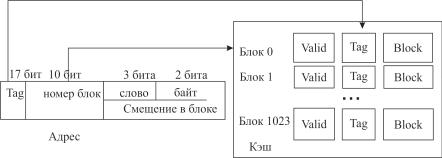

Кэш-память прямого отображения является самым простым типом кэш-памяти. На рис. 1.14 приведен пример одноуровневой кэш-памяти, содержащей 1024 блока по 32 байта.

Рис. 1.14. Кэш-память прямого отображения и формат адреса

Каждый элемент кэш-памяти состоит из трех частей:

1.Поле Tag (бирка), содержит старшие 17 разрядов адреса памяти, из которого поступил блок данных (адрес блока).

2.Поле Valid (действительно), содержит сведения о достоверности данных.

3.Поле Block, содержит копию блока данных памяти.

В кэш-памяти прямого отображения данный блок может храниться только в одном месте по номеру блока. Когда процессор выдает адрес памяти, контроллер кэш-памяти выделяет из этого адреса 10 бит номе-

61

ра блока и использует их для поиска в кэш-памяти одного из 1024 элементов. Если этот элемент действителен, то производится сравнение поля Tag адреса и поля Tag кэш-памяти. Если поля равны, то попадание, иначе – промах. В случае попадания слово считывается из кэшпамяти. При промахе или недействительности, блок вызывается из памяти и сохраняется в кэш-памяти, заменяя тот блок, который там был.

1.3.2.4.Ассоциативная по множеству кэш-память

Вкэш-памяти прямого отображения одноименные блоки MM конкурируют за право занять одну и ту же область в кэш-памяти. Если программе часто требуются ячейки с адресами 0х00000000 и 0х0000800000, то будут иметь место постоянные конфликты, и каждое обращение повлечет за собой замещение нулевого блока. Чтобы разрешить эту проблему, нужно сделать так, чтобы одноименные блоки помещались в нескольких местах (множествах) кэш-памяти.

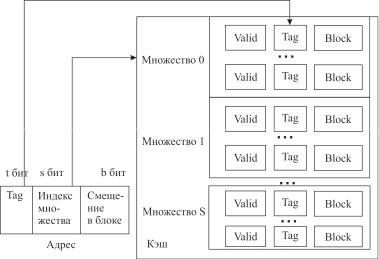

На рис. 1.15 приведена ассоциативная по множеству кэш-память. Такая память сложнее предыдущей, поскольку требуется проверить все множества, чтобы узнать, есть ли нужный блок. Память для хранения тэгов адресов реализуется как ассоциативная, что позволяет исключить перебор при поиске места блока.

Рис. 1.15. Ассоциативная по множеству кэш и формат адреса

Если нужно поместить новый блок в кэш-память, то какой из старых блоков нужно заместить? Для этого хорошо подходит рассмотренный выше алгоритм LRU.

62

Обобщим параметры кэш-памяти: m – разрядность адреса памяти;

M = 2m – величина адресного пространства в байтах; S = 2s – число множеств кэш;

E – число линий (входов) в множестве; B = 2b – размер блока в байтах;

t = m * s*b – число битов тега; C – общий размер кэш в байтах.

Таким образом, кэш может быть охарактеризована четверкой (m, S, E, B), а общий размер кэш составляет C = S*E *B байт.

1.3.2.5. Обновление кэш-памяти

При работе с кэш-памятью одновременно могут существовать две копии одних и тех же данных: одна – в кэш, другая – в основной памяти. В MM данные может изменять не только процессор, но и устройства ввода-вывода, работающие по каналу прямого доступа в память. Поэтому необходимо поддерживать их непротиворечивость или когерентность. В MPS c несколькими МП, разделяющими общую MM, также необходимо поддерживать когерентность, но уже и кэш этих МП.

Во всех решениях контроллер кэш-памяти разрабатывается так, чтобы кэш-память могла перехватывать запросы на магистрали, контролируя все запросы магистрали от других процессоров и устройств ввода-вывода, и предпринимать необходимые действия. Эти устройства называются кэш-памятью с отслеживанием (Snooping Cashe). Набор правил, которые выполняются кэш-памятью, процессорами и MM, чтобы предотвратить появление различных вариантов данных в нескольких блоках кэш-памяти, формирует протокол когерентности кэширования. Единица передачи и хранения кэш-памяти называется строкой или блоком кэш-памяти (32 или 64 байт).

Самый простой протокол когерентности кэширования называется сквозной записью (write through). В случае промаха кэш-памяти при записи слова, которое было изменено, оно записывается в MM. Строка, содержащая нужное слово, не загружается в кэш-память. В случае попадания при записи кэш обновляется, а слово, плюс ко всему, записывается в MM. Всегда при обновлении кэш-памяти одновременно обновляется и основная память.

Другой вариант поведения при промахах по записи – загрузка кэшпамяти (политика заполнения по записи – write-allocate). Заполнения по

63

записи эффективно, когда высока вероятность повторного обращения

кслову, вызвавшему промах.

Вустройствах с отслеживанием все кэши отслеживают все запросы

магистрали, и всякий раз, когда записывается слово, оно обновляется в кэш-памяти инициатора запроса, обновляется в MM и удаляется из всех остальных кэшей.

1.3.2.6. Протокол когерентности кэширования с обратной записью

При большом количестве процессоров не эффективно каждый раз перезаписывать ОП. Вместо этого используется обратная запись (write back). Используется бит изменения в поле состояния кэша. Этот бит устанавливается, если блок был обновлен новыми данными и является более поздним, чем его оригинальная копия в основной памяти. Перед тем как перезаписать блок в кэш-памяти, контроллер проверяет состояние этого бита. Если он установлен, то контроллер переписывает данный блок и основную память перед загрузкой новых данных в кэшпамять.

Рассмотрим один из популярных протоколов с обратной записью MESI. MESI – аббревиатура состояния кэш-памяти:

Invalid – блок кэш-памяти содержит недействительные данные. Shared – в нескольких кэшах содержатся одинаковые блоки, основ-

ная память обновлена.

Exclusive – блок только в этой кэш-памяти, основная память обновлена.

Modified – блок действителен, основная память недействительна, копий блока не существует.

При загрузке процессора все элементы кэш-памяти помечаются как недействительные I. При первом считывании из MM нужная строка вызывается в кэш-память и помечается как Е. Другой процессор (процессор 2) может вызвать ту же строку и поместить ее в кэш, но при отслеживании исходный держатель строки (процессор 1) узнает, что он уже не единственный, и объявляет, что у него есть копия. Обе копии помечаются состоянием S.

Процессор 2 производит запись в строку кэш-памяти в состоянии S и помещает сигнал о недействительности на магистраль, сообщая всем другим процессорам, что нужно отбросить свои копии. Соответствующая строка в процессоре 2 переходит в состояние М.

64

Процессор 3 считывает эту строку. Процессор 2, который в данный момент содержит строку, знает, что копия в MM недействительна, поэтому он передает на магистраль сообщение, чтобы процессор 3 подождал, пока он запишет строку обратно в память. После записи строки вMM процессор 3 вызывает из памяти копию этой строки, и в обоих кэшах строка помечается как S. Затем процессор 2 записывает в эту строку снова, чтоделаетнедействительным копию вкэш-памятипроцессора3.

Процессор 1 записывает слово в эту строку. Процессор 2 видит это и передает на шину сигнал, который сообщает процессору 1, что нужно подождать, пока строка не будет записана в MM. После завершения этого действия процессор помечает собственную копию как недействительную, поскольку он знает, что другой процессор собирается изменить ее. Возникает ситуация, в которой процессор 1 записывает чтолибо в некэшируемую строку. Если применяется политика writeallocate, строка будет загружена в кэш-память и пометится как М. В противном случае строка в кэш-памяти сохранена не будет.

1.3.2.7. Команды поддержки когерентности памяти

Устройства ввода-вывода MPS, работающие по каналу прямого доступа к MM, не содержат кэш-памяти, а следовательно, и рассмотренных выше механизмов поддержки когерентности памяти. Вся ответственность ложится на CPU и реализуется программным путем. Для этой цели в системе команд процессора предусмотреныкоманды flush иinvalidate.

Пусть программа процессора формирует данные для отправки через устройство ввода-вывода, помещая их в кэшируемую область MM

ввиде буфера выходных данных (кэш-память работает в режиме обратной записи). Это означает, что новые данные будут сформированы

вкэши, а не в MM. Устройство же ввода-вывода берет данные из MM. Поэтому перед разрешением на передачу процессор должен переместить подготовленные данные из кэш-памяти в MM, выполнив команду flush. По этой команде данные из кэш-памяти перезаписываются в MM. В команде flush указывается адрес и размер перезаписываемых данных.

Пусть устройство ввода-вывода принимает данные и помещает их во входной буфер MM, минуя процессор. В кэш-памяти процессора могут остаться данные входного буфера от предыдущей обработки, помеченные как действительные. По завершении приема устройство вводавывода информирует процессор о готовности входного буфера. Для работы с этими новыми данными процессор должен объявить недействи-

65

тельными строки кэш-памяти, содержащие старые значения входного буфера. Поэтому процессор выполняет команду invalidate для соответствующих строк кэш-памяти. Команда invalidate объявляет недействительными строки кэш, содержащие данные старого входного буфера. В команде invalidate указывается адрес и размер недействительных данных.

1.4. Магистраль микропроцессорной системы

Каждая микросхема процессора содержит набор выводов, через которые происходит обмен информацией с внешним миром. Эти выводы подразделяются на три типа: адресные, информационные (данные) и управляющие, которые и являются основой трехшинной магистрали микросистемы. Эти выводы называют шиной адреса (AB – Address Bus), шиной данных (DB – Data Bus) и шиной управления (CB – Control Bus). Например, чтобы выбрать команду, CPU помещает на шину адреса адрес команды. Затем формирует сигналы на одной или нескольких линиях шины управления, чтобы сообщить памяти о выполнении операции чтения. В ответ память помещает на шину данных требуемое слово и посылает сигнал о том, что это сделано. Когда CPU получает данный сигнал, он записывает выставленное слово в регистр команд.

Число адресных выводов и число выводов шины данных – два ключевых параметра, определяющих производительность CPU. При наличии m адресных линий можно обратиться к 2*m ячейкам памяти. Обычно m=16, 20, 32, 64. CPU, содержащий n линий шины данных, может считывать или записывать n-битное слово за одну операцию.

Обычно n=8, 16, 32, 64.

Линии шины управления регулируют и синхронизируют поток данных, а также выполняют другие разнообразные функции. Все шины управления содержат линии питания, «земли» и синхронизирующего сигнала. Остальные выводы могут быть разными для разных шин. Тем не менее линии шины управления можно разделить на несколько основных групп:

1)управление шиной;

2)прерывание;

3)арбитраж шины;

4)состояние;

5)разное.

66

1.4.1. Циклы обращения к магистрали

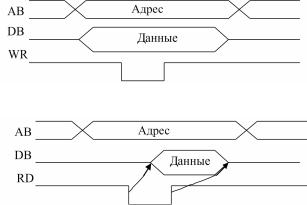

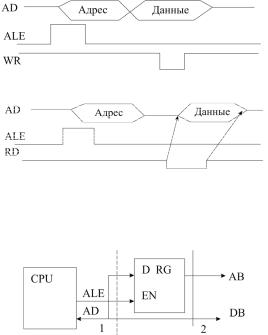

Обмен данными через магистраль выполняется словами или байтами в виде следующих друг за другом обращений. За один цикл обращения к магистрали между CPU, MM и I/O передается от одного до нескольких байт. Существует несколько типовых циклов обмена, среди них чтение памяти и запись в память. В случае архитектуры гарвардского типа, когда память программ и данных физически разделены, вводится также цикл чтения памяти программ. Рассмотрим простую магистраль со следующим набором сигналов управления в манере Intel:

RD (Read) – строб чтения памяти; WR (Write) – строб записи в память; READY – готовность к обмену.

Временные диаграммы передачи данных через магистраль однотипны и имеют вид, представленный на рис. 1.16. На диаграммах выходные данные памяти истинны в момент окончания строба RD, тогда как формируемые CPU выходные данные – в течениедействиясигнала WR.

а

б

Рис. 1.16. Циклы записи (а) и чтения (б) магистрали

В некоторых случаях, например, когда в MPS используются медленно работающие компоненты или некоторые из модулей еще не готовы к обмену по ряду причин, не зависящих от CPU, длительность стробов WR и RD могут оказаться недостаточными для правильного обмена со стороны компонента. Тогда для организации надежного завершения магистральной операции в состав магистрали вводят специальную линию READY.

67

В каждом цикле обращения к магистрали перед окончанием строба RD или WR CPU проверяет линию READY. При подтверждении обмена CPU завершает операцию на магистрали, в противном случае он переходит в состояние ожидания подтверждения, в котором остается до установления сигнала READY (рис. 1.17).

Рис. 1.17. Цикл чтения с подтверждением обмена

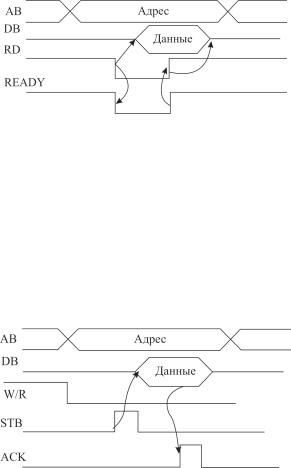

Рассмотрим простую магистраль со следующим набором сигналов управления в манере Motorola:

STB – строб операции на магистрали;

W/R – тип операции запись/чтение;

ACK – подтверждение операции.

На рис. 1.18 приведена временная диаграмма цикла чтения в манере Motorola. По сигналу ACK CPU осуществляет прием данных с шины и завершает цикл магистрали.

Рис. 1.18. Циклы чтения с подтверждением обмена

вманере Motorola

1.4.2.Двухшинная магистраль

ВCPU с целью сокращения ширины магистрали вводят совмещенную шину адреса/данных (AD), по которой передаются как адреса, так

иданные. Этап передачи адресной информации отделен по времени от

68

этапа передачи данных и стробируется специальным сигналом ALE (Address Latch Enable), который включен в состав CB. На рис. 1.19

представлена временная диаграмма работы такой магистрали.

а

б

Рис. 1.19. Циклы записи (а) и чтения (б) двухшинной магистрали

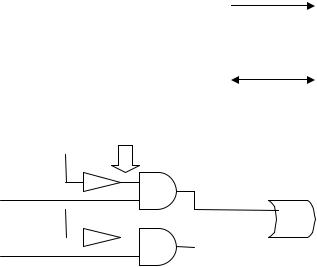

Рис. 1.20. Преобразование двухшинной (1) и трехшинной (2) магистрали

Каждый модуль с двухшинной магистралью содержит локальный адресный регистр для запоминания адресной информации по сигналу ALE. Для фиксации адресной информации может быть использован и один общий регистр, в результате MPS с двумя шинами преобразуется в MPS с тремя шинами, как показано на рис. 1.20.

1.5. Контроллеры прерываний, устройств и интерфейсов устройств ввода-вывода

1.5.1. Контроллер прерываний [1]

Процессору необходима способность взаимодействовать с окружением через набор устройств ввода-вывода. Эти устройства обычно требуют быстрой реакции процессора для обслуживания событий реально-

69

го мира. Прерывания обеспечивают этот механизм и исключают для процессора необходимость постоянно опрашивать (polling) устройства для обнаружения их внимания к себе. Очень часто имеется множество источников прерывания на некоторой данной платформе, поэтому необходим контроллер. Контроллер прерываний – компонент, который собирает все аппаратные события от SoC и платформы и предоставляет их процессору. На этом фундаментальном уровне контроллер прерываний передает события процессорному ядру для обработки. Контроллер прерываний способствует идентификации события вызвавшего прерывания, так что механизм обработки исключения (exception) процессора может передать управление подходящей функции обработки. На рис. 1.21 приведена упрощенная возможная структура контроллера прерываний.

|

Линия |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Контроллер прерываний |

|

|

|

|

||||||||

|

прерывания |

|

|

|

|

|

|

|

|||||||

|

А |

|

Регистр статуса прерываний |

|

|

Линия |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

В |

|

А |

|

прерывания |

|

|

|

|

|

|

|

|

|

|

|

|

|

процессора |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

Регистр масок прерываний |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Линия |

|

|

|

|

|

|

|

В |

|

А |

|

Запись/ |

Процессор |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

прерывания |

|

|

|

|

|

|

|

|

|

|

|

Чтение |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

В |

|

|

Регистр отложенных прерываний |

регистров |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

прерывания А |

|

|

|

|

|

|

|

|

|

|

|

В |

|

А |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

Маска[0] |

|

|

|

|

|

||||||||

Прерывание А |

Отложенное [0] |

|

Статус [0] |

Линия |

|||||||||||

|

|

|

прерывания |

||||||||||||

|

Маска [1] |

|

Статус [1] |

процессора |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Прерывание В |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Отложенное [1] |

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|||||||||

Рис. 1.21. Структура контроллера прерываний

Контроллер прерываний содержит три регистра, которые может читать и записывать процессор. Регистры содержат битовые поля с одиночными битами, выделенными для каждого источника прерывания. Регистр статуса прерываний отражает текущее состояние входящих линий прерываний. Он устанавливается в 1, когда запрос прерывания ак-

70